2.1 Verilog HDL语言要素

2.1.1空白符:

空白符包括空格符(lb)、制表符(\t )、换行符和换页符。在编译和综合时,空白符被忽略。

例: initial begin a=3'b100;b=3'b010;end

相对于

initial

begin

a=3'b100;

b=3'b010;

end

2.1.2 注释符

(1)单行注释:以“//”开始,Verilog HDL忽略从此处到行尾的内容。

(2) 多行注释:多行注释以" /* "开始,到 " */ "结束,Verilog HDL忽略其中的注释内容。

2.1.3标识符和转义标示符

在Verilog HDL中标识符( ldentifier)被用来命名信号名、模块名、参数名等,它可以是任意一组字母、数字、$符号和_(下划线)符号的组合。应该注意的是标识符的字母区分大小写,并且第一个字符必须是字母或者下划线。

Verilog HDL规定了转义标识符(Escaped ldentifier)。采用转义标识符可以在一条标识符中包含任何可打印字符,转义标识符以"(反斜线)符号开头,以空白结尾(空白可以是一个空格、一个制表字符或换行符)。

2.1.4 关键字

语言内部已经使用的词,语言内部的专用词,是事先定义好的确认符,PS:所有关键字都是小写的。

2.1.5 数值

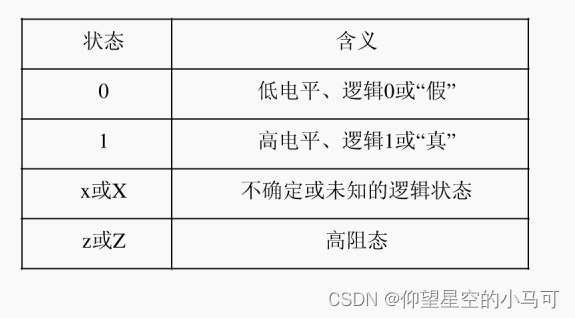

(1)四种基本的逻辑数值状态

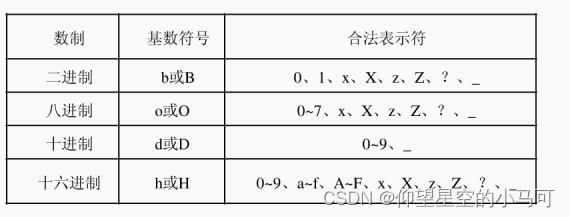

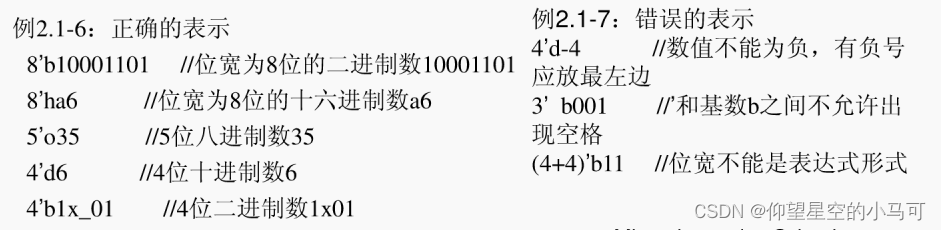

(2)整数及其表示

(3)实数及其表示

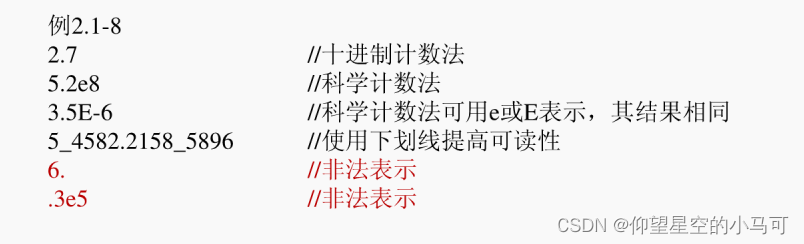

(3)实数及其表示

( 1)十进制表示法,采用十进制格式,小数点两边必须都有数字,否则为非法的表示形式。例如:3.0,4.54,0.2等等都是正确的,而5.就是错误扯,因为小数点两侧都必须要有数字。

(2)科学计数法。例如:564.2e2的值为56420.0,8.7E2的值为870.0(e不分大小写),3E-3的值为0.003。

2.2 数据类型

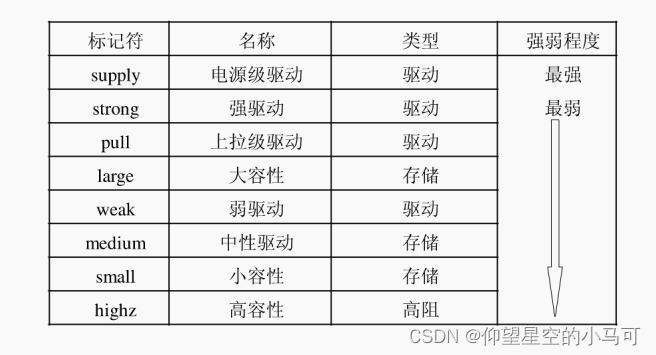

物理数据类型:连线型、寄存器型和存储器型数据类型;信号强度表示数字电路中不同强度的驱动源,用来解决不同驱动强度存在下的赋值冲突

2.2.1 物理数据类型

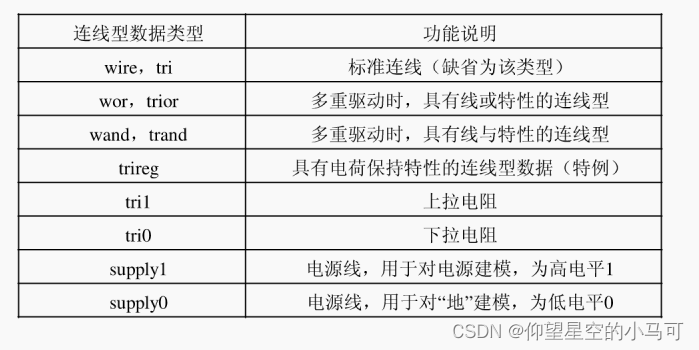

1. 连线型

1)wire 和 tri

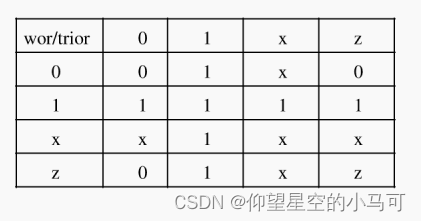

2)wor 和 trior

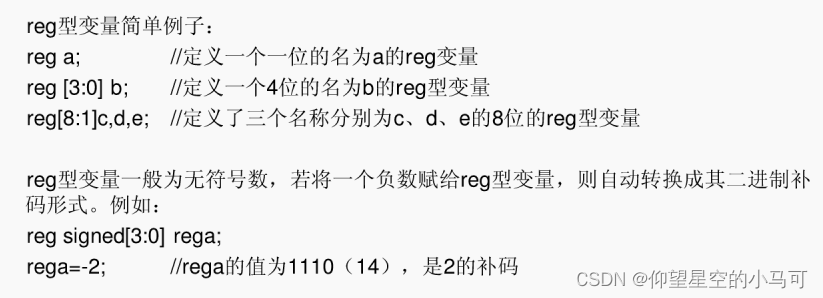

2.寄存器型:

reg型是数据储存单元的抽象类型,其对应的硬件电路元件具有状态保持作用,能够存储数据,如触发器、锁存器等。

reg型变量常用于行为级描述,由过程赋值语句对其进行赋值。

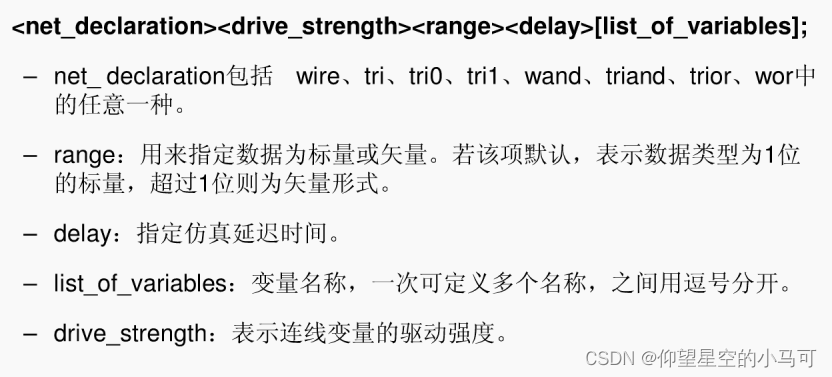

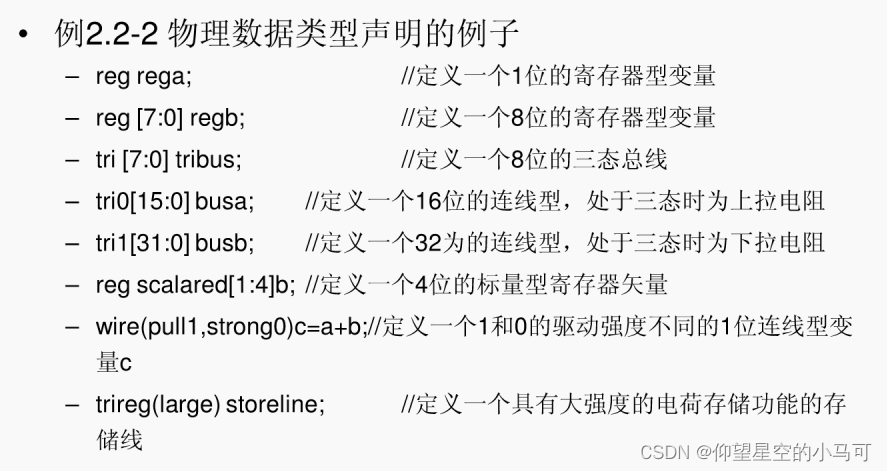

2.2.2 连线型和reg型数据类型的声明

1. 连线型数据类型的声明

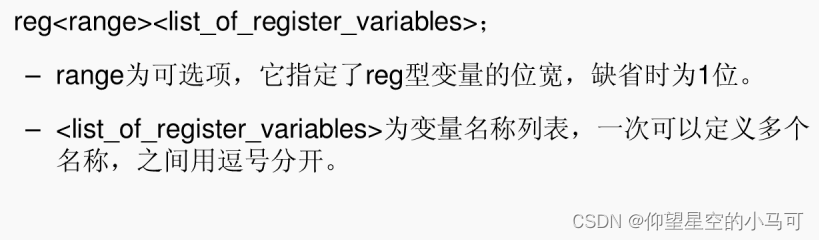

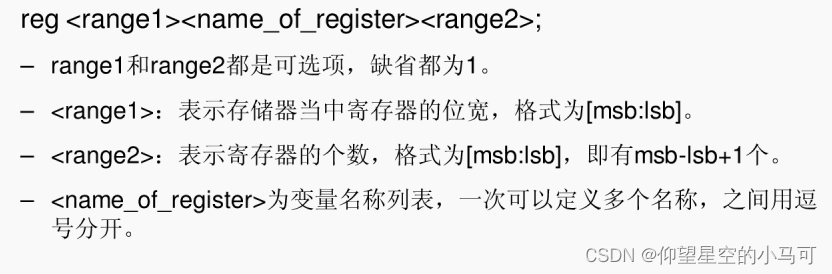

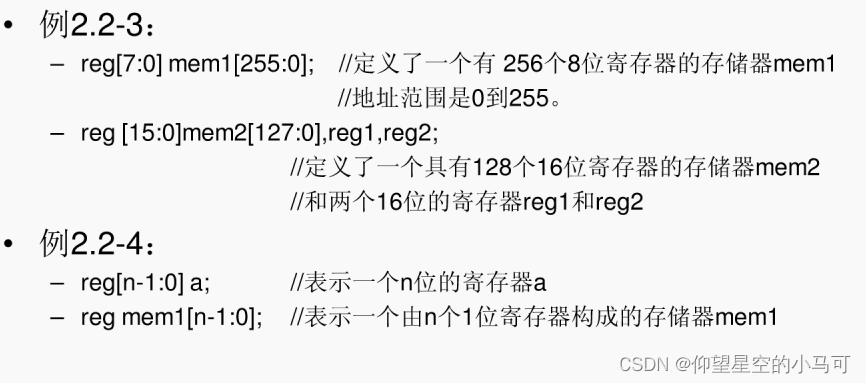

2. 寄存器型数据类型的声明

2.2.3 存储器型

1. 抽象数据类型

主要包括整型( integer) 、时间型( time)、实型(real)及参数型(parameter) 。

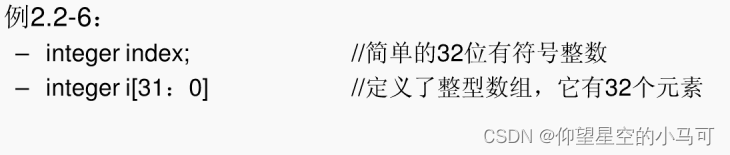

2.整型

**integer<list_of_register_variables>;**

3.时间型

(1)时间型数据与整型数据相类似,只是它是64位的无符号数。时间型数据主要用于对模拟时间的存储与计算处理,常与系统函数$time一起使用。

(2)时间型数据的声明格式为:

time<list_of_register_variables>;

例如: time a,b;ll定义了两个64位的时间型变量

4.实型:

型数据在机器码表示法中是浮点型数值,可用于对延迟时间的计算。

(1)实型数据的声明格式如下:

real<list_of_variables>;

例如:real stime; 定义了一个实数型数据

5.参数型(parameter) :

属于常量,在仿真开始之前就被赋值,在仿真过程中保持不变,以提高程序的可读性和维护性。

(1)参数类型的定义格式为:

parameter参数名1=表达式1,参数名2=表达式2,…,参数名n=表达式n;

例2.2-7:

parameter length=32,weight=16;

parameter Pl=3.14,LOAD=4’b1101;

parameter DELAY=(BYTE+BIT)/2;

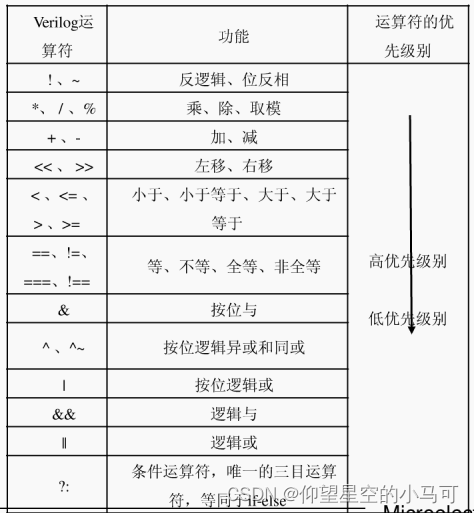

2.3 运算符和表达式

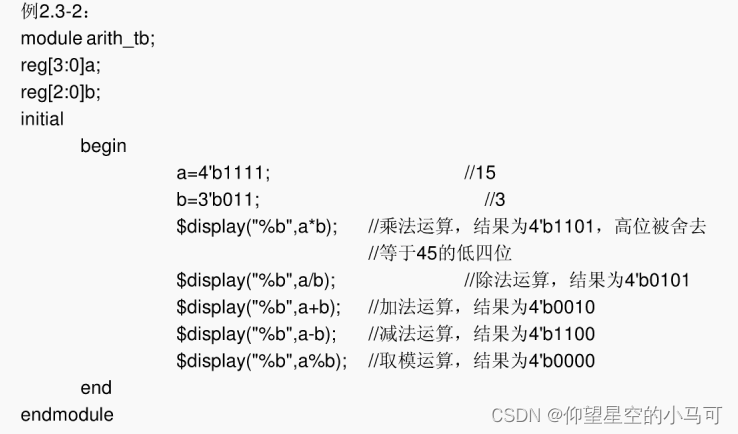

2.3.1 算术操作符(加,减,乘,除,取模)

1.算术操作结果的位宽

算术表达式结果的长度由最长的操作数决定。在赋值语句下,算术操作结果的长度由操作左端目标长度决定。

例2.3-1:

reg[3:0]A,B,C;

reg[5:0]D;

A=B+C; //4位

D=B+C; //6位

2.有符号数和无符号数的使用

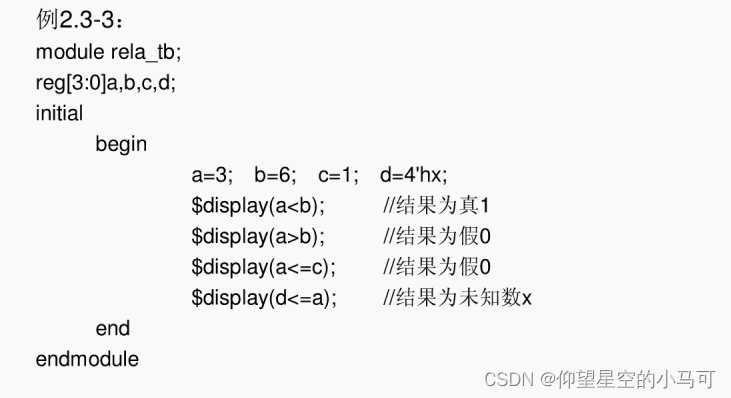

2.3.2 关系操作符

1.大于“>”、小于“<”、大于等于“>=”和小于等于“<=”。

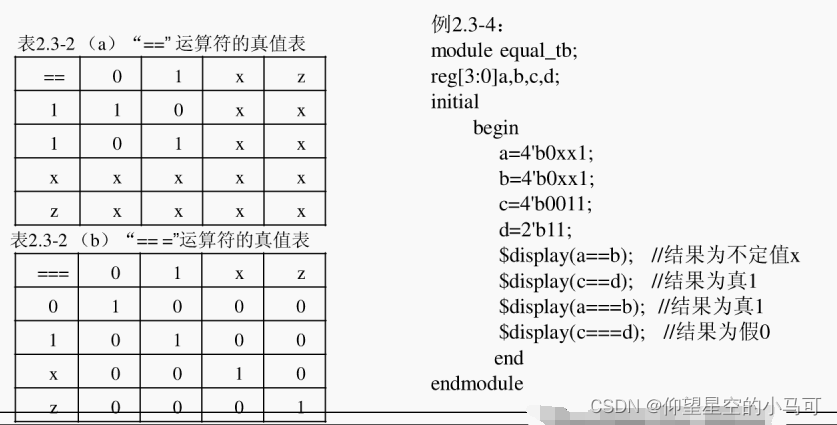

2. 等于“ == ”、不等于“!=”、全等“-= =”、非全等“!==”

3.比较的结果有三种,即真“1”、假“0"和不定值“x”

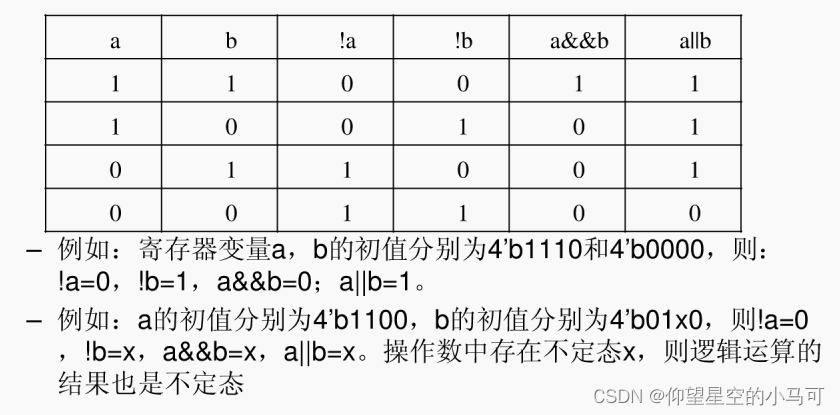

2.3.4 逻辑运算符

逻辑与运算符“&&”、逻辑或运算符“I”、逻辑非运算符“!”

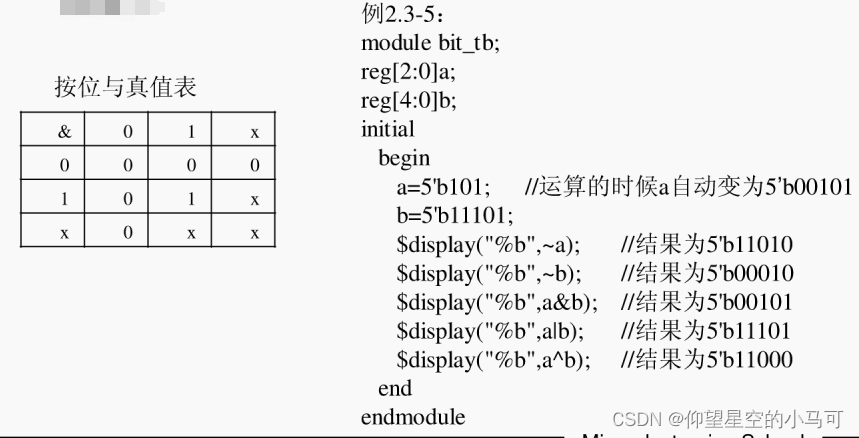

2.3.5 按位运算符

按位取反“~ ”、按位与“&”、按位或I”、按位异或、按位同或~

例2.3-5:

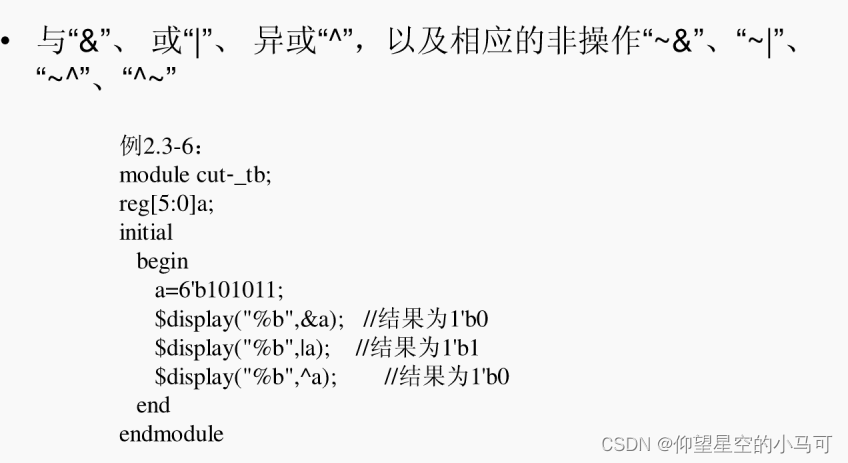

2.3.6 归约运算符(缩位运算符)

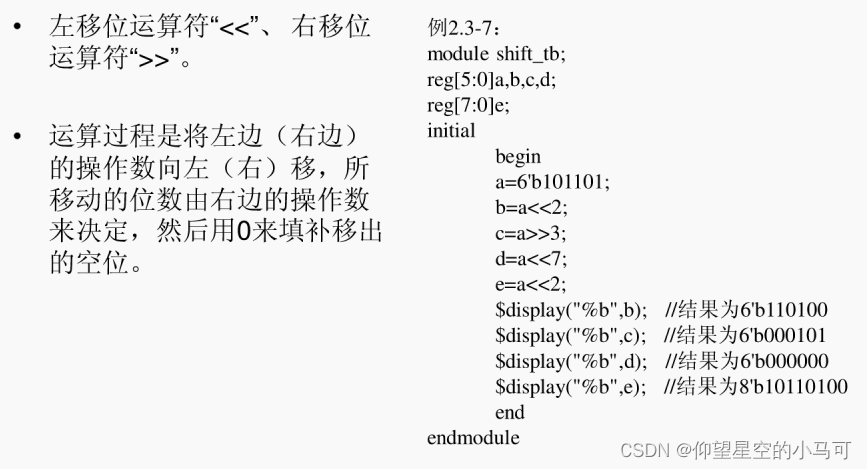

2.3.7 移位操作符

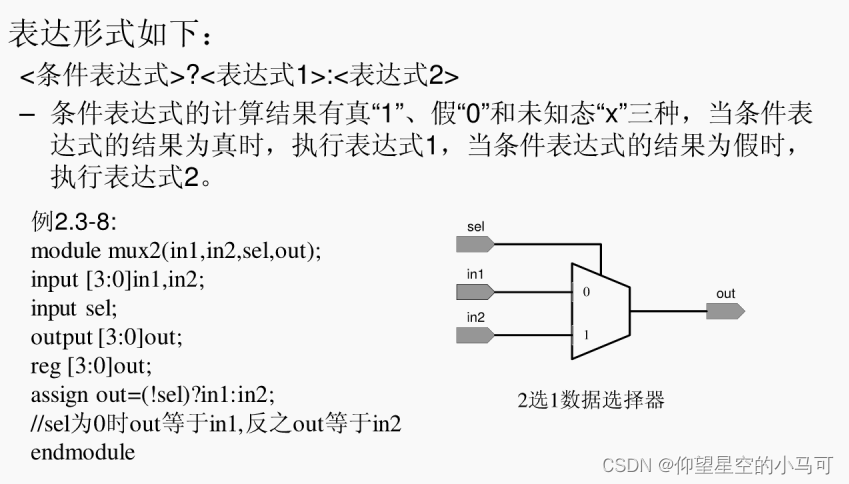

2.3.8 条件运算符

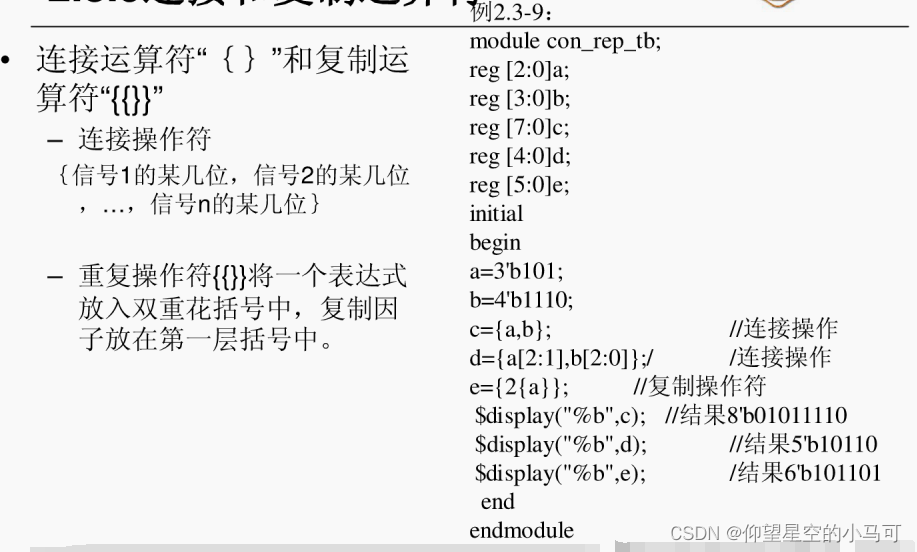

2.3.9 连接和复制运算符

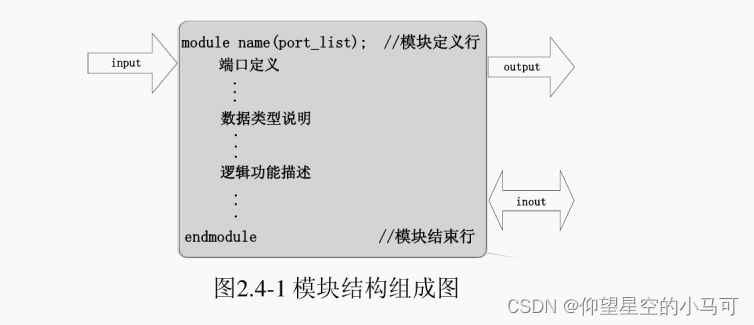

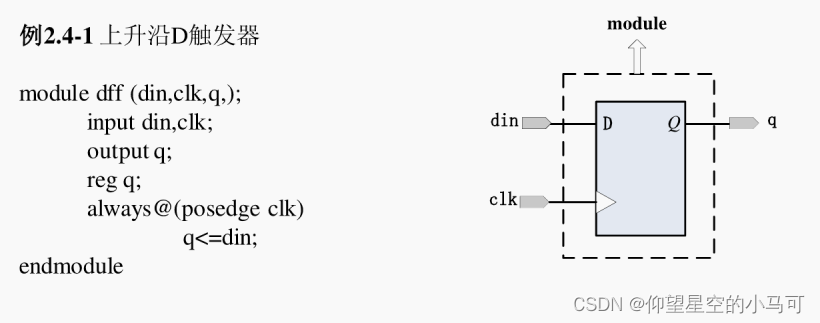

2.4 模块的基本概念

2.4.1 模块的基本概念

模块( module)是Verilog HDL语言的基本单元,它代表一个基本的功能块,用于描述某个设计的功能或结构以及与其它模块通信的外部端口。

一个模块主要包括:模块的开始与结束、模块端口定义、模块数据类型说明和模块逻辑功能描述这几个基本部分。

- (1)模块的开始与结束:以关键词module开始,以关键词endmodule结

束的一段程序,其中模块开始语句必须要以分号结束。 - (2)端口定义:用来定义端口列表里的变量哪些是输入(input)、输出

( output)和双向端口( inout)以及位宽的说明。 - (3)数据类型说明:数据类型在语言上包括wire、reg、memory和

parameter等类型,用来说明模块中所用到的内部信号、调用模块等的声明语句和功能定义语句。 - (4)逻辑功能描述:用来产生各种逻辑(主要是组合逻辑和时序逻辑)

。主要包括以下部分:initial语句、always语句、其它子模块实例化语句、门实例化语句、用户自定义原语(UDP)实例化语句、连续赋值语句( assign) 、函数( function)和任务( task) 。

2.4.2 端口

1.端口的定义

一模块的端口可以是输入端口 (input)、输出端口 ( output)或双向端口( inout) 。

2.模块引用时端口的对应方式

- (1)在引用时,严格按照模块定义的端口顺序来连接,不用标明源模块定义时规定的端口名。格式如下:模块名(连接端口1信号名,连接端口2信号名. … ) ;

- (2)在引用时用“.”标明源模块定义时规定的端口名。格式如下:模块名(.端口1名(连接信号1名),.端口2名(连接信号2名). . . ) ;一这样表示的好处在于可以用端口名与被引用模块的端口对应,不必严格按端口顺序对应,提高了程序的可读性和可移植性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?