资料来源于瑞芯微电子

晶振布线:

在设计印刷电路板时:保持晶体尽可能靠近可编程芯片晶体引脚,保持走线长度短和小,以减少电容器负载和防止不必要的噪音辐射。 将所有信号从晶体和X1和X2引脚下面走线应避免在此区域中,以防止噪声耦合。在顶层周围放置一个保护环,并将环绑在相邻的地面上层通过,以帮助隔离晶体与不必要的噪音耦合。第二层是一个完整的地面层,没有任何分裂的平面。它有助于保护辐射干扰到其他层板上的走线。

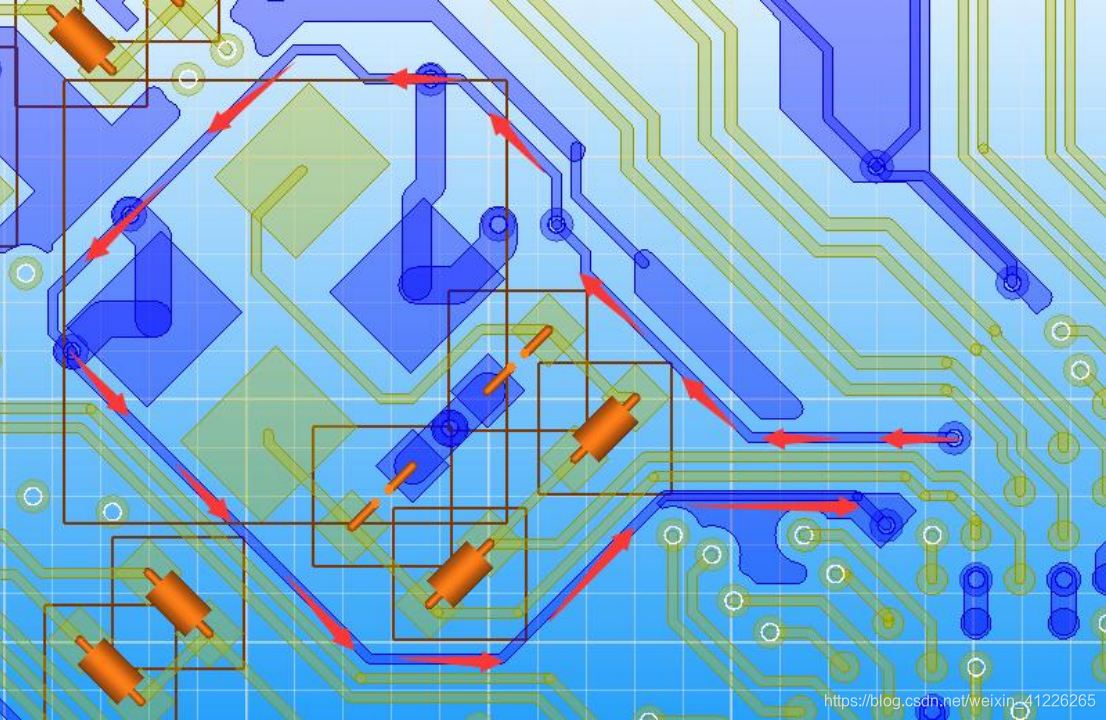

信号靠近:

差分对信号通常区分两种不同的长度匹配要求。第一个要求是最大的对内偏斜。这是最大允许长度不同 对的正负信号之间的关系。如第5节所述,不仅要匹配总体长度,还要匹配信号一段内的长度。 竖起来了。正负信号分量同步传播是很重要的…只有当这些信号是同步的,它们的场就会得到补偿,电磁辐射就会产生 Diation被减少了。

第二个长度匹配要求是时钟和信号对之间或同一接口的不同对之间的最大允许倾斜。一些接口(例如。PCIe、EDP、DP和 正在从数据信号中恢复时钟信号。因此,时钟和数据信号之间的匹配可以相当宽松。不要试图过度匹配这样的接口,因为它是 真的不需要,额外的弯曲只是引入了其他信号质量问题。另一方面,有些接口没有嵌入式时钟信号(例如。米皮界面)… 请非常小心地路由这些信号。需要满足时钟和数据信号之间的长度匹配

有关高速信号之间所需最小距离的信息可在第6节中找到…为了尽量减少跟踪之间的串扰,需要一个最小的距离。十字架的等级 谈话取决于两条走线之间的距离和它们被紧密路由的长度。有时,瓶颈可能迫使路径的路径比通常允许的更近。试试看 最大限度地减少这些区域,并扩大瓶颈之外的信号之间的距离。如果有空位,尽量扩大高速信号之间的距离 -速度和低速信号)即使已满足最低的轨迹分离要求

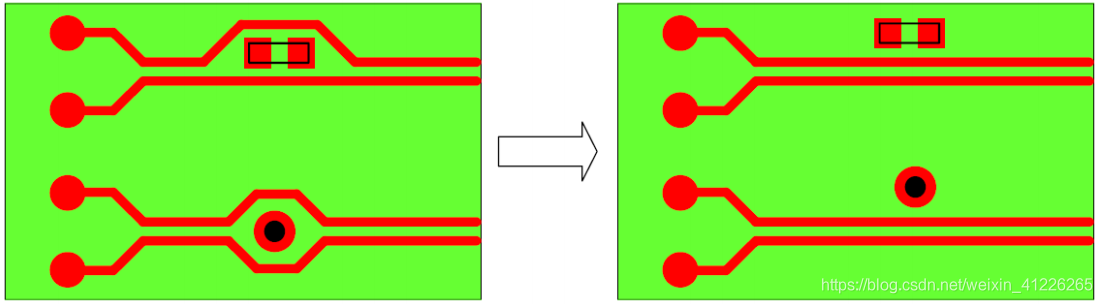

两点器件的连接:

长的存根痕迹可以作为天线,因此增加了符合EMC标准的问题。存根痕迹也会产生反射,对信号的完整性产生负面影响。共同来源 对于存根,在高速信号上是拉起或拉下电阻…如果需要这样的电阻,将信号路由为雏菊链。

作为经验法则,大于波长十分之一的存根应该被认为是有问题的。下面的示例显示对Gen3PCIe信号的计算:

Vias也可以充当存根。例如,在六层板中,当信号通过使用VIA从第1层更改为第3层时,VIA将创建一个到达第6层的存根。依次反钻通孔 避免这样的存根是一种相当昂贵的技术,也是大多数PCB制造商不支持的技术。唯一的实际解决方案是减少高速痕迹中的通孔数量…

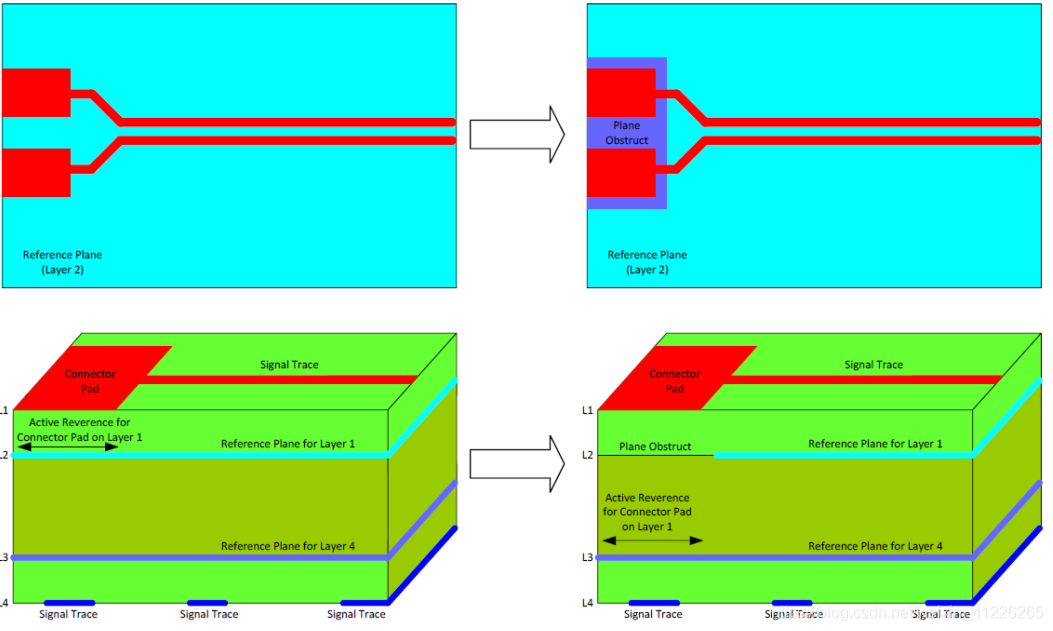

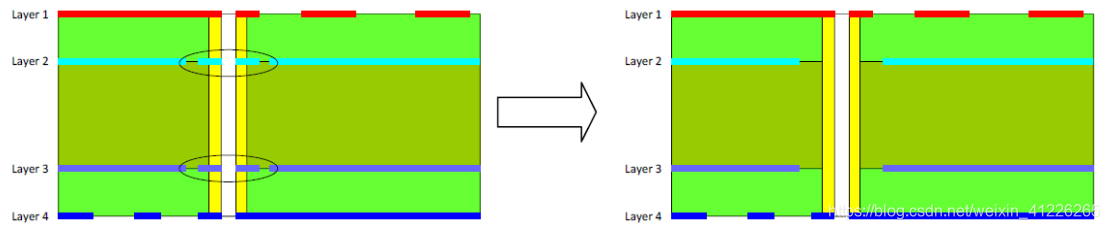

去掉连接器底下地平面:

走线的阻抗取决于它的宽度和轨迹与参考平面之间的距离。一个宽的走线比一个具有相同距离的薄的走线具有更低的阻抗。同样的效果也存在于连接器和组件垫。一个大的焊盘的阻抗明显低于连接到焊盘的走线。这种阻抗不连续性会导致反射减少信号不连续。因此,在大连接器和组件垫下,应该放置一个平面障碍物,平面的面积应该通过模拟来决定。在这种情况下,主动参考平面将放置在另一层。这个参考平面的网络应该与正常参考平面相同。这个参考平面需要用通孔缝合到正常参考平面上

过孔是阻抗不连续的另一个来源。为了最大限度地减少影响,应移除内部层中未使用的通孔垫。这可以在CAD工具中的设计工具设置或通过 PCB制造商提出要求

差分对信号:

不允许在差分对之间放置任何组件或通道,即使信号是对称路由的。组件和对之间的通道可能导致EMC辐射造成阻抗不连续

一些差分对高速信号需要串行耦合电容器,对称地放置这样的电容器。电容器和焊盘产生阻抗不连续。0201封装的电容和0402封装的电容是可以接受的。不要放置较大的封装,如0603或0805等

通过引入阻抗的巨大不连续性。尽量将放置孔的数量减少到最小,并对称地放置过孔

为了满足差分对的阻抗要求,两个信号轨迹都需要在同一层上走线。在换层布线中加入同样数量的孔

长度匹配:

高速接口对到达时间有额外的要求,在不同的走线方式会对信号对之间有所影响。例如,在高速并行总线中,所有数据信号都需要在一个时间段内到达,以满足接收机的设置和保持时间要求。载波板设计器需要确保这种允许的倾斜不被超过。因此为了满足这一要求,需要进行长度匹配。通常会给出最大的时间偏差的要求

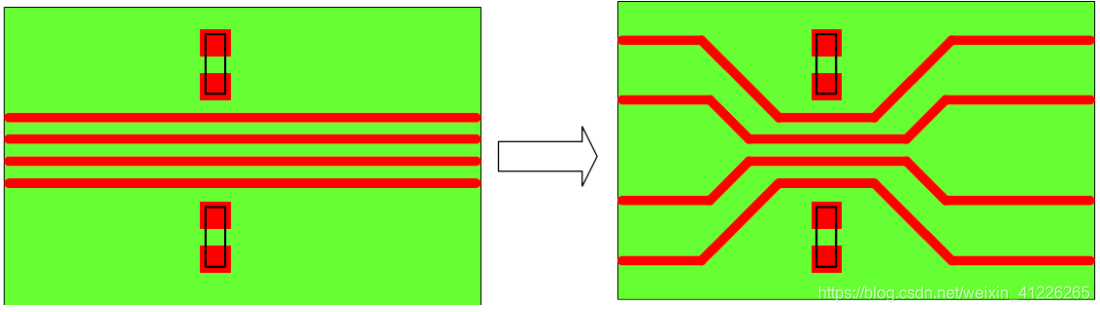

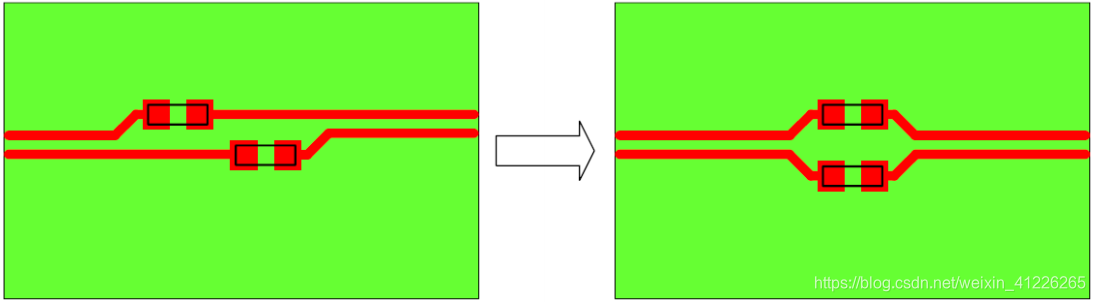

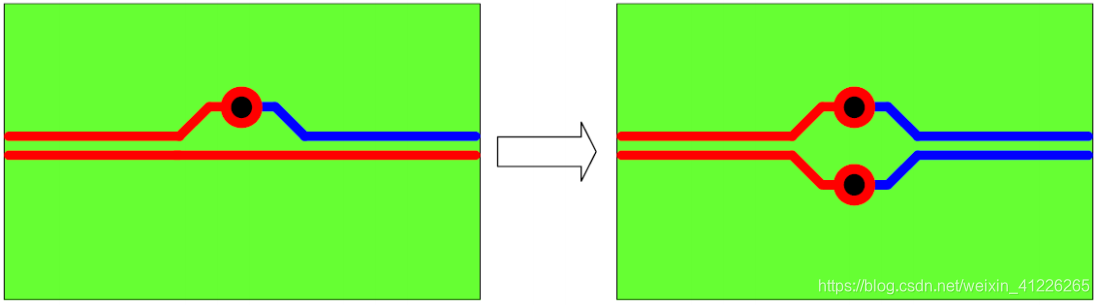

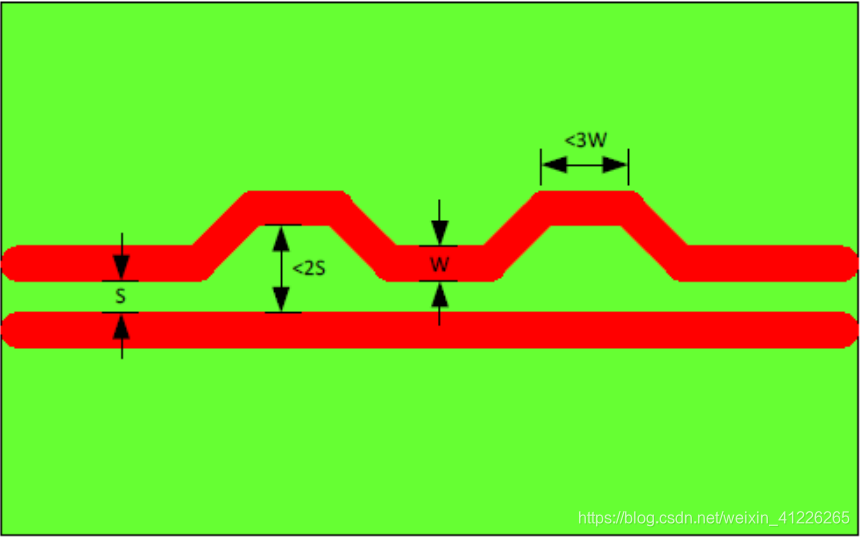

差分对信号往往需要一个非常紧密的延迟倾斜之间的正负信号轨迹。因此,长度差异需要补偿使用蛇形走线。为了减少阻抗不连续性,需要仔细选择蛇形走线轨迹的几何形状。下图为理想蛇纹石痕迹的要求:

下面是讲解有关蛇形走线所注意的那几个点:

校正长度的蛇形走线放置错误匹配点,正确的应放置在长度不匹配的原点。这样可以确保正负信号分量的真确性

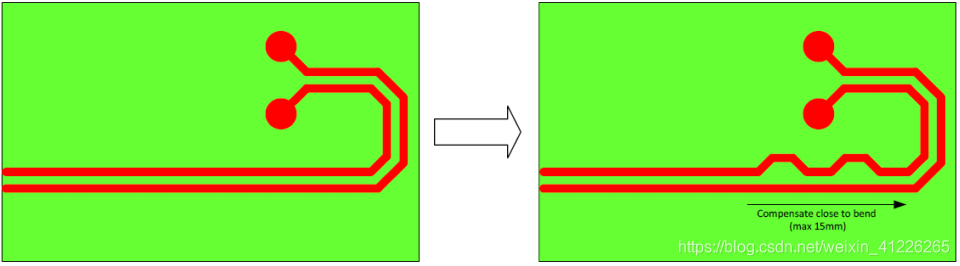

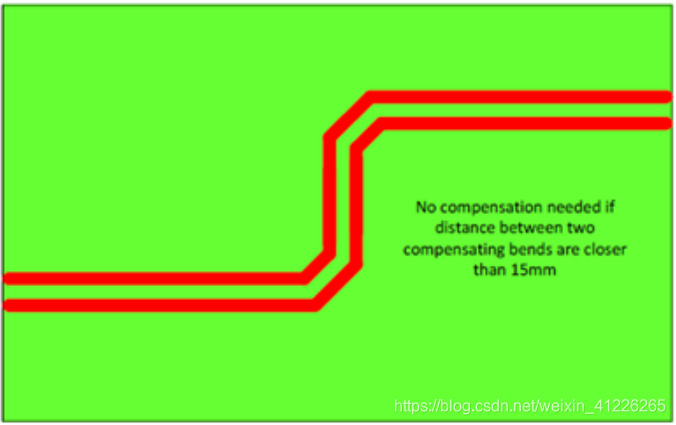

弯曲是长度不匹配的一个常见来源。补偿应靠近弯道,最大距离为15mm放置

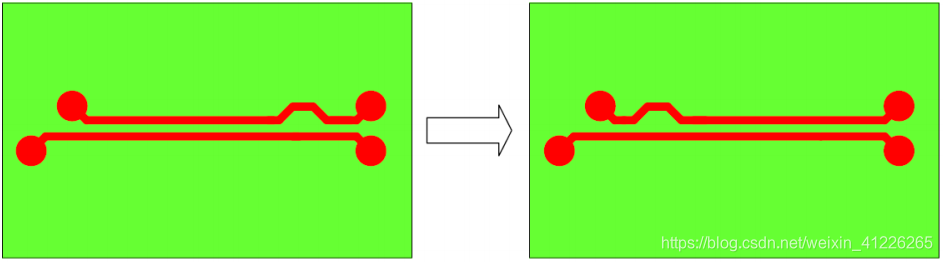

往往两个弯道相互补偿,如果弯曲小于15毫米,则不需要额外的蛇形补偿。

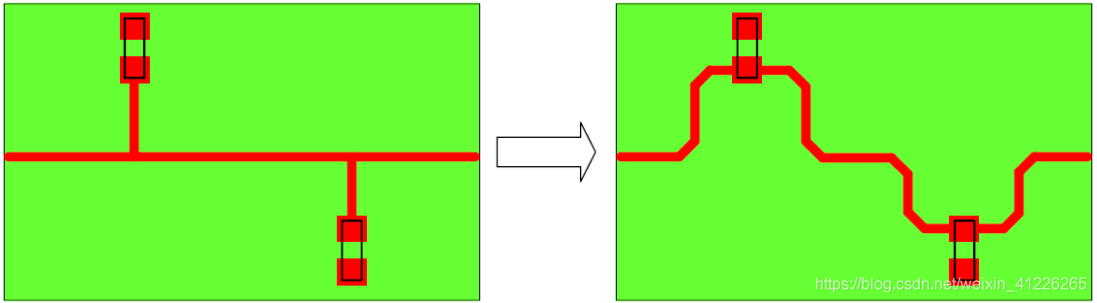

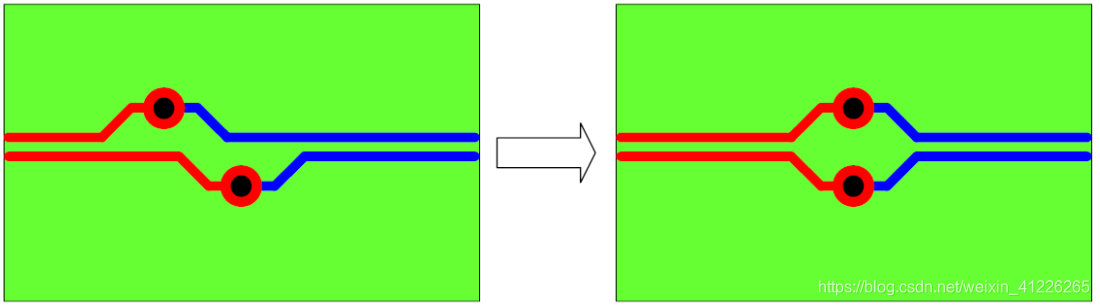

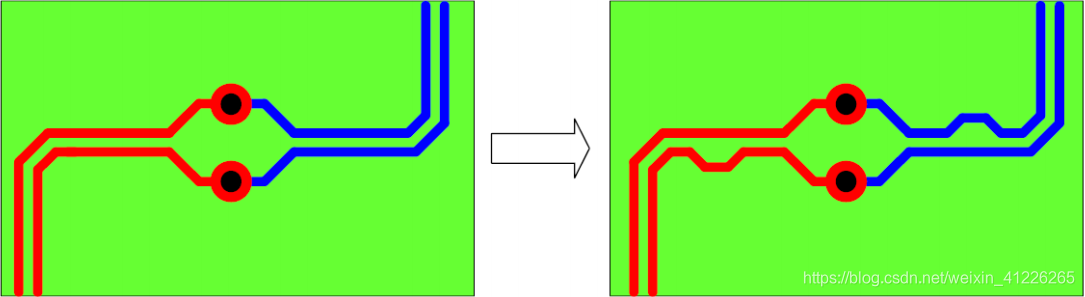

差分对连接的每个段都需要单独匹配。连接可以由连接器、串行耦合电容器或通孔分割。下面图中的两个弯曲 我们会互相补偿。由于通孔将微分对分成两段,需要单独补偿弯曲。这确保了正反两方面的信号 通过通孔同步传播。违反此规则可能需要手动检查,因为DRC可能只检查整个连接的长度差异。

差分对连接的每个段都需要单独匹配。连接可以由连接器、串行耦合电容器或通孔分割。下面图中的两个弯曲 我们会互相补偿。由于通孔将微分对分成两段,需要单独补偿弯曲。这确保了正反两方面的信号

不同层的信号速度不相等。由于差异很难估计,所以如果需要匹配,则最好在同一层上路由信号。例如,复员方案 播放接口需要信号对和时钟对之间的紧密匹配。最好是在同一层上路由DDR3信道的所有数据和时钟信号。

156

156

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?