在上一期jaya小编给大家带来了一款由知名FPGA 开发板厂商黑金出产的,国产FPGA紫光同创PGL12G开发板的硬件部分,在上一期给大家简单的介绍了一下,有兴趣的盆友,可以移步上期硬件部分的测评,这期的测评主要将会对紫光同创的这颗PGL12G进行环境的搭建和Verilog程序例程的综合等等。

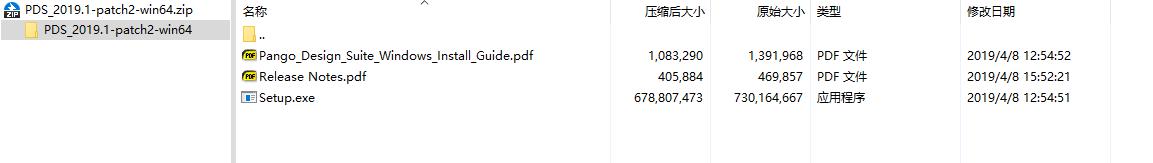

OK开始进入正题,作为一款国产的FPGA,肯定是有一个套新的环境,像是Xilinx的开发环境Vivado或者老一些的芯片都是用ISE的,像是Intel的FPGA环境一般Quartus。我们的这颗来自紫光同创的国产FPGA所应用的开环境是Pango Design Suite。当你获取了开发板,自然界就会拿到,板卡对应的环境安装包,如下图。

按照找手册,我们打开Setup.exe进行安装,不过既然提供的exe安装包文件,估计我拿到的软件是只能在Windows 下进行使用,像是Vivado的话是可以在linux下进行安装的,听说linux下的运行效率更好,同样的硬件配置综合工程速度更快。不过小编也没做过那么大的FPGA的工程需要综合,需要提速到Linux版本的,Windows版本基本已经可以满足小编的需求了。OK,这样我们就开始安装,安装的过程大家都懂得,下一步到天黑就好了。

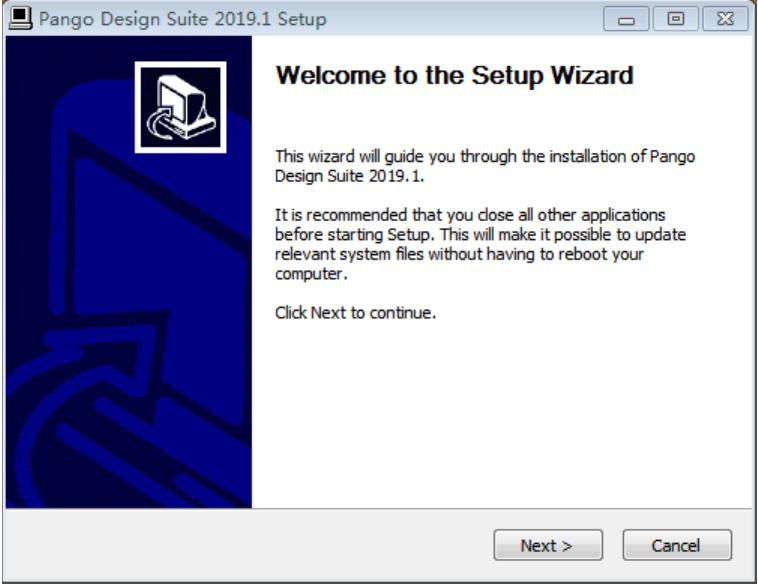

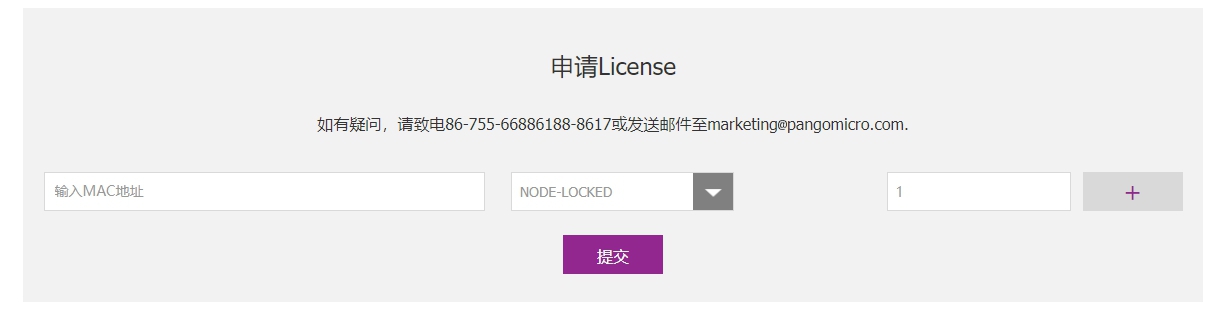

然后,小编就遇到了第一个难点,是关于License 配置的问题,License是需要申请的,要得到一个绑定MAC地址的的License文件。License文件有两种Node-locked License(单机版)和Floating License(服务器版)两种,我们个人来用呢,就是用Node-locked License就可以了。

申请的方法,就是在网页申请,网页连接如下:https://www.pangomicro.com/support/License/index.html

填好申请的需求后,可能需要联系一下官方,小编也不确定是因为节假日期间申请被忽略了还是什么其他的原因,小编的申请提交后就石沉大海了,后面通过和官方沟通才拿到Node-locked License。关于MAC地址的填写,请注意使用你默认上网网卡的MAC地址,否则可能使用起来会有问题。比如你经常用无线网卡来连接网络,那么就要填写你的无线网卡的MAC地址。官方会提供我们一个*.lic的文件,启动软件的时候填写下*.lic文件的目录就可以正常打开软件了。(小编这边已经填过一次了,这个填写*.lic地方的显示略有不同)

相应的license配置好,软件才能正常工作, Pango Design Suite 需要 PDS License文件,同时还有另外一个License,是软件内置的Synplify 综合工具,这个综合工具也需要相应的 OEM License 文件。 两个License配置好了我们的软件也就能正常的工作了。

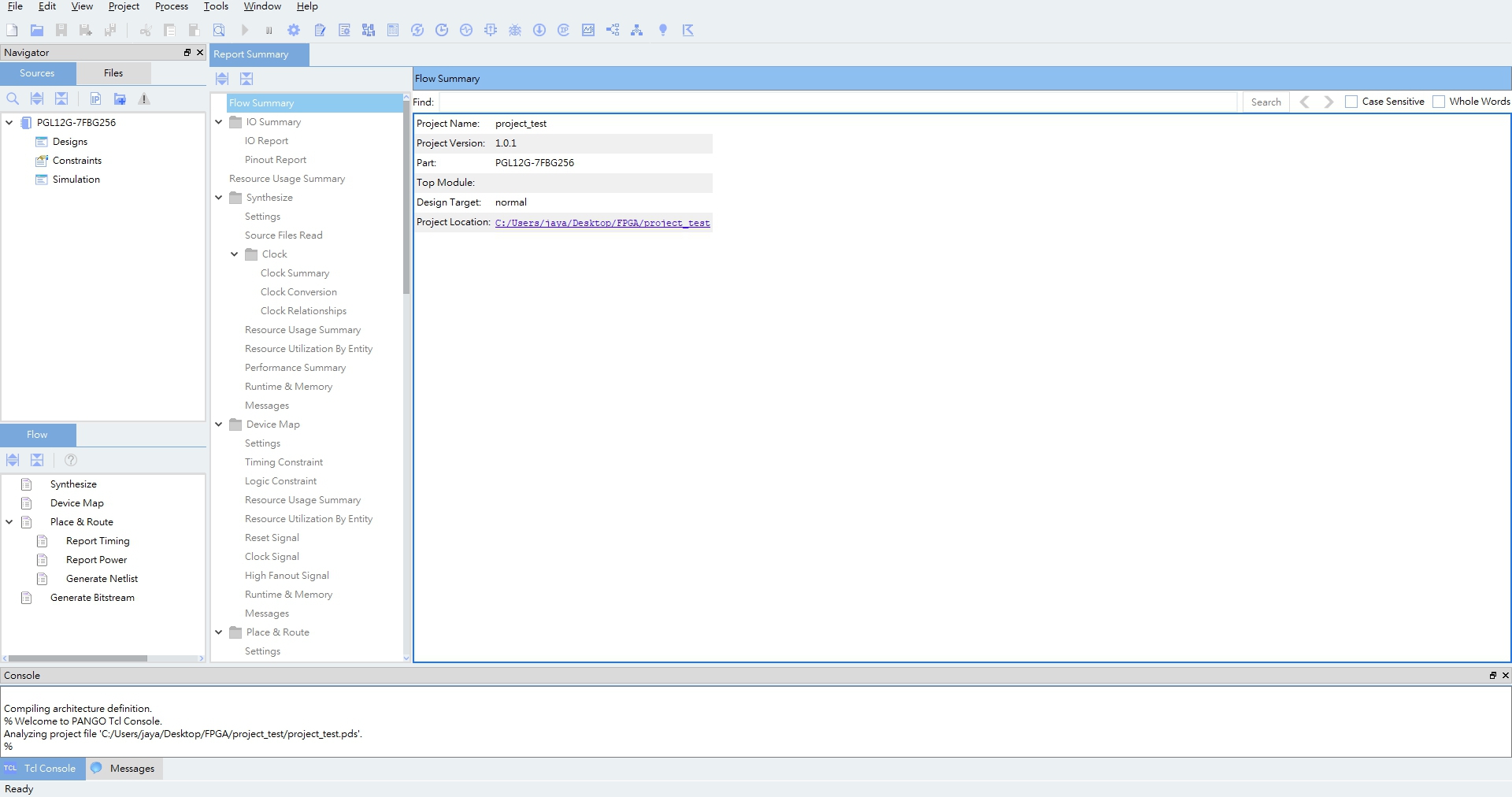

打开软件环境的界面如下图。相对比来说还是比较简洁明了,我们来建立一个project来看看。

创建project的第一个见面先给我们一个简介,告诉我们在创建工程的时候都需要提供什么信息。我们直接Next就好。

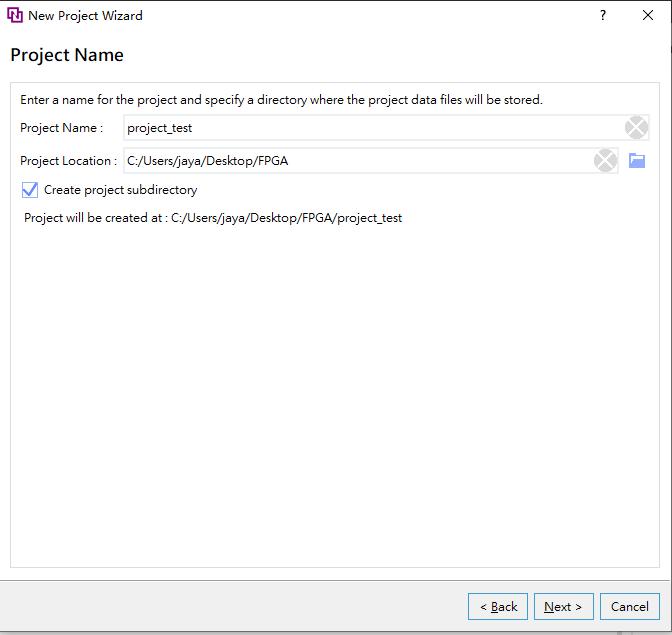

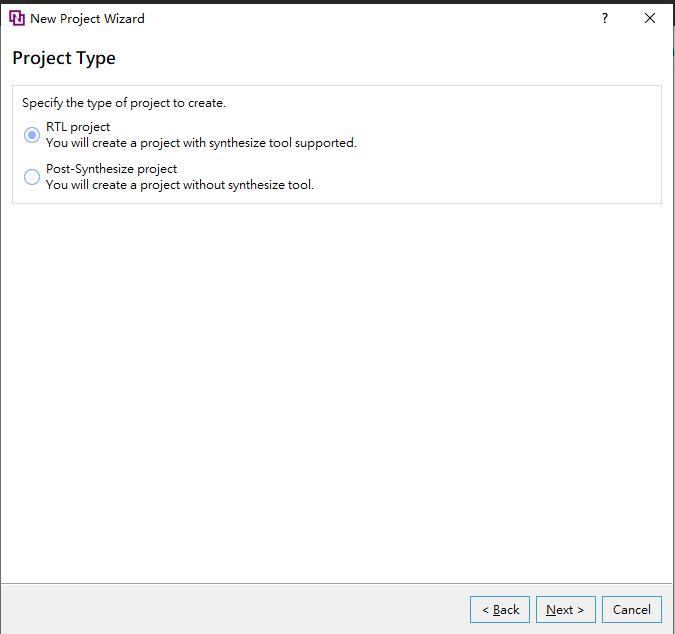

然后呢我们要添加Project的Name 根据自己的需求填写就好,Project Type,我们选择RTLProject。

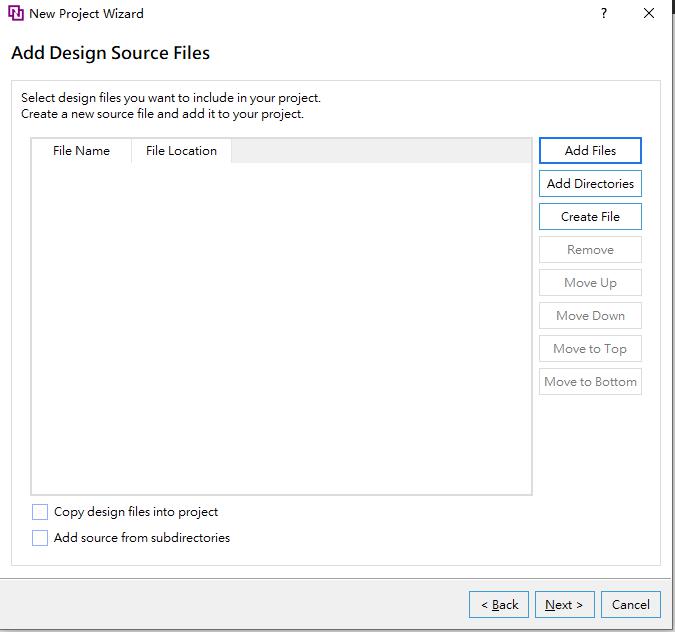

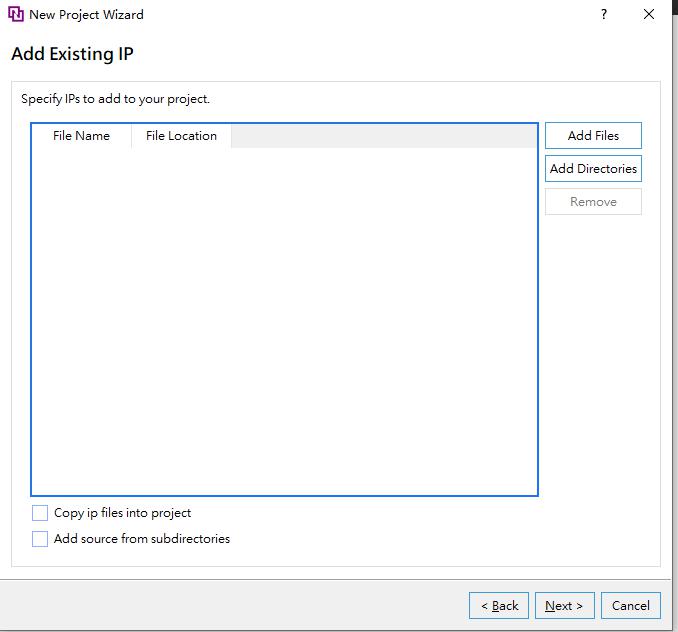

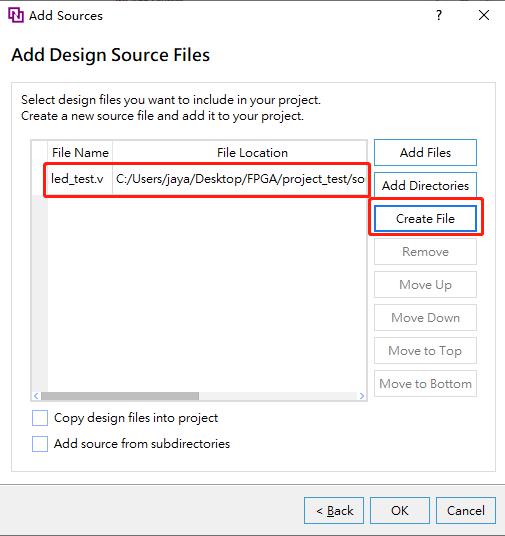

然后我们要添加Design Source Files,这里呢我们直接创建一个空工程,不添加任何文件。然后是IP部分的选择,Add Existing IP,我们也不会使用到IP,所以直接下一步。

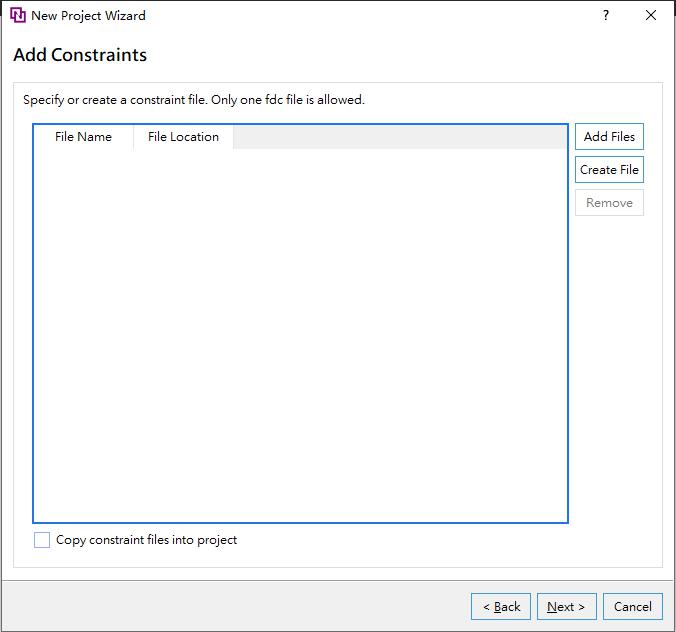

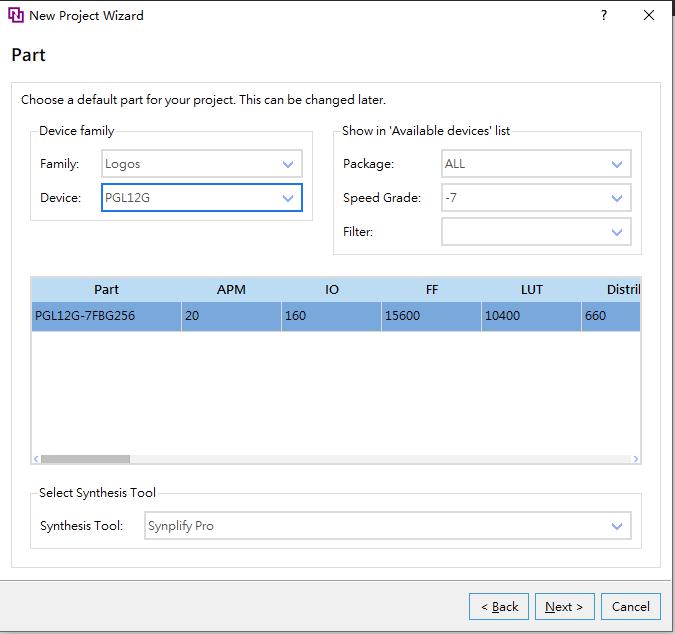

在之后是让我们来添加约束文件。Add Constraints,一样的,我们现在也没有要添加的约束文件。Part部分这里就是选择我们使用的器件,PGL12G 开发板首先在Family栏里选择Logos系列,Device中选择PGL12G,在 Package栏选择 BG324 ,Speed grade 栏选择-7,这样我们就选中了我们需要的芯片型号。单击NEXT进入下一界面。

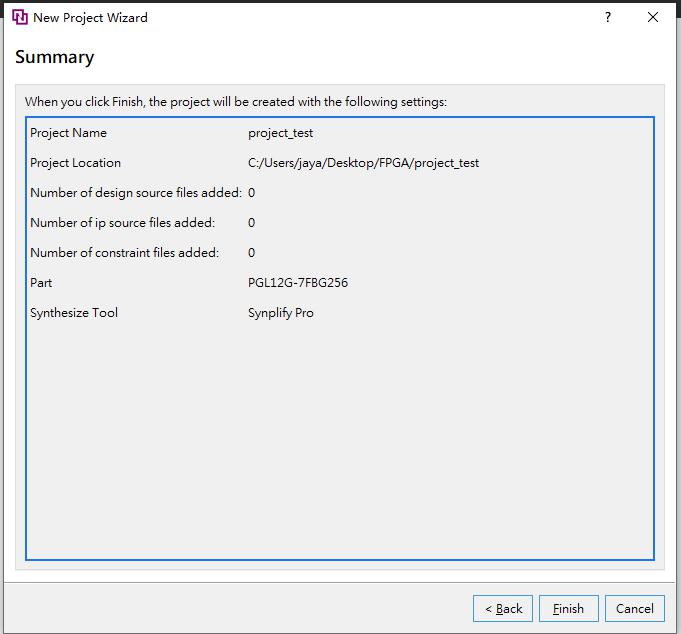

OK我们的项目配置已经完成,仔细检查一下我们需要的配置是正确的,没有问题我们Finish。完成我项目的创建。

这是我们终于进入到FPGA开发的阶段。界面如下:

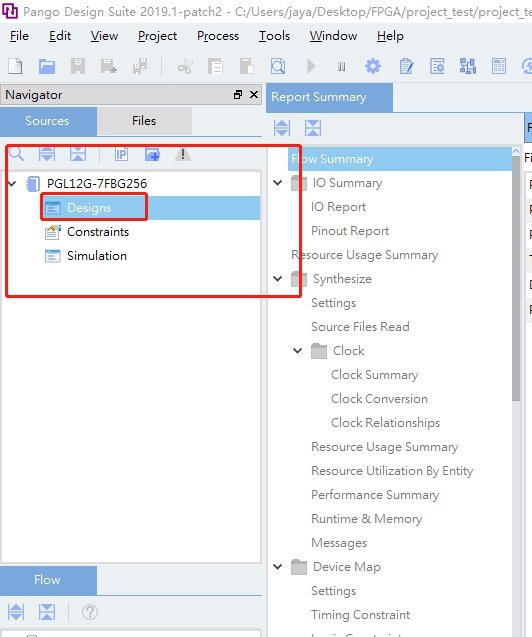

我们来双击Design,来创建我们的工程文件。也就是Verilog代码。

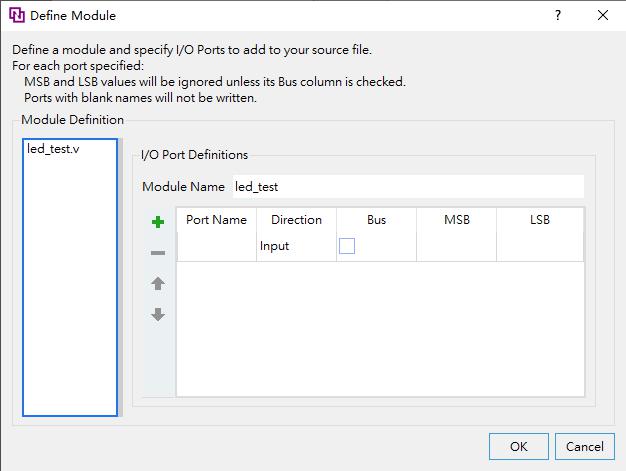

完成配置之后,向导会提示您定义I/O 的端口,这里我们可以不定义,后面自己在程序中编写就可以,单击 OK完成。

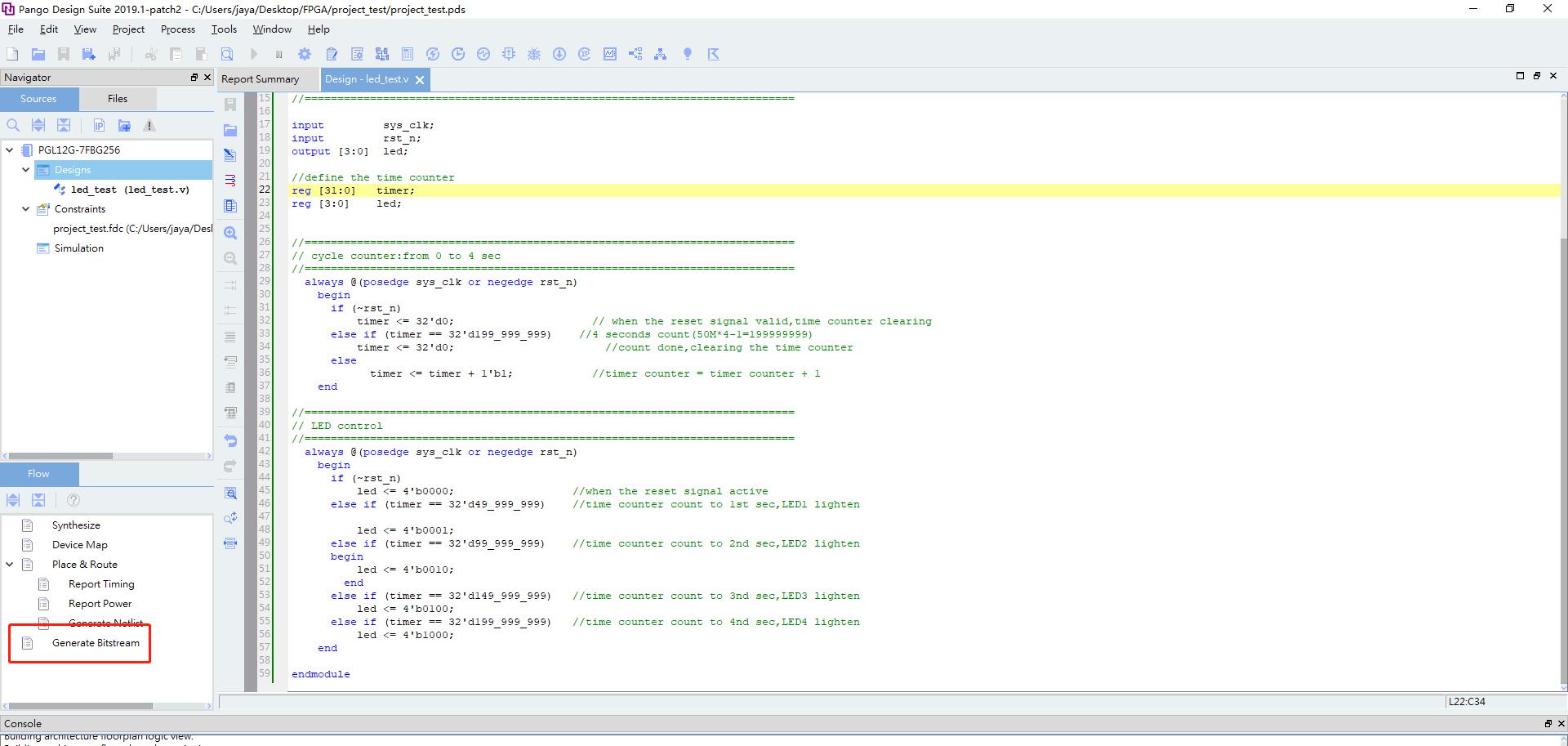

OK这样我们就终于可以写Verilog代码了。我们直接将,黑金给我们提供的代码写进来。

简单的流水灯,代码如下:

//===========================================================================

// Module name: led_test.v

//===========================================================================

`timescale 1ns / 1ps

module led_test

(

sys_clk, // system clock 50Mhz on board

rst_n, // reset ,low active

led // LED,use for control the LED signal on board

);

//===========================================================================

// PORT declarations

//===========================================================================

input sys_clk;

input rst_n;

output [3:0] led;

//define the time counter

reg [31:0] timer;

reg [3:0] led;

//===========================================================================

// cycle counter:from 0 to 4 sec

//===========================================================================

always @(posedge sys_clk or negedge rst_n)

begin

if (~rst_n)

timer <= 32'd0; // when the reset signal valid,time counter clearing

else if (timer == 32'd199_999_999) //4 seconds count(50M*4-1=199999999)

timer <= 32'd0; //count done,clearing the time counter

else

timer <= timer + 1'b1; //timer counter = timer counter + 1

end

//===========================================================================

// LED control

//===========================================================================

always @(posedge sys_clk or negedge rst_n)

begin

if (~rst_n)

led <= 4'b0000; //when the reset signal active

else if (timer == 32'd49_999_999) //time counter count to 1st sec,LED1 lighten

led <= 4'b0001;

else if (timer == 32'd99_999_999) //time counter count to 2nd sec,LED2 lighten

begin

led <= 4'b0010;

end

else if (timer == 32'd149_999_999) //time counter count to 3nd sec,LED3 lighten

led <= 4'b0100;

else if (timer == 32'd199_999_999) //time counter count to 4nd sec,LED4 lighten

led <= 4'b1000;

end

endmodule

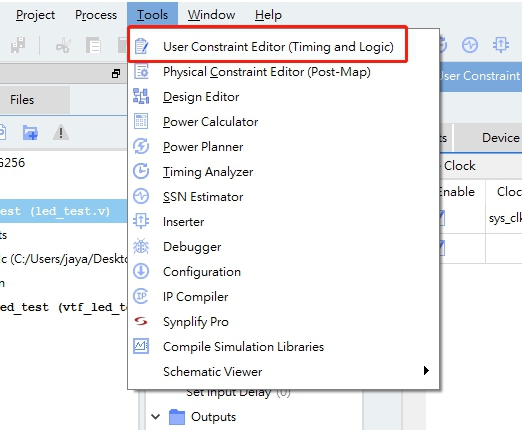

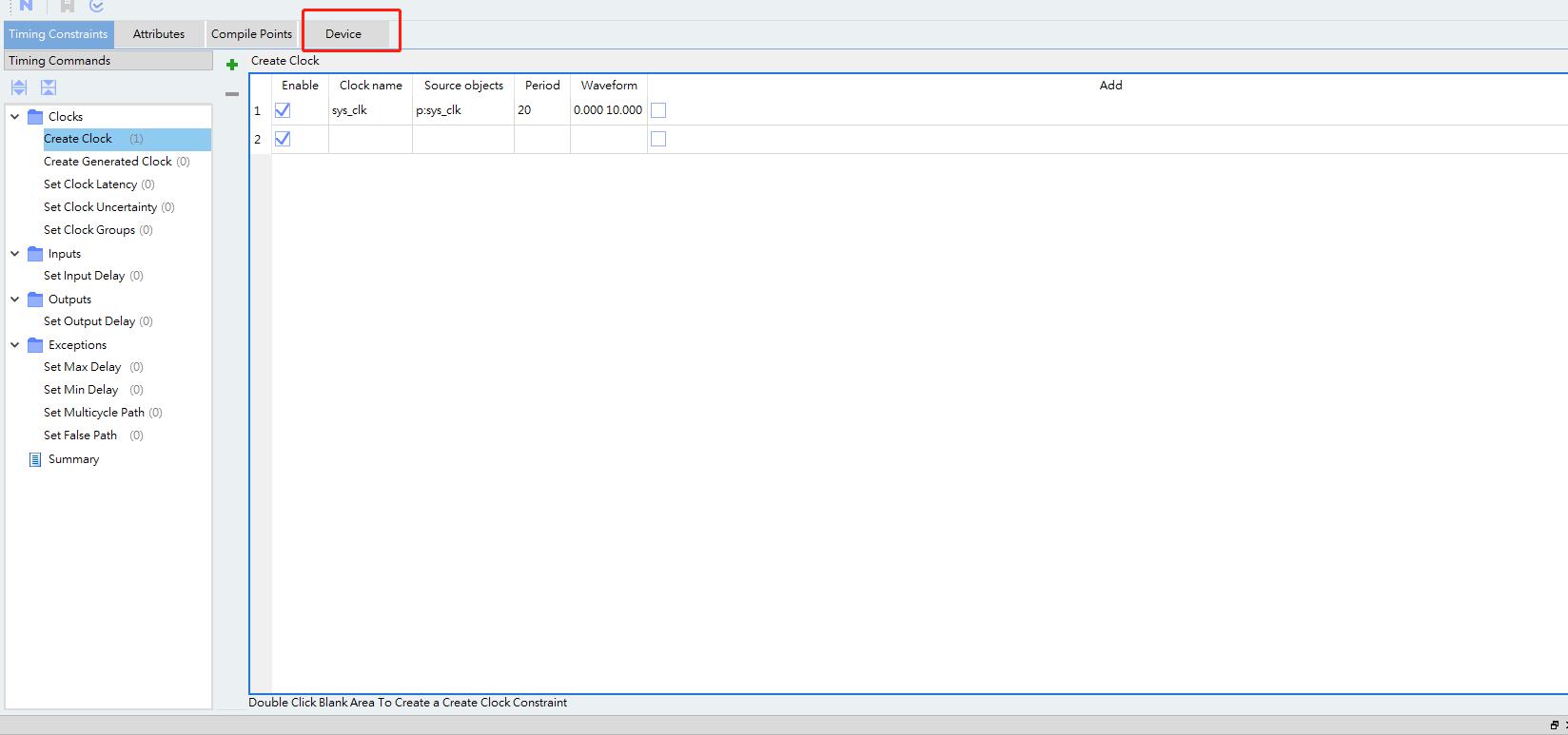

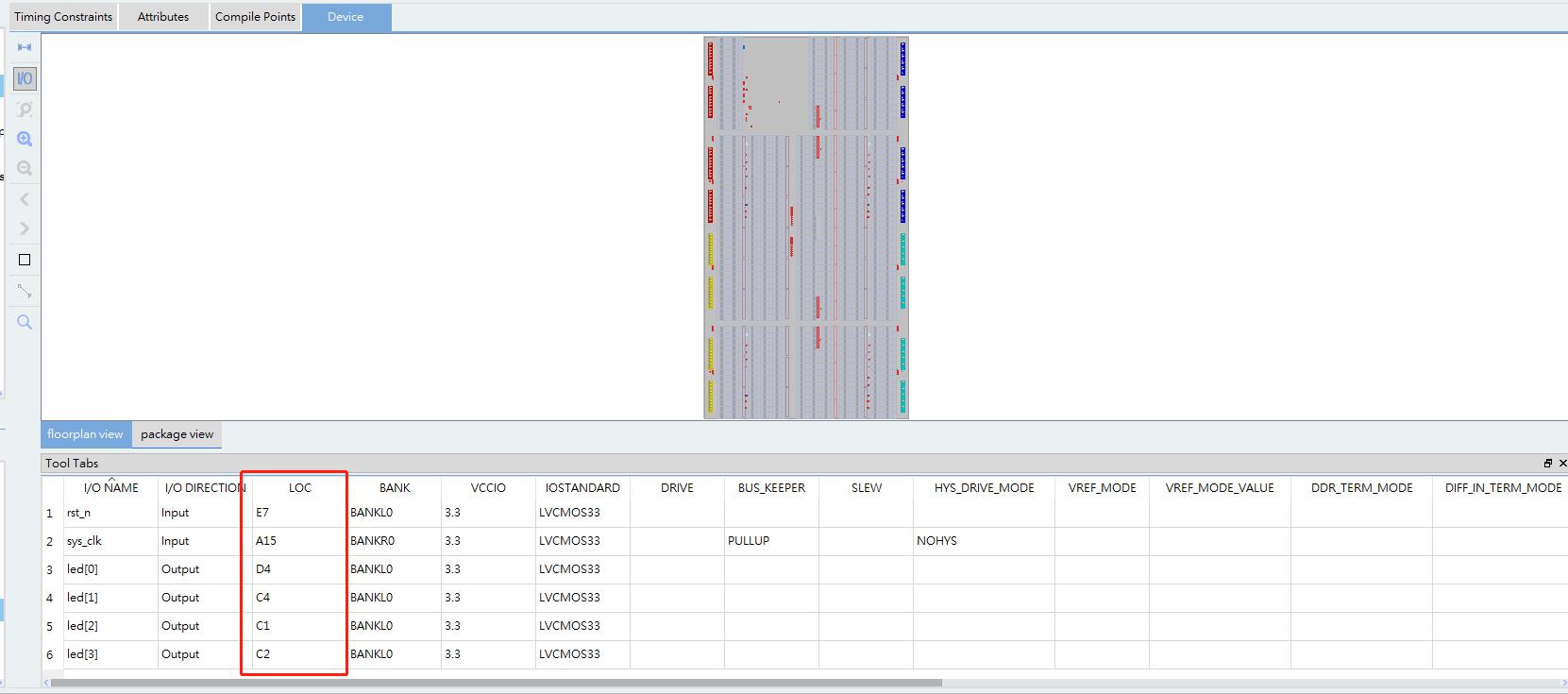

下一步,我们来分配管脚,(PS:这里也是和单片机不同的,一般的话单片机写好C,完成编译就可以download进单片机,而FPGA则是要在固定的工具中进行管脚的指定,才可以进行最后的综合,进而拿到bitfile,烧录进FPGA进行使用),我们打开约束器进行约束,指派管脚。我们选择device,中的IO

在这里指定好使用的管脚,保存。如下图:

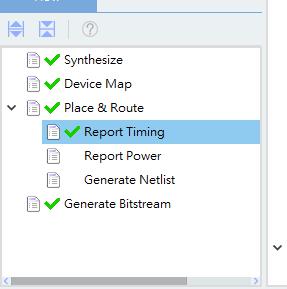

然后我们来综合生成Bitstream,双击Generate Bistream,如下图红框。(PS:这里的Bitsream就是最终的网表文件,可以理解为FPGA的程序)如果工程在生成位流文件过程中没有错误,则会出现下图中每一步都正确的“√”,否则就会在Messages 栏中显示 errors 的错误。

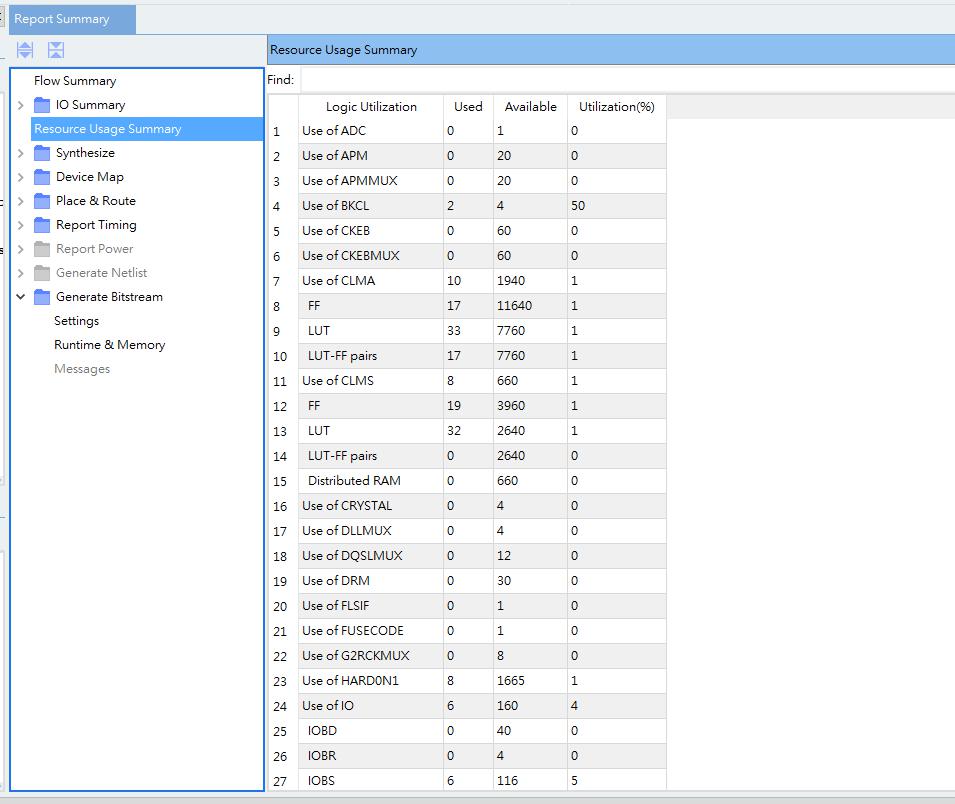

完成综合之后,位流文件生成完成后,我们可以在Report Summary 页面的到了 FPGA 资源的使用情况。

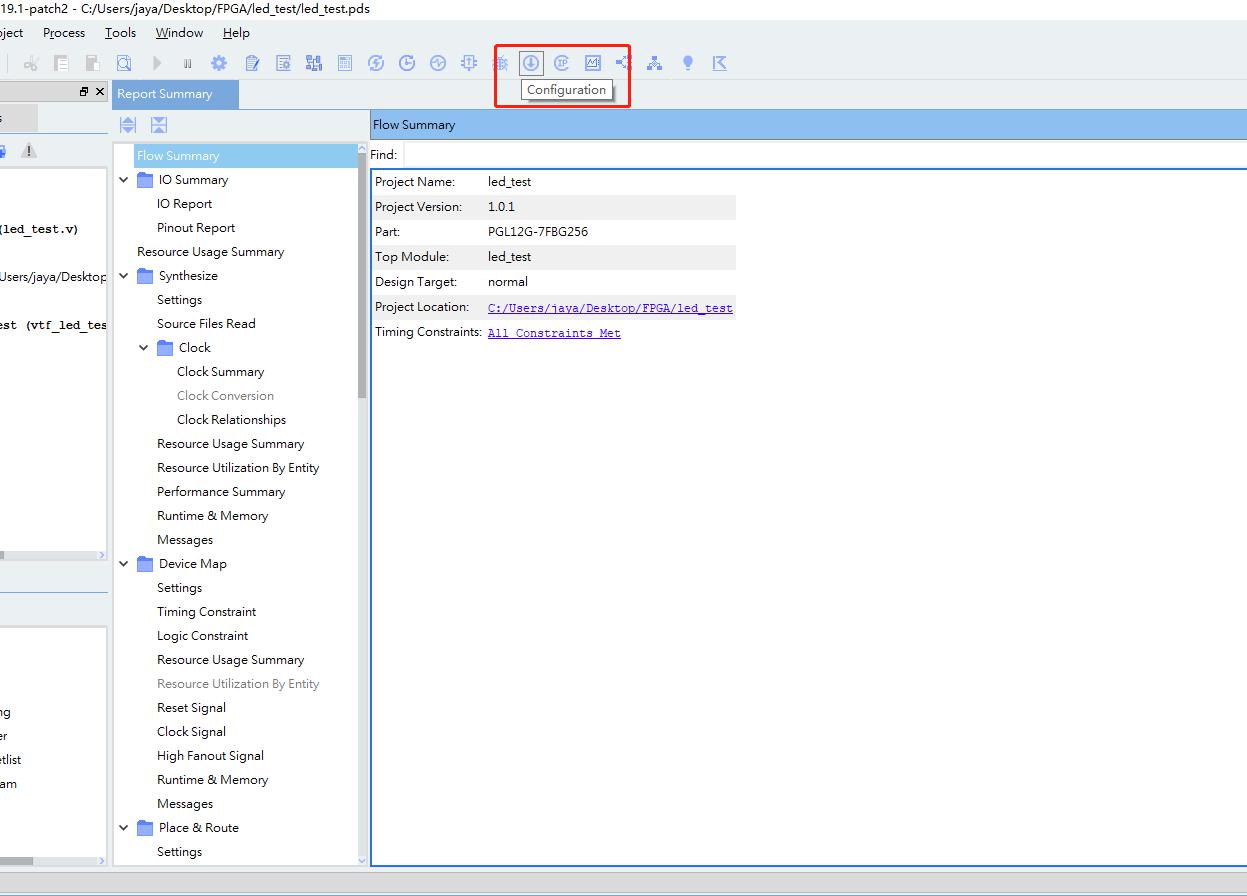

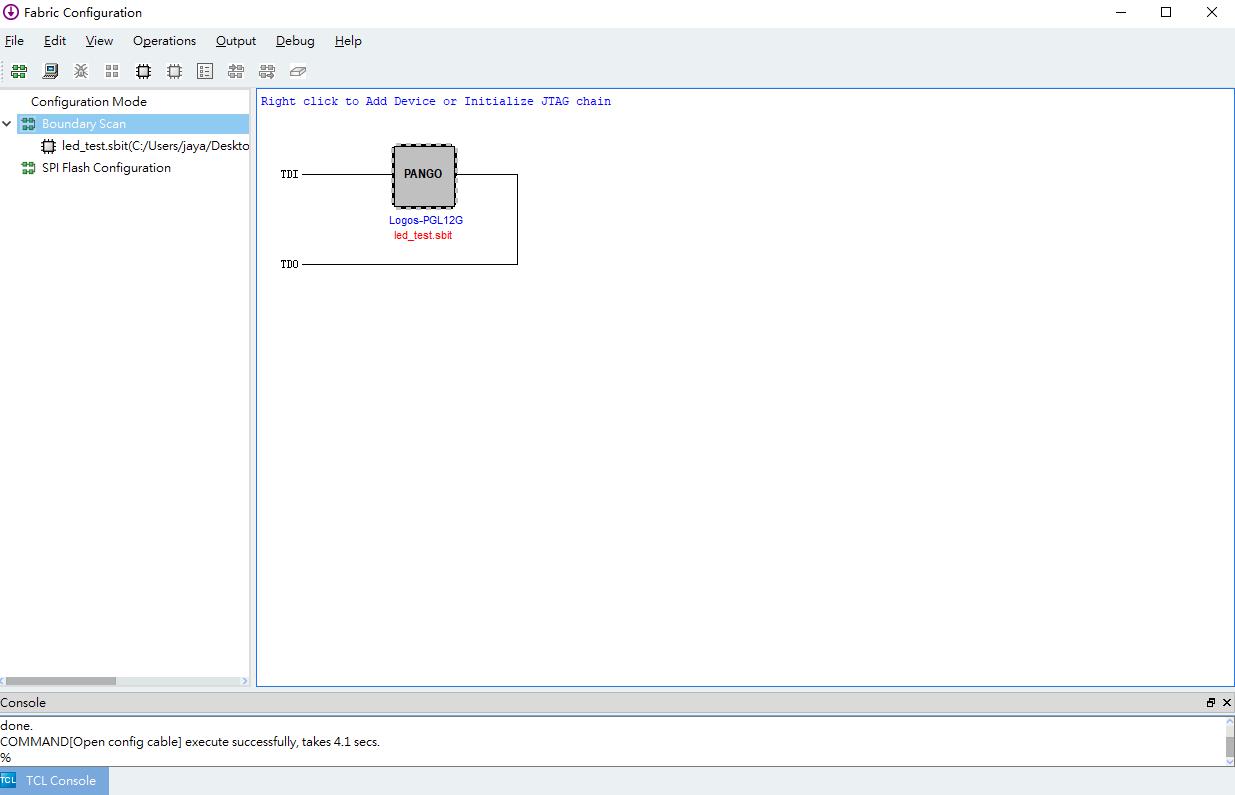

最后就是下载的过程,单击界面中的“Configuration”按钮,在弹出的对话框中,Boundary Scan的作用是下载程序到 FPGA 中运行;SPI Flash Configuration是将程序固化程序flash 中。

我们选择下载到FPGA中执行。然后单击Promgram,这样程序就下载到板子中执行了。执行效果见下图:

到这里呢,我们的使用就告一段落,简单来总结下,作为黑金的开发板,配套资源完善,同时PGL12G表现出了国产FPGA的希望,尽管国产FPGA在未来还有好长一段路要走,但是PGL12G也让我们看见国产FPGA的希望,紫光同创于2013年12月正式成立,到20年也仅仅只有7年的发展,与那些FPGA的巨头比较当然是吃亏的,这次紫光同创与黑金合作的开发板,主观感受是面向FPGA的初学者,同时也为我们的FPGA学习之路提供了新的选择。

整体来说PGL12G这块开发板还是很适合初学者入手的,有黑金强大的开发经验和教育背景作为支撑,通过PGL12G开学习FPGA的开发,还是相当不错的。黑金也提供了充足的例程,其中不乏一些高端些的功能,比如透过CMOSSensorOV5640,实现视频数据的采集,再比如通过逻辑单元实现视频数据的边缘检测,通过IP核调用原生的HDMI实现视频的输出等等,整体在学习的角度很全面,基本上由浅入深全部囊括。初学者如果将黑金的资料完整的玩下来,基本上就会对于FPGA会有一个比较深刻的认识。

另外说一些小编自己的感受,整块板卡用下来,无论是板卡的设计,还是开发环境,对于国人习惯来说还是比较友善的。(PS:额除了工程目录不能使用中文名)可以看得出开发环境上紫光同创是上了心的。文档的描述也是十分完善,上手过程会接触到的问题基本都有描述。国产FPGA距离成为FPGA大佬来说,肯定还是有很长的路要走的,但是在走这一段路的路程中,我们可以通过学习了解与紫光同创共同提高进步。

版权声明:本文系电路城原创文章,转载请注明出处!

4447

4447

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?