本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

一、软件简介

Pango Design Suite 是紫光同创基于多年 FPGA 开发软件技术攻关与工程实践经验而研发 的一款拥有国产自主知识产权的大规模 FPGA 开发软件,可以支持千万门级 FPGA 器件的设计开 发。该软件支持工业界标准的开发流程,可实现从 RTL 综合到配置数据流生成下载的全套操 作。

二、支持平台

三、软件安装

一般地,将软件安装在 C:\pango\ PDS_2022.1;(此为默认安装路径)。软件安装完成后, 会在桌面以及程序菜单中添加快捷方式 PangoDesign Suite2022.1;在程序菜单 Pango Design Suite2022.1 文件夹中包含 Pango Design Suite、软件卸载的快捷方式 Uninstall、程序附件 Accessories 以及软件文档 Documents。

本教程以 Pango Design Suite 2022.1 Windows 版本安装进行说明,下面将详细介绍 PDS 安装过程:

安装程序

(1)首先关闭电脑所有杀毒软件,否则杀毒软件有可能会拦截一些组件,造成安装失败 或功能缺失等不确定结果;

(2)双击安装包中的安装程序 Setup.exe,启动安装程序:

(3)启动安装程序后的界面如下:

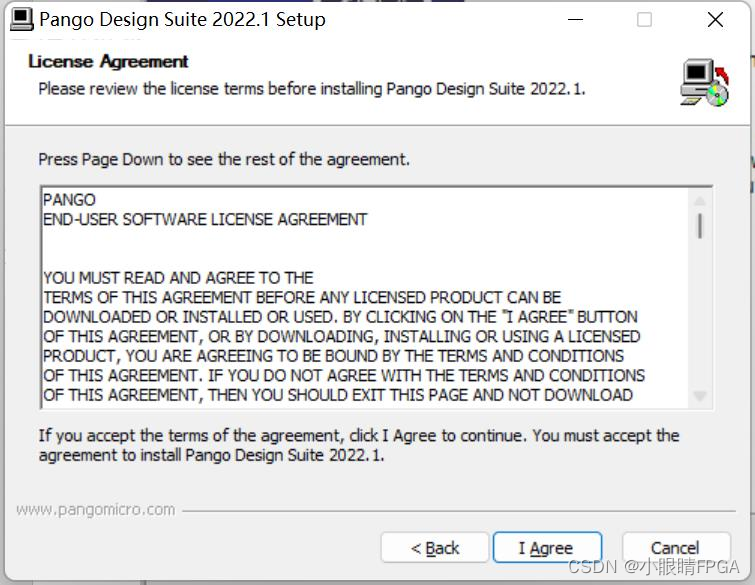

(4)点击“Next”,跳转至许可协议对话框:

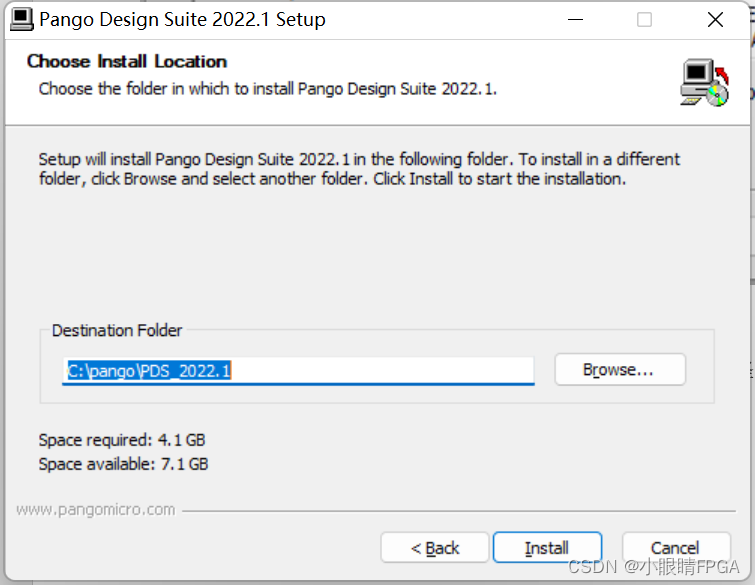

(5)选择接受许可协议,点击“I Agree”按钮,进入选择安装路径选择框,如下图所示, 默认安装路径为 C:\pango\PDS_2022.1,建议采用默认路径。

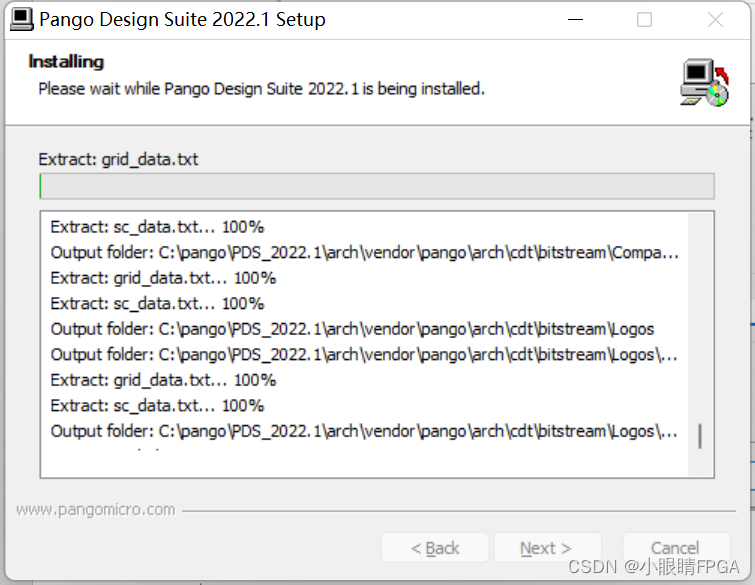

(6)直接点击“Install”,则跳转到安装界面。

(7)耐心等待至完成全部安装过程,点击“Finish”,安装完毕。

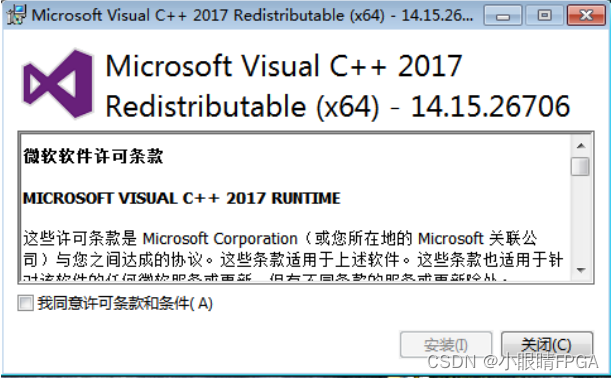

(8)安装完成后,会提示是否需要安装运行库 vcredist_VS2017.exe。若电脑之前未安装 过则需要安装此运行库后才能运行 PDS,点击“是”按钮进行安装;若电脑之前已安装过此运 行库则无需再次安装,点击“否”按钮不进行安装即可。

注:如果不确定,建议点击“是”进行安装,否则可能导致 PDS 无法运行。

(9)点击“是”进入运行库安装界面,选择同意许可条款和条件,点击安装按钮进行安 装。

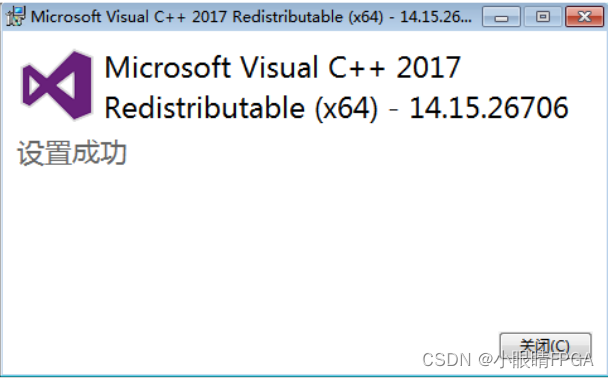

(10)安装完成界面点击“关闭”完成安装。

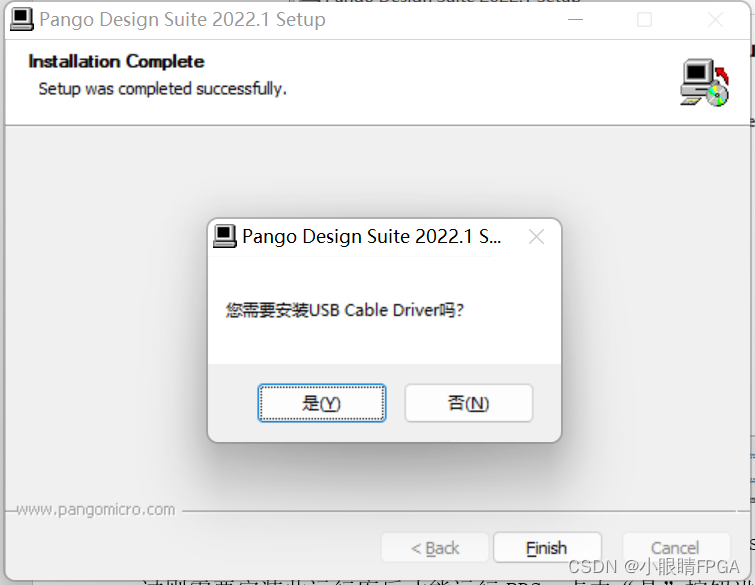

(11)完成安装后,会提示是否需要安装 USB Cable Driver。安装点击“是”,否则可能 导致下载器无法正常使用。

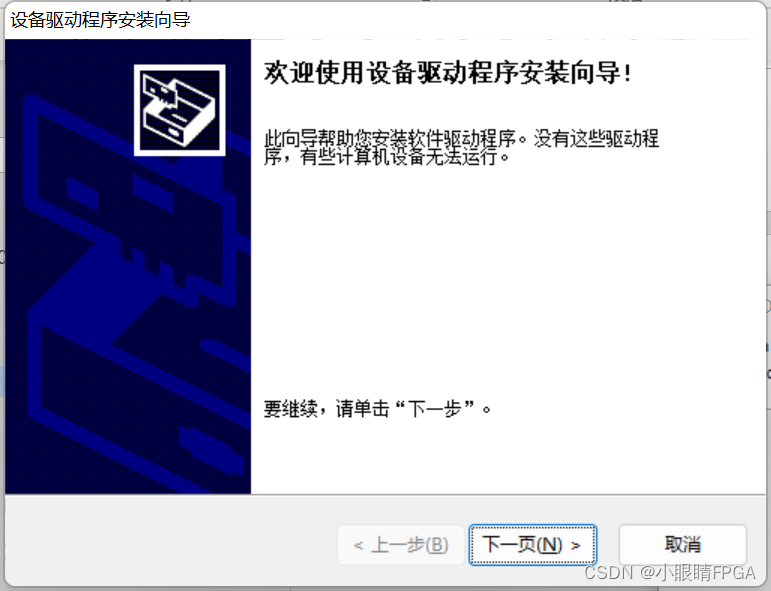

(12)点击“是”进入驱动程序安装界面:

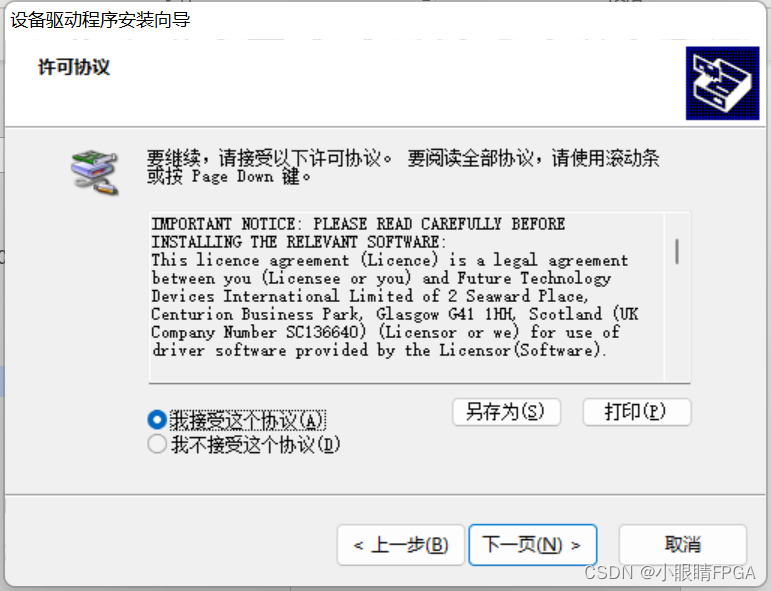

(13)点击“下一步”进入安装驱动程序许可协议界面。点击“我接受这个协议”,然后点击“下一步”。

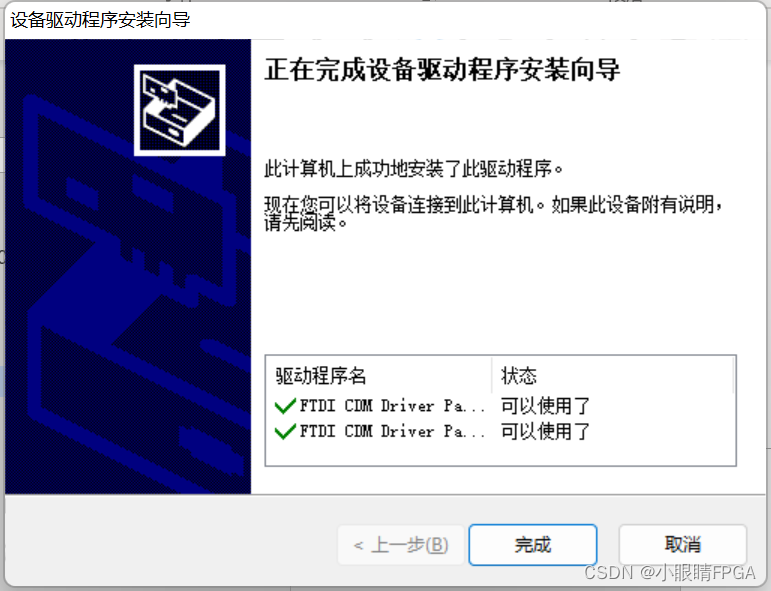

(14)点击“完成”,完成驱动程序的安装。

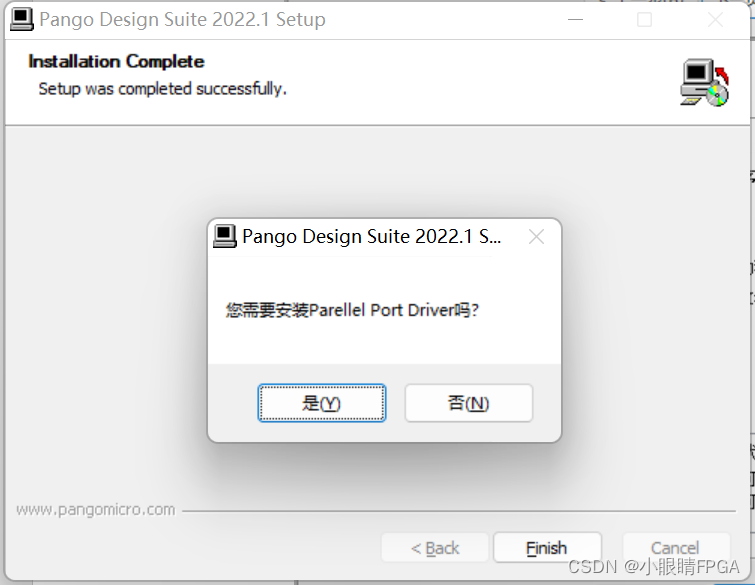

(15)完成安装后,会提示是否需要安装 ParellelPortDriver。安装点击“是”。

(16)点击“是”进行并口驱动程序安装。

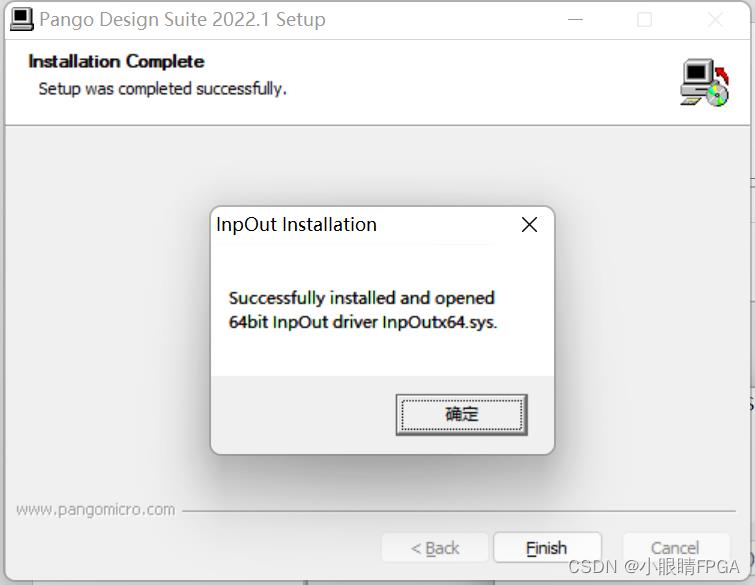

(17)完成后点击“确定”,结束安装。在桌面上看到如下图标:

四、License 关联,环境变量设置

软件完成安装后,Pango Design Suite 需要 License 文件才能正常使用。

注:

(1)License 申请请联系相关销售,提供相关资料,他会帮您申请;

(2)若只使用 Verilog 则只需申请 PDS License 即可,若使用 VHDL 或 System verilog 则还需要申请 Synplify license;

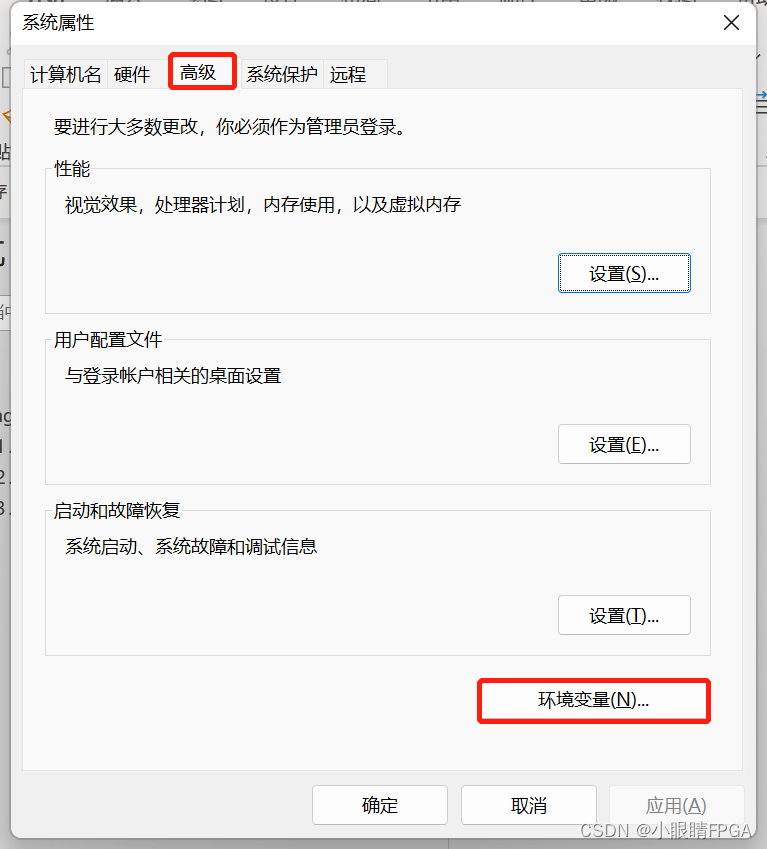

(3)为方便管理 license 文件,建议在 PDS 软件安装目录下新建一个 license 文件夹 存放 license 文件。 首先在电脑上打开运行窗口,接着在窗口内输入 sysdm.cpl 然后回车。在系统属性界面内 选择高级,然后点击环境变量,进行设置。

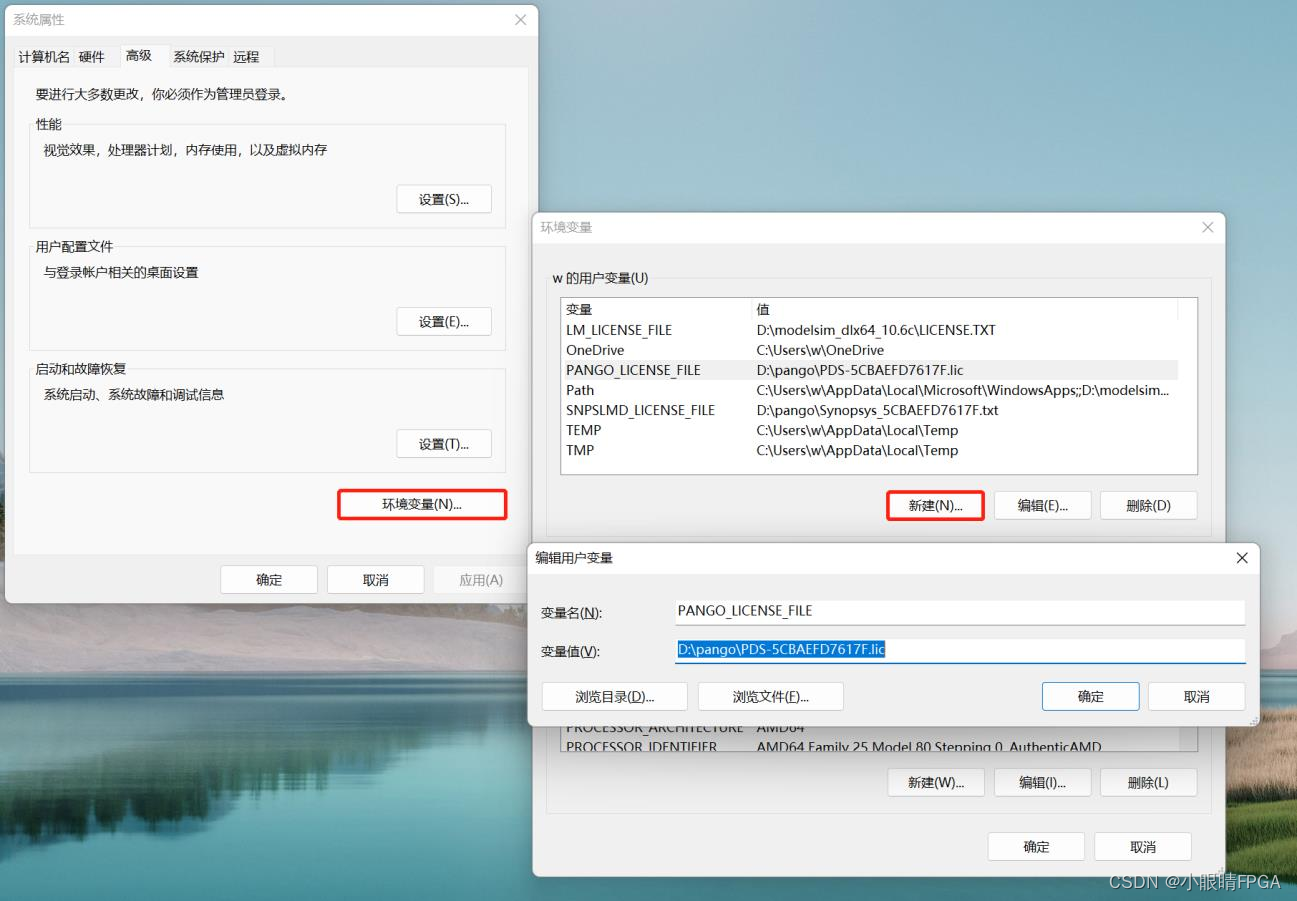

PDS license 环境变量设置

若 PDS license 文件路径为:D:\pango\license\pds_node-locked.lic

直接设置环境变量:

变量名:PANGO_LICENSE_FILE 变

量值:D:\pango\license\pds_node-locked.lic

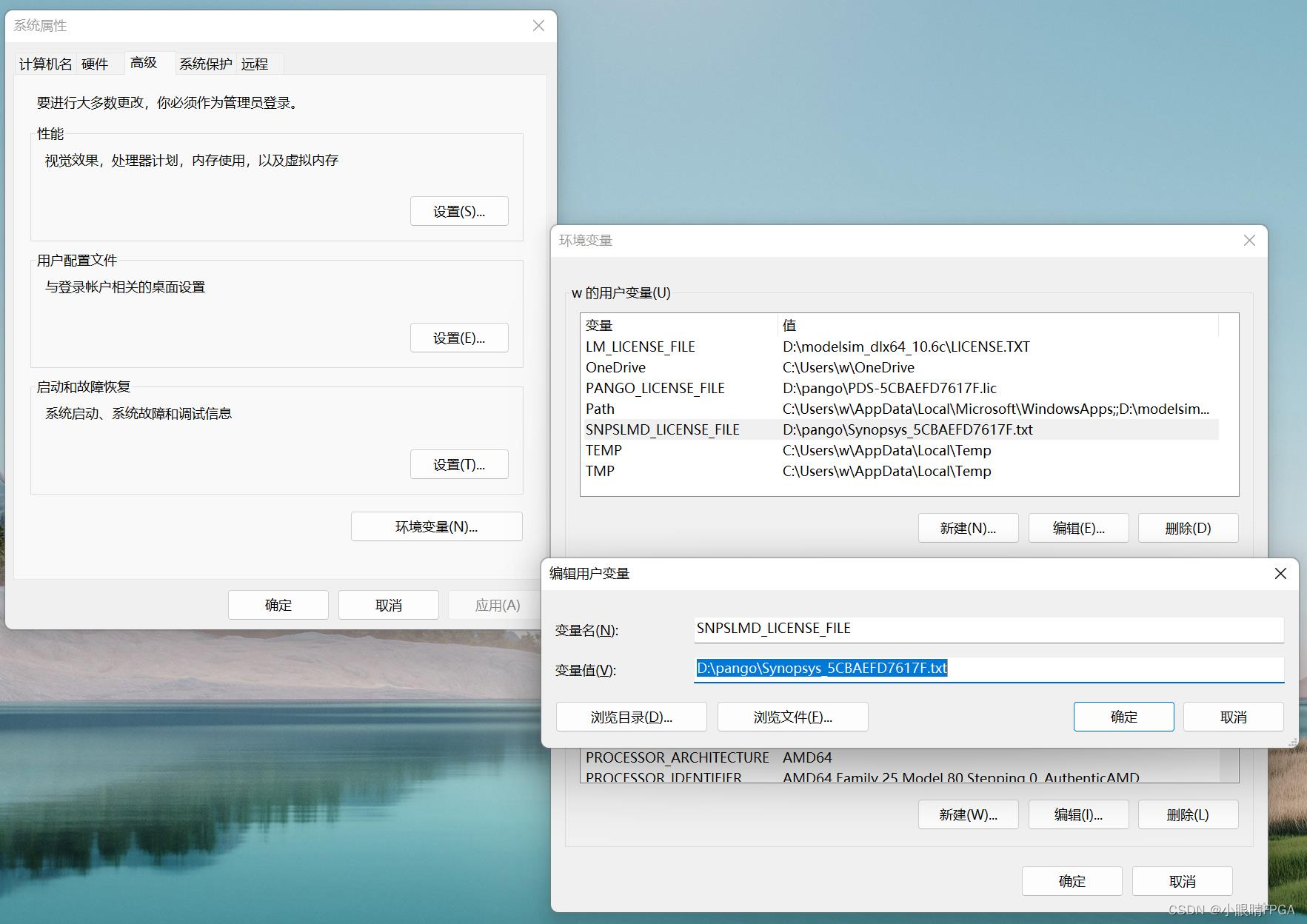

Synplify license 环境变量设置

若使用 Synplify 综合工具也需要相应的 OEM License 文件才能使用。

若 Synplify license 文件路径:E: \pango\license\oem_node-locked.lic

直接设置环境变量:

变量名:SNPSLMD_LICENSE_FILE

变量值:E:\license\oem_node-locked.lic 即可。

注:因 OEM 所在路径不支持空格,故不支持在含空格的路径下安装

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?