前言:下文时序图来源于AT24C02 2-Wire serial EEPROM DataSheet

一、I2C总线通信协议

1.线路

I2C通信结构中的两个线路:

(1)时钟线 SCL

(2)数据线 SDA

2.协议内容

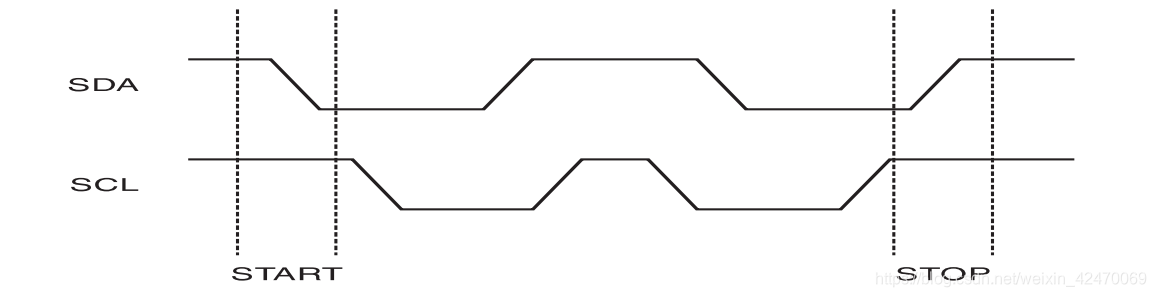

数据传送过程中,在时钟线SCL为高电平时间段内,要想成功传输数据,数据线 SDA 必须为固定状态(要么高要么低),不允许有跳变。

时钟线 SCL 为高电平时间段内,数据线 SDA 的任何电平变化将将引起总线的数据传输为的启动或停止。

(1)启动条件

时钟线 SCL 保持高电平期间,数据线 SDA 电平从高变低,即为启动。

(2)停止条件

时钟线 SCL 保持高电平期间,数据线 SDA 电平从低变高,即为停止。

来张时序图感受下:

注:

(1)通信协议内容还有一项:只有在总线非忙时才允许进行数据传输;

(2)数据传输中,启动信号 START 最先发送.。

二、EEPROM 电路——FPGA外围电路之一

以常见的型号为 AT24C02 的 EEPROM 为例

AT24C02 DataSheet地址

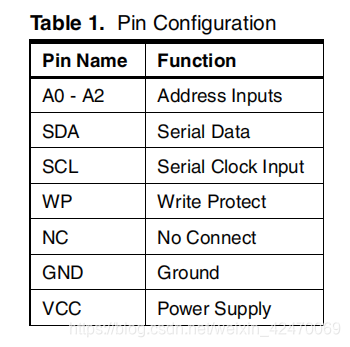

1.外部封装及管脚定义

通常情况下,一般选择 8pin 的封装。

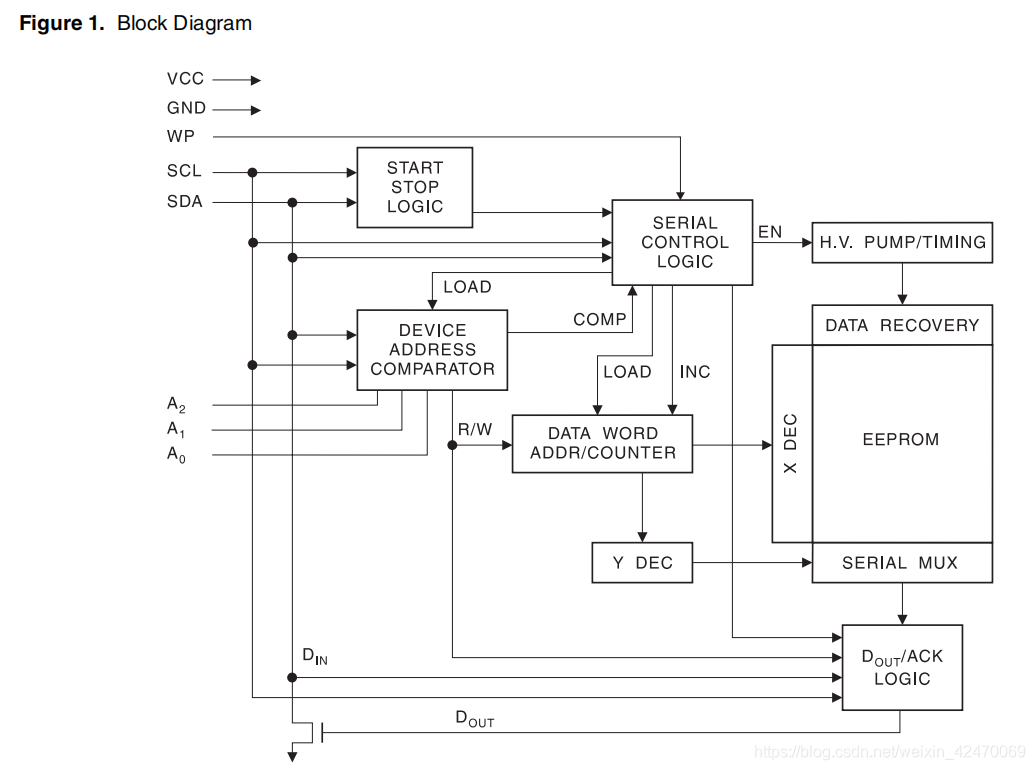

2.结构要素图(配合上面的管脚定义看)

3.FPGA外围电路搭建

SDA、SCL、WP接口要接上拉电阻和电压。

三、读写时序

1.字节写

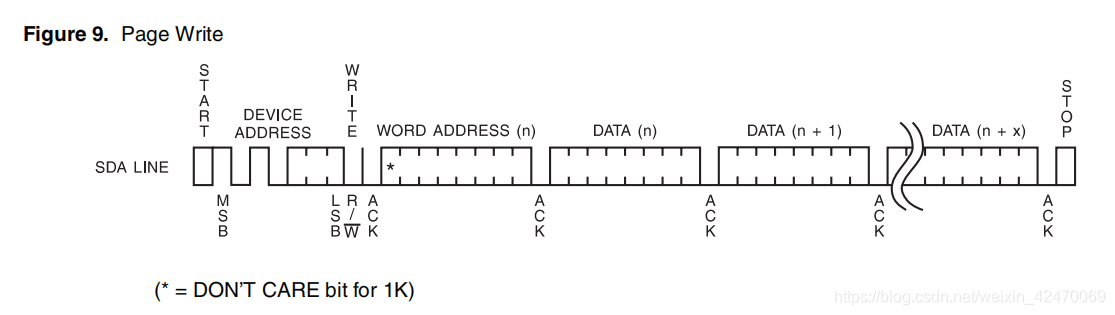

1.起始位 START ;

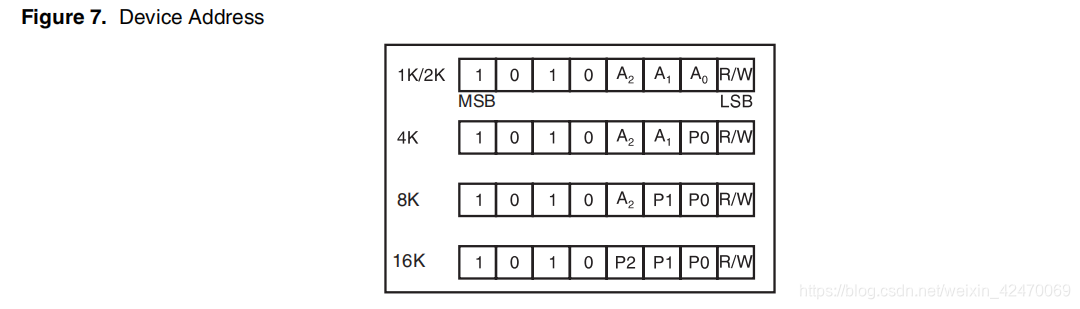

2.设备地址DEVICE ADDRESS 为 8bit ,而实际上表示设备地址只有 3bit(A0-A2),高4bit 固定为 1010,最后 1 bit 为读写标志位,高电平表示从设备读数据,低电平表示向设备写数据。

例如当电路中只有一个 EEPROM 并向其中写数据时,则地址位后三位为000,MSB-LSB 7bit 为 1010 000,由于此时是写操作(低有效),所以对应最后读写标志位为0,即 8bit 为 1010 0000。

3.设备地址应答位 ACK,低电平表示 EEPROM 接收到数据,注意此时 SDA LINE 为 EEPROM 向主机发送数据;

4.写入字节地址 WORD ADDRESS;

5.写入字节地址应答位 ACK ;

6.写入的数据DATA;

7…写入的数据ACK;

8…停止位 STOP。

注:

关于设备地址DEVICE ADDRESS 和 MSB-LSB组成的 8 bit 定义如下:

2.页写

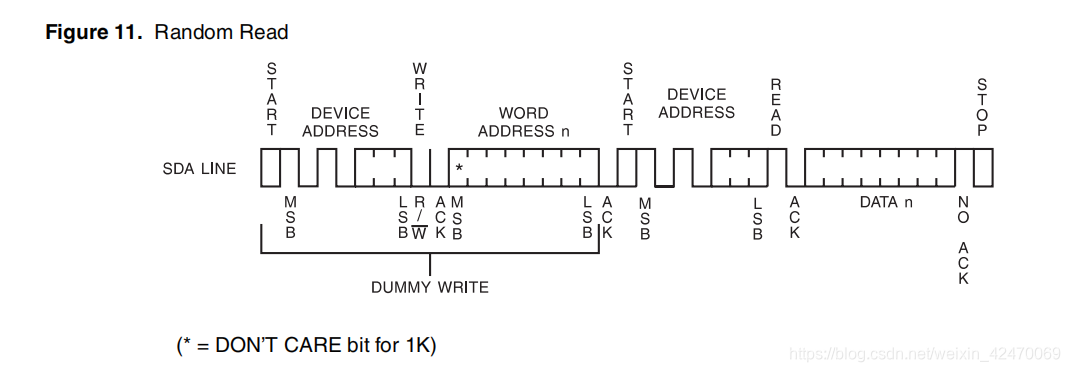

3.随机读

注:这里有一段时序为 “DUMMY WRITE”,在写完设备地址和数据字地址被 EEPROM 应答后,还要再重新初始化,此时要再传输设备地址,同时 LSB 的后一个字节为高电平,表示读操作。

读出的最后一个数据后无应答。

4.顺序读

本文深入探讨了I2C总线通信协议的原理,包括时钟线SCL和数据线SDA的工作机制,以及启动和停止条件。通过分析AT24C02 EEPROM的电路设计和管脚定义,详细解释了EEPROM的FPGA外围电路搭建。此外,文章还介绍了EEPROM的读写时序,包括字节写、页写和随机读等操作流程。

本文深入探讨了I2C总线通信协议的原理,包括时钟线SCL和数据线SDA的工作机制,以及启动和停止条件。通过分析AT24C02 EEPROM的电路设计和管脚定义,详细解释了EEPROM的FPGA外围电路搭建。此外,文章还介绍了EEPROM的读写时序,包括字节写、页写和随机读等操作流程。

2254

2254

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?