本实验采用的开发板是黑金7020,ZYNQ嵌入式开发流程如下图所示。

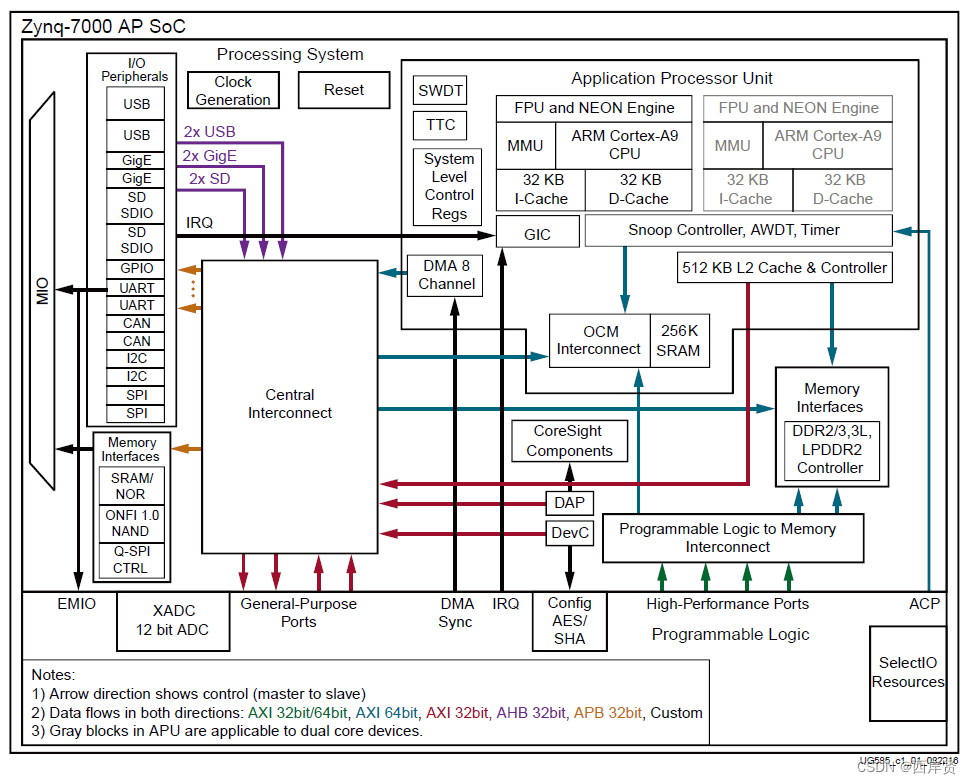

ZYNQ 7000系列的功能块相互连接示意图如下图所示。

一、创建Vivado工程

Ubuntu中安装Vivado软件说明了如何在Ubuntu中安装Vivado软件,使用下面命令打开Ubuntu中的Vivado软件。

source /opt/Xilinx/Vivado/2017.4/settings64.sh

vivado &

打开后创建工程,选择工程要存放的路径,设置工程名称,然后点击下一步。

选择RTL工程,勾选不指定源文件。

选择对应的开发板类型。

接下来是信息汇总界面,如果前面设置有误可以返回修改。

到这里工程就创建完毕了!

二、添加并配置IP核

Vivado工程创建完毕后点击Create Block Design,创建一个模块设计。

创建好模块设计后在Diagram窗口中添加ZYNQ的IP核。

双击后该IP核就添加成功了。

双击该IP核后出现IP核的配置界面,如下图所示。

在DDR配置这里原则一个和自己开发板兼容的芯片型号。

查看原理图中UART对应的PS口,我的开发板对应的是48和49这两个口。

在外围IO口配置这里找到48和49口对应的UART双击,使其变成绿色。

BANK500对应的电压是3.3V,BANK501对应的电压是1.8V,可以从原理图中找到相应的依据。

在MIO配置界面中设置电压,按照原理图进行配置。

移除掉IP核上不必要的接口,取消勾选FCLK_RESET0_N和M AXI GP0接口。

取消勾选FCLK_CLK0接口。

此时的IP核就很精简了,点击上面蓝色的Run Block Automation,在弹出的对话框中保持默认设置,点击OK即可。

点击验证设计有无错误。

生成输出产品。

三、生成顶层HDL

生成顶层HDL的过程很简单,右键system,选择Create HDL Wrapper即可。

生成结束后,双击打开.v文件,里面就是Verilog语言描述的。

四、导出到SDK

点击File—>Export—>Export Hardware,弹出下面的对话框,因为本实验不涉及到PL端的设计,因此不用勾选比特流文件,直接点击OK即可,导出的文件就存在于本工程中。

导出成功后在工程文件夹下就多了一个.sdk的文件夹,如下图所示。

进到该文件夹里面,只包括一个后缀为.hdf的文件。

五、在SDK中创建应用工程

点击File—>Launch SDK,弹出下面的对话框,点击OK即可。

等待软件启动。

启动成功之后点击左上角Application Project选项,弹出下面的对话框,设置工程名称后点击Next。

在这里选择一个空的应用,点击Finish。

完成之后就多了两个文件夹,一个是工程文件,一个是BSP板级支持包文件,BSP文件是连接工程文件和下面系统硬件文件的桥梁。在src目录下新建一个.c文件,创建完成后点击Finish。

在菜单栏Windows—>Preferences下的Appearance—>Colors and Fonts中,在右侧找到Basic—>Text Font就可以设置字体大小。

创建C程序成功后就可以在里面填入代码了,简单的代码如下。

写完代码后程序会自动被编译。

六、板级验证

连接开发板到电脑,不仅要接开发板上的JTAG接口,还要连接开发板上的UART接口。

在Ubuntu关闭的时候设置虚拟机,将串行端口添加进来,不然连接之后无法识别。

这里如果没有可选项,确保接口都是连接到虚拟机的,然后再修改/dev/目录下对应字符设备的权限为666,修改完成后再到这里就可以看见了。

然后选择项目下的.elf文件,右键选择在硬件平台上运行,如下图所示。

但是这个时候却出现了下面的问题,我没能在Ubuntu端解决这个问题,改用Windows下执行了。

同样的操作在Windows下就没问题,如下图所示,终端成功的打印出了Helloworld!

当然也可以不用自己开终端,SDK自带终端,如果窗口中没有SDK Terminal,可以在菜单栏找到Window—>Show View—>Other…下搜索调出该终端了。

串口的选择根据自己电脑识别的而定,如下图所示。

在硬件平台上运行,结果同样打印在了SDK终端中,如下图所示。

参考视频:

正点原子手把手教你学ZYNQ之嵌入式开发

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?