点击蓝字关注“PYNQ开源社区”

PYNQ-PRIO是一个介绍如何利用FPGA部分可重配置特性和PYNQ框架提供的方便的API,对FPGA分时复用,提高FPGA灵活性的项目。可重配置是指在一个FPGA工程中,划分了静态逻辑部分和动态逻辑部分,静态逻辑部分是指在运行过程中逻辑不变的部分,动态逻辑部分是指在运行过程中可以根据需要下载特定比特流文件实现不同逻辑的部分,在工作时,修改某一动态逻辑部分不会对静态逻辑部分和其他动态逻辑部分造成影响,实现了FPGA的功能上的分时复用。

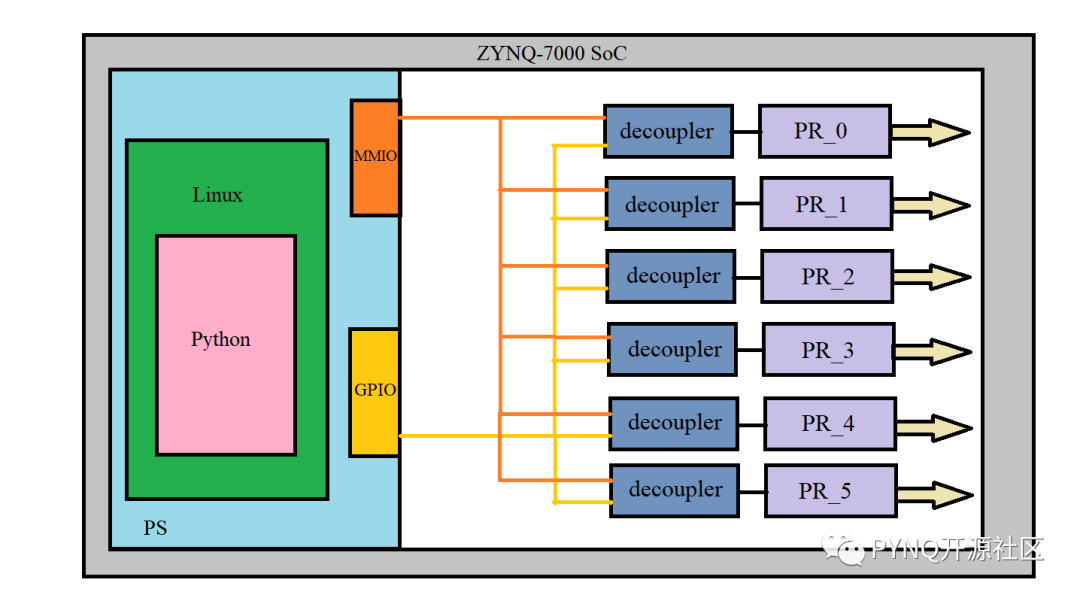

上图为工程项目示意图。通过软硬件划分,在PS端中负责Linux和通信,PL端例化了6个PR(Partitial Reconfiguration)块。每个块中有GPIO、uart和IIC等几种不同的RM(Reconfiguration Module),它们通过各自的partitial bitstream下载。动态逻辑部分和静态逻辑部分使用分离器保证它们互不影响,并在动态逻辑部分下载完成后对下载好的部分进行复位。

此项目中在PYNQ框架下有两种驱动这些IP的方式:一是直接使用PYNQ提供的API操作overlay里面的IP,二是将这些IP通过DTS(Device Tress Source)注册到linux sysfs中,然后调用linux提供的驱动。

快速开始

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4636

4636

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?