欢迎大家来我的博客逛逛👏:hauhau.cn

摘 要

通过quartus软件,使用verilog语言,采用了结构化行为描述方法,完成了单周期CPU模型机的设计和仿真,实现了模型机的正常运行

**关键字:**整体、系统

第一章 原理与模型机设计

1.1 实验有关原理

冯诺依曼计算机工作原理

- 计算机由控制器、运算器、存储器、输入设备、输出设备五大部分组成。

- 程序和数据以二进制代码形式不加区别地存放在存储器中,存放位置由地址确定。

- 控制器根据存放在存储器中地指令序列(程序)进行工作,并由一个程序计数器控制指令地执行。

-

单周期CPU:指的是一条指令的执行在一个时钟周期内完成,然后开始下一条指令的执行,即一条指令用一个时钟周期完成。

-

指令系统:指一台计算机的所有的指令合集。

-

指令周期:是从取指令、分析指令到执行完该指令所需的时间,不同的指令其指令周期长短可以不同。

-

单周期CPU处理指令的步骤:

取指令 -> 指令译码 -> 指令执行 -> 存储器访问 -> 结果写回

1.2 模型机设计

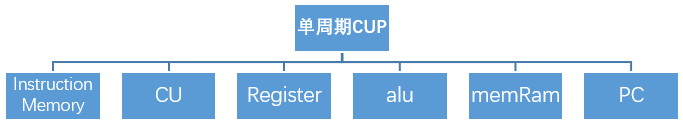

结构框图

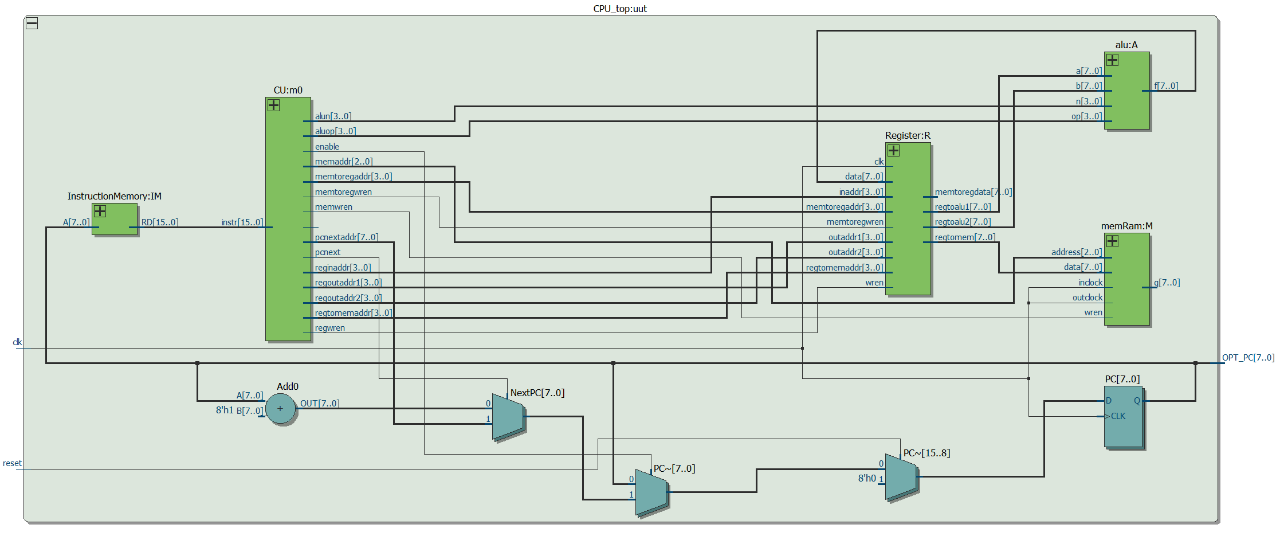

控制线路图

对应模块及功能

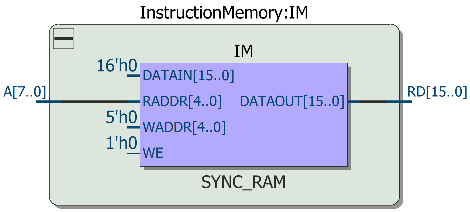

**InstructionMemory:**指令存储器,依据输入的地址从存储器中取出相对应的指令。

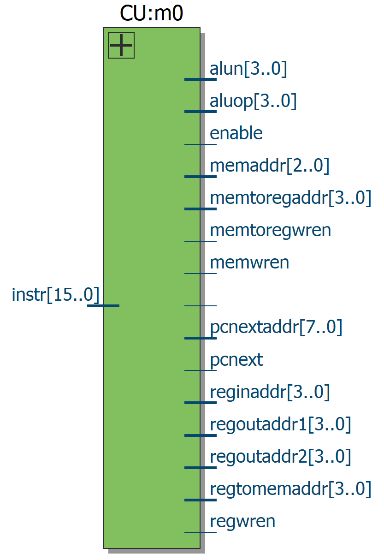

**CU:**控制单元,对指令进行分析,确定应该进行什么操作,并按照确定的时序向相应的部件发出控制信号。

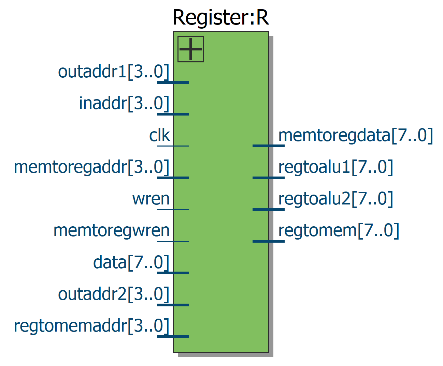

**Register:**数据寄存器(图1.2.4),负责将alu的运算数据和存储器中取出和存入的数据进行暂存,起到缓存的作用,因为单周期内不能同时读写,所以加入了一级缓存的设计。

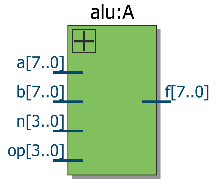

**ALU:**算术逻辑单元(图1.2.5),依据输入的操作码和数据进行相应的算数运算和逻辑运算。

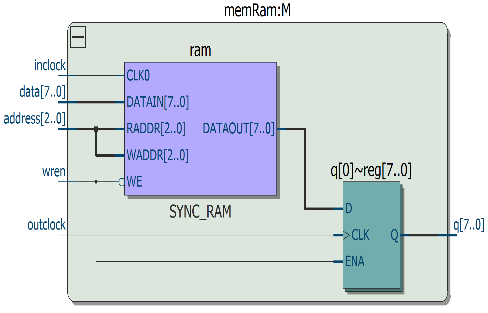

**memRam:**数据存储器(图1.2.6),对数据进行存储

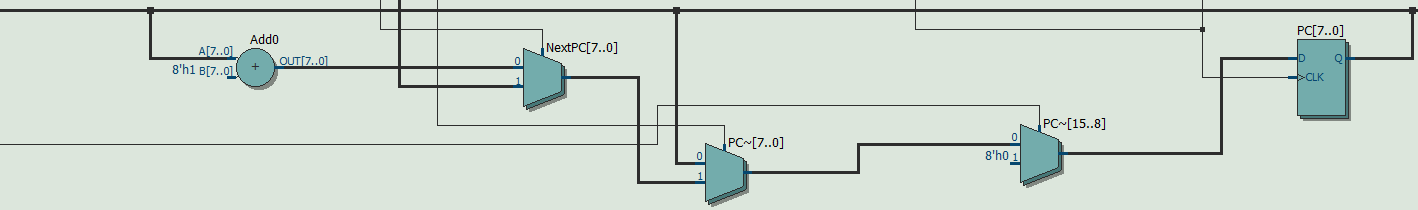

**PC:**程序计数器,进行取值操作,完成第一条指令的执行,而后根据PC取出第二条指令的地址。PC中的地址自动加一或由转移指令给出下一条指令的地址。

第二章 原理与模型机设计

2.1操作码格式

本次实验采用的是定长编码,机器指令16位编码,故根据实际需求设计出以下操作码:

`define ADD 4'b0000 //算术加

`define INC 4'b0001 //算术加1

`define NOT 4'b0010 //逻辑非

`define AND 4'b0011 //逻辑与

`define OR 4'b0100 //逻辑或

`define SLF 4'b0101 //数据左移

`define SRF 4'b0110 //数据右位

`define JMP 4'b0111 //无条件转移

`define STO 4'b1000 //写存储器,存数

`define LAD 4'b1001 //读存储器,取数

`define MOV 4'b1010 //数据传送

`define HAT 4'b1111 //暂停

2.2指令与格式

==>算数运算指令

(1) ADD rd, rs, rt

| 0000 | rd(四位) | rs(四位) | rt(四位) |

|---|---|---|---|

功能:rd <- rs + rt (算数加)

(2) INC rt, rs

| 0001 | rt(四位) | rs(四位) | 0000(未用) |

|---|---|---|---|

功能:rt <- rs (算数加1)

==>逻辑运算指令

(3) NOT rt, rs

| 0010 | rt(四位) | rs(四位) | 0000(未用) |

|---|---|---|---|

功能:rt <- !rs (逻辑非运算)

(4) AND rd, rs, rt

| 0011 | rd(四位) | rs(四位) | rt(四位) |

|---|---|---|---|

功能:rd <- rs & rt (逻辑与运算)

(5) OR rd, rs, rt

| 0100 | rd(四位) | rs(四位) | rt(四位) |

|---|---|---|---|

功能:rd <- rs | rt (逻辑或运算)

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8434

8434

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?