ADI 的codec和DSP的数据传输

1939的数据传输

ADC和DAC串行数据模式默认为I2S。 还可以将端口编程为左对齐,右对齐和TDM模式。 字宽默认为24位,可以设置为16或20位。

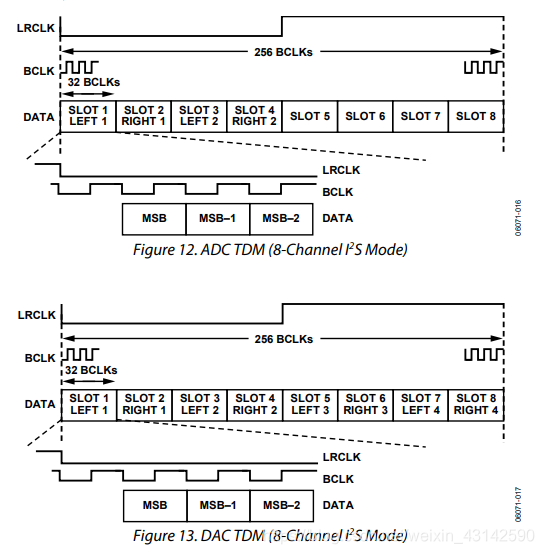

对TDM模式:

AD1939串行端口还具有几种不同的TDM串行数据模式。 第一种也是最常用的配置如图12和图13所示。在图12中,ADC串行端口输出一个数据流,该数据流由四个片上ADC和四个未使用的插槽组成。 在图13中,八个片上DAC数据插槽被打包到一个TDM流中。 在这种模式下,DBCLK和ABCLK均为256 fS。

1777作为codec的数据传输

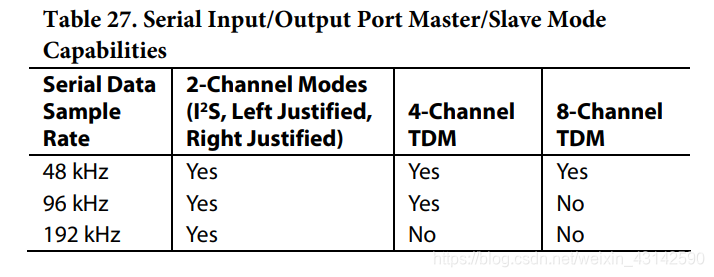

可以将ADAU1777的串行数据输入和输出端口设置为以2通道格式或4通道或8通道TDM流模式接收或发送数据,以与外部ADC,DAC,DSP或者SOC通讯。数据以二进制补码(MSB优先)格式处理。在2通道流中,左通道数据字段始终在右通道数据字段之前。在8通道TDM模式下,数据通道从ADC_SDATA0_ST和ADC_SDATA1_ST位设置的通道开始顺序输出。在串行数据端口(SAI_0,SAI_1)和串行输出控制寄存器(SOUT_SOURCE_x_y,地址0x13至地址0x16)中设置串行模式和帧中数据的位置。

串行数据时钟不需要与ADAU1777主时钟输入同步,但是LRCLK和BCLK引脚必须彼此同步。 LRCLK和BCLK引脚都为串行输入和输出端口提供时钟。可以将ADAU1777设置为系统中的主机或从机。因为只有一组串行数据时钟,所以输入和输出端口必须始终都是主机或从机。

串行数据控制寄存器允许控制时钟极性和数据输入模式。有效数据格式为I2 S,左对齐,右对齐(24位或16位),PCM和TDM。在除右对齐模式之外的所有模式下,串行端口都输入任意数量的位,最多24个限制。多余的位不会引起错误,但是会在内部被截断。

串行端口可以在每个LRCLK帧中以任意数量的BCLK跳变工作。 TDM模式下的LRCLK可以作为50%占空比时钟或1位宽脉冲输入到ADAU1777。表27列出了串行输入/输出端口可以工作的模式。当使用具有高BCLK速率(12.288 MHz)的低IOVDD(1.8 V),采样率192 kHz或以48 kHz采样率运行的8通道TDM模式时,

建议在串行端口引脚上使用较高的驱动器设置。高驱动强度有效地加快了波形的转换时间,从而改善了时钟和数据线的信号完整性。这些可以在PAD_CONTROL4寄存器(地址0x4C)中设置。

3634

3634

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?