前言:

相比FPGA开发来说,使用软核可以做一些FPGA实现比较困难的事情,比如lwip以太网传输。lwip的一些协议和主要功能就不在这里过多赘述,网上可以自行搜索,这里主要记录一下调试过程遇到的一些问题。

由于XILINX官方默认的lwip bsp驱动暂时不支持YT8511网口芯片,在使用该网口的时候需要自己手动修改库文件以支持该芯片,不同版本工具之间的修改方式大同小异,这边仅以Vitis 2021.1为例。

开发板FPGA型号:Xilinx–>Artix7–>xc7a100tfgg676-2;

开发环境:Vitis 2021.1;

PHY型号:裕太微YT8511;

一、新增lwip库,添加YT8511底层驱动

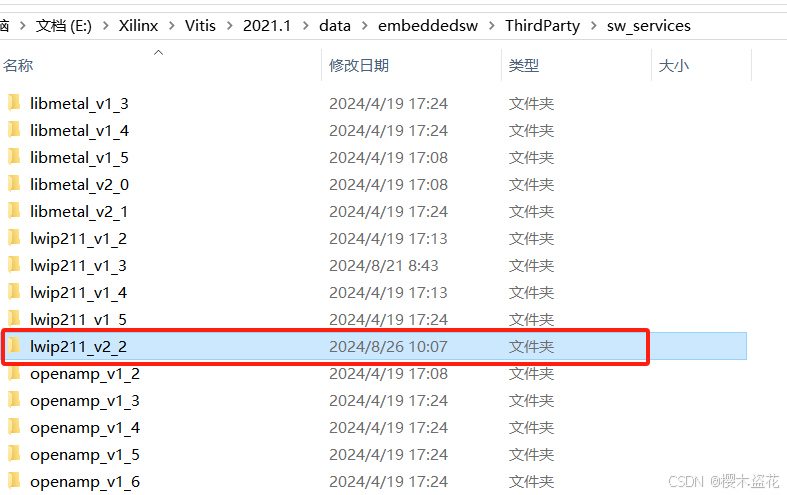

1-1:找到vitis ide安装目录下的LWIP库的路径,将其拷贝一份放到工程目录下:

这里我复制了一份lwip211_v1_5文件夹,将其名字改为lwip211_v2_2。

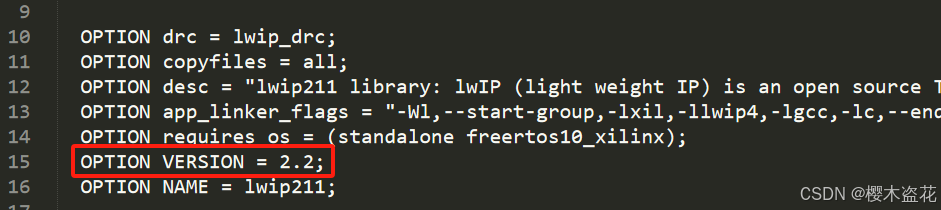

1-2:修改lwip211_v2_2\data\lwip211.mld文件,将其中的版本编号

OPTION VERSION =1.5;

修改为

OPTION VERSION = 2.2;

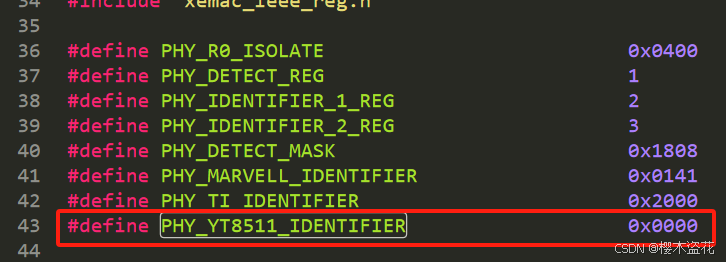

1-3:打开lwip211_v2_2\src\contrib\ports\xilinx\netif\xaxiemacif_physpeed.c,进行如下修改

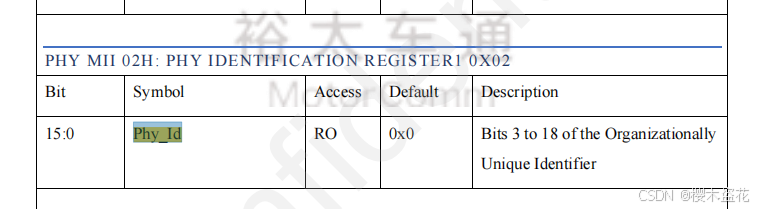

1-3-1:新增定义YT8511芯片ID

根据YT8511芯片手册定义的ID:0x0000

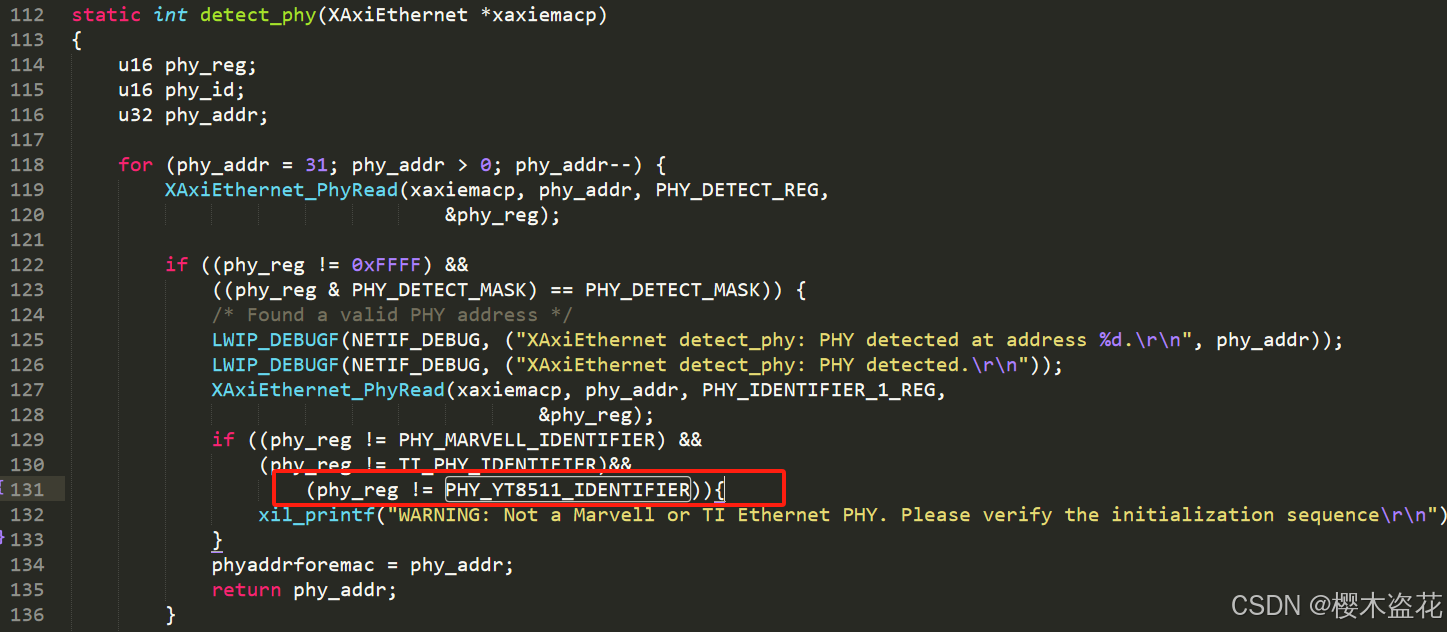

1-3-2:在原有的detect_phy函数中增加PHY8511识别条件

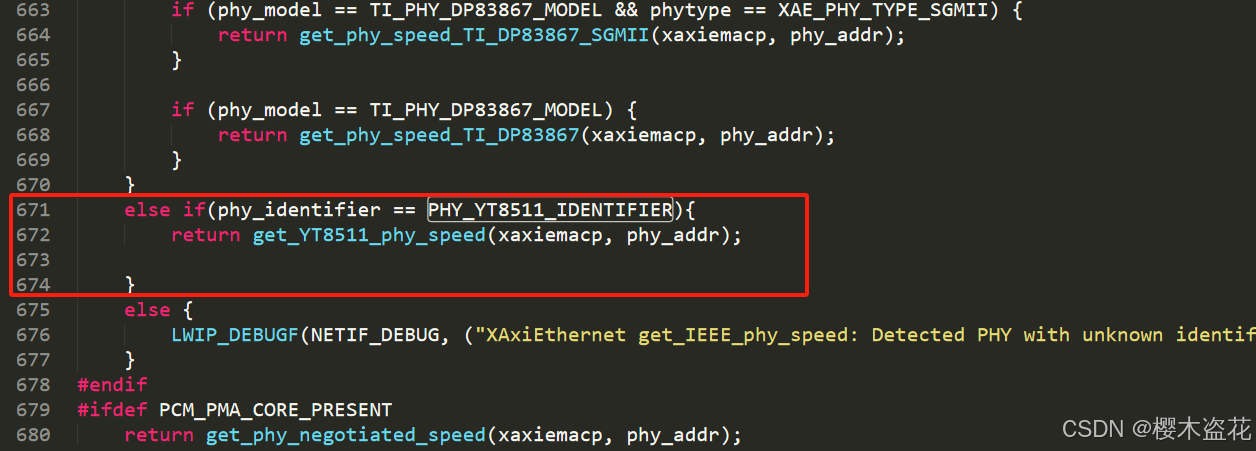

1-3-3:在原有的get_IEEE_phy_speed函数中新增速率获取条件

1-3-4:添加get_YT8511_phy_speed函数。

static u32_t get_YT8511_phy_speed(XAxiEthernet *xaxiemacp, u32_t phy_addr)

{

u16_t control;

u16_t status;

u16_t status_speed;

u32_t timeout_counter = 0;

u32_t temp_speed;

xil_printf("Start YT8511 PHY configuration,Please Waiting...\r\n");

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET, &control);

control = IEEE_CONTROL_REG_OFFSET_PAR; //0xa100---100M 0x9140---auto

xil_printf("BASIC CONTROL REGISTER PAR(Addr=0X00) is %x \r\n",control);

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET, control); //对PHY-8511进行配置 自协商模式

//Bit[15] :软件复位, 1:PHY 复位 0:正常模式;

//Bit[14] :内部环回模式 1:内部环回模式 0:正常模式;

//Bit[6] Bit[13]:选择网速带宽,只有在自动协商使能不开启的情况下有效 10:1000Mb/s 01:100Mb/s 00:10Mb/s;

//Bit[12] :自动协商使能 1:自动协商使能 0:自动协商不使能;

//Bit[9] :重启自协商 1:重新开始自协商 0:自协商重启完成。

xil_printf("PHY-YT8511 Register Parameter Setting Complete \r\n");

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, 0x1e, 0x000c);

XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, 0x1f, 0x0052);

// XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, 0x1e, 0x000d);

// XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, 0x1f, 0x0f30);

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET, &control); //读取0x00地址的控制寄存器,验证是否配置成功

xil_printf("BASIC CONTROL REGISTER PAR(Addr=0X00) is %x \r\n",control);

if (control){

xil_printf("PHY-YT8511 Register Setting Success \r\n");

}

else {

xil_printf("PHY-YT8511 Register Setting Fail\r\n");

}

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_STATUS_REG_OFFSET, &status); //读取0x01地址的控制寄存器

xil_printf("BASIC STATUS REGISTER_PAR(Addr=0X01) is %x \r\n",status);

//对我们用位的说明如下:

//Bit[5]:自协商完成 1:自协商完成 0:正在进行自协商;

//Bit[2]:连接状态, 1:连接成功 0:连接失败。

//这里只对连接状态进行验证

while ( !(status & 0x0004) ) {

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_STATUS_REG_OFFSET, &status);

}

XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_STATUS_REG_OFFSET, &status);

xil_printf("BASIC STATUS REGISTER_PAR(Addr=0X01) is %x \r\n",status);

xil_printf("PHY-YT8511 Link_Status is up \r\n");

XAxiEthernet_PhyRead(xaxiemacp, phy_addr,0X11,&status_speed); //读取0x11地址的PHY特定状态寄存器

xil_printf("PHY SPECIFIC STATUS REGISTER(Addr=0X11) is %x \r\n", status_speed);

//Bit[15:14]:连接速度

//11:保留

//10:1000Mbps

//01:100Mbps

//00:10Mbps

status_speed = status_speed>>8;

if (status_speed & 0x04) { //校对Link status real-time状态

temp_speed = status_speed & 0xc0;

if (temp_speed == 0x80)

return 1000;

else if(temp_speed == 0x40)

return 100;

else

return 10;

}

return XST_SUCCESS;

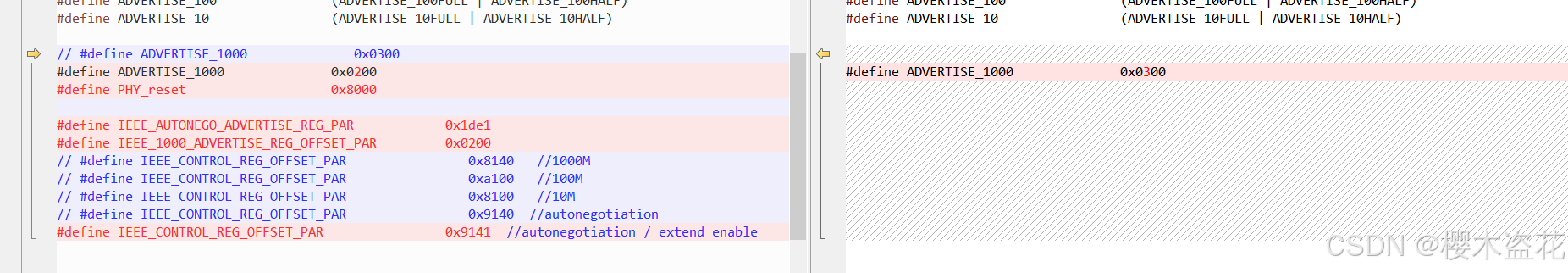

}1-4:打开lwip211_v2_2\src\contrib\ports\xilinx\netif\xemac_ieee_reg.c,进行如下修改

将左边代码复制到右边,对原有代码进行替换

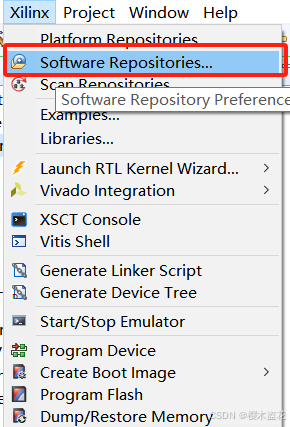

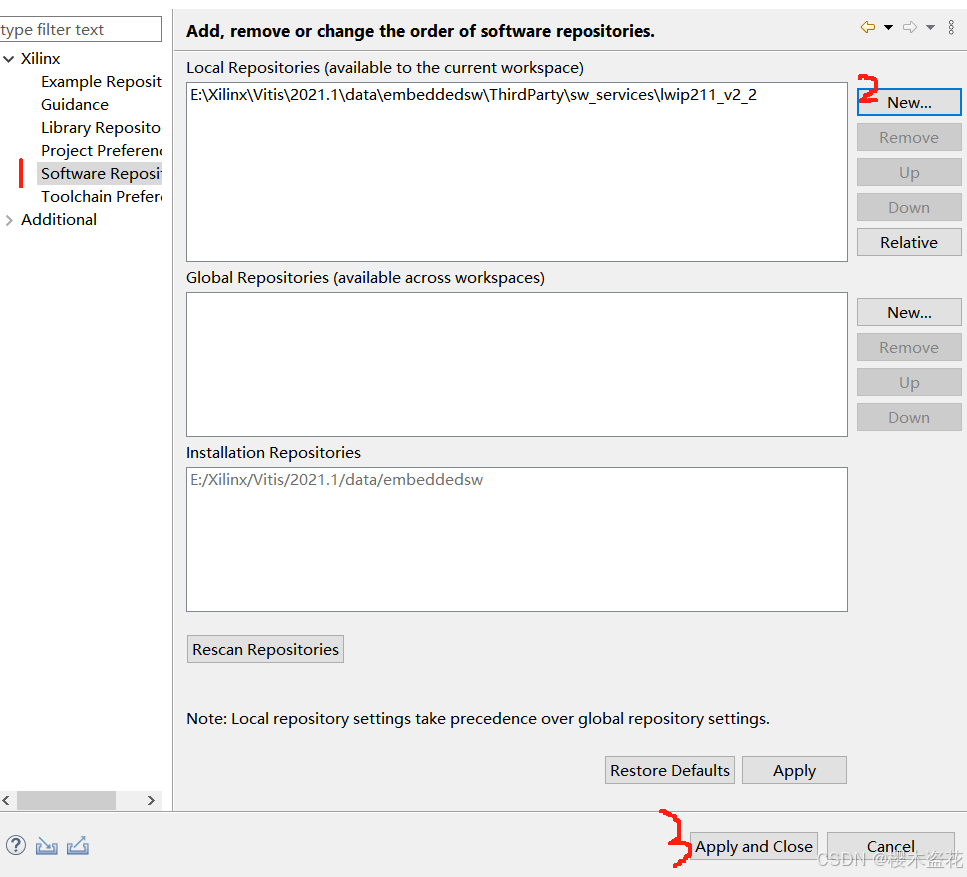

1-5:在Vitis软件中导入新增的lwip211_v2_2库路径

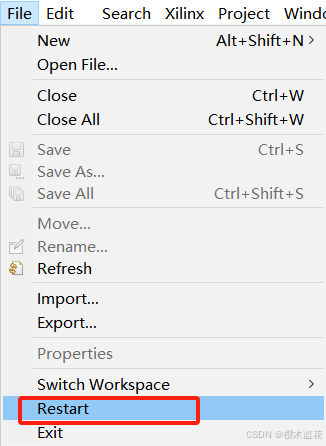

1-6: 重启Vitis软件

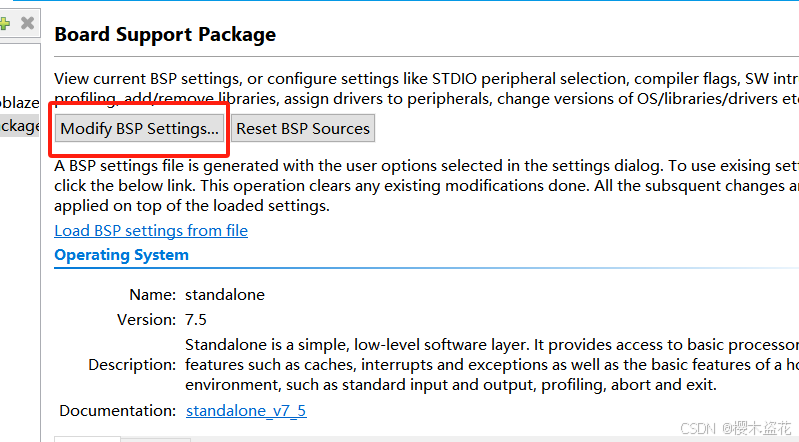

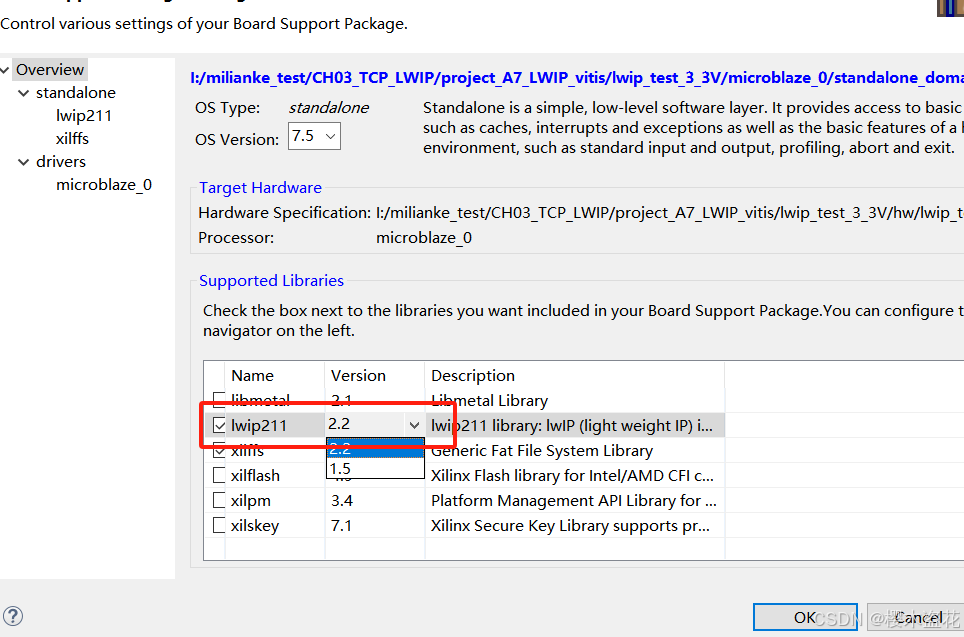

1-7:勾选lwip库文件,选择刚才新增的lwip211_2.2版本

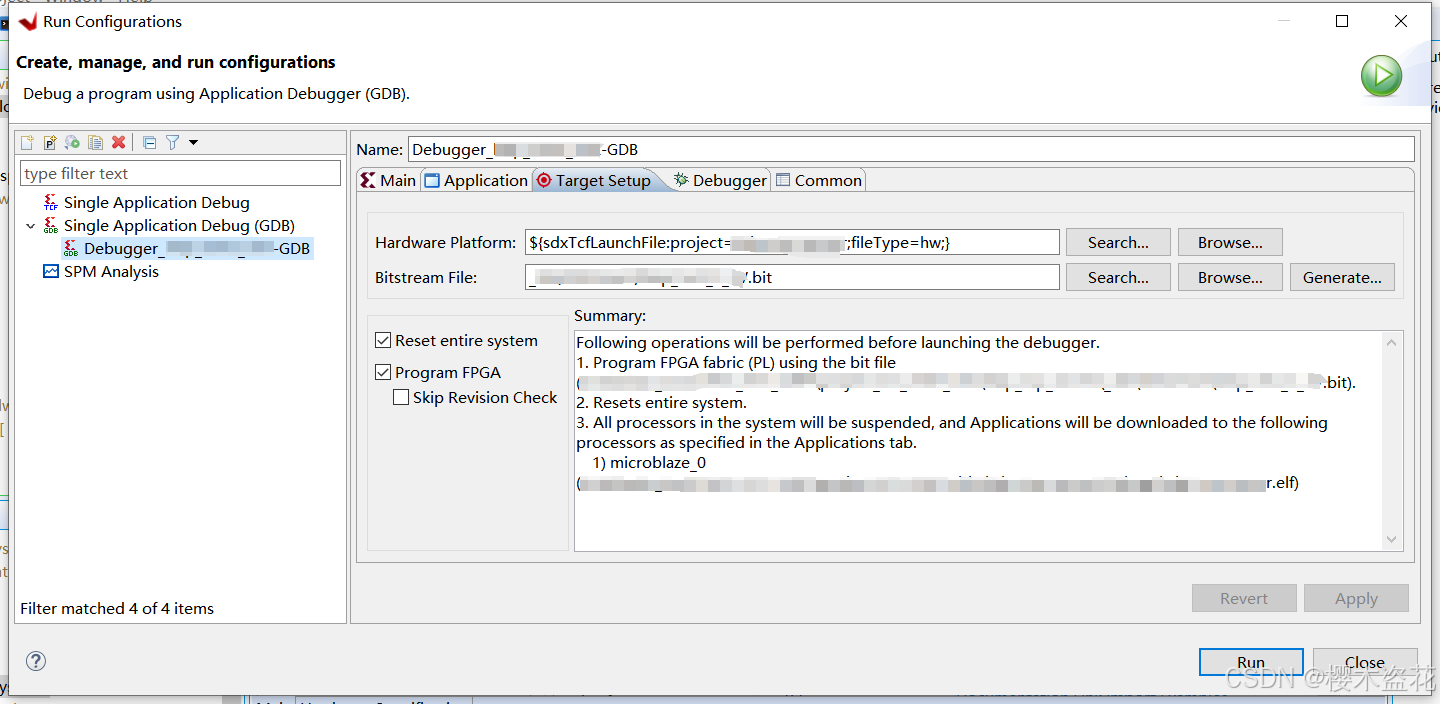

1-8:重新编译硬件平台以及代码工程后烧写

至此lwip bsp驱动支持YT8511网口芯片,对lwip库的添加完成。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?