目录

9、浮点单元

本章介绍 TriCore™ 浮点运算单元(FPU)架构。FPU 是 TriCore 配置中的可选组件。使用该内核的每个系统不一定都需要它。

可选的 FPU 是与 IEEE-754 兼容的浮点运算单元,与 TriCore 指令集配套使用。

9.1、功能概述

FPU执行兼容IEEE-754的单精度浮点运算指令,并支持以下特性集:

- 浮点加法、减法、乘法、MAC 和除法指令。

- 将有符号和无符号整数以及 32 位有符号分数(Q31 格式)转换为或从 IEEE-754 单精度格式转换为 TriCore 有符号和无符号整数以及 32 位有符号分数(Q31 格式)。

- QSEED.F 指令用于获取近似值,以便在牛顿-拉斐森迭代中执行平方根运算。

- 两个浮点数的比较。

- 实现了所有四种 IEEE-754 四舍五入模式。

- 可对选定的 IEEE-754 异常生成异步陷阱(TriCore 1.3.1 和 TriCore 1.6)。

限制:

FPU有以下限制和使用限制:

- 只支持 IEEE-754 单精度格式。

- 算术运算不支持 IEEE-754 去规范化数字。

- 使用 FPU 指令无法实现符合 IEEE-754 标准的余数函数,因为使用单独舍入指令序列时会产生多重舍入的影响。

- 融合乘法累加运算(MAC)不是 IEEE-754 标准的一部分。使用 FPU MAC 运算与使用单独的乘法和累加运算会产生不同的结果,因为在 MAC 运算结束时只对结果进行一次舍入。

- 由于不支持非正态数,因此无法完全符合 IEEE-754 标准。

- 如果没有 FPU,那么 FPU 指令将导致 UOPC(未执行操作码)陷阱。

9.2、符合 IEEE-754 标准

9.2.1、EEE-754单精度数据格式

单精度 IEEE-754 浮点格式有三个部分:符号位、8 位偏置指数和 23 位小数尾数(在第 22 位之前有一个隐含的二进制点)。对于普通数字,尾数在二进制点左侧有一个隐含的 1。下表显示了 IEEE-754 单精度格式的不同数字表示类型。表中

s = 位 [31]:符号位。

e = 位 [30:23]:偏置指数。

f = 位 [22:0]:尾数的小数部分。

IEEE-754单精度表示类型

IEEE-754 没有定义如何区分信号 NaN 和静默 NaN,但 bit[22] 已成为区分的标准方法。

注意:零的两个带符号值的处理方式总是相同的,除了不同的带符号零之外,不会产生不同的结果。

9.2.2、非正态数

算术运算不支持反常数。除 CMP.F 指令外,所有指令在计算前都会用适当符号的零替换去正态操作数。计算后,如果结果是一个反常规数,则用适当符号的零替换。

从概念上讲,IEEE-754计算的常规顺序为:

1. 计算结果无限精度。

2. 四舍五入为IEEE-754格式。

它被替换为:

1. 将所有非正常操作数替换为带符号的零。

2. 计算结果无限精度。

3. 四舍五入为IEEE-754格式。

4. 用带符号的零代替所有不正常的结果。

该程序对下溢有微妙的影响

只有 CMP.F 指令支持反常规数,该指令除了识别反常规操作数外,还对反常规数进行比较。

9.2.3、NaNs (Not a Number)

NaN(非数字)是 IEEE-754 标准中与数字不对应的比特组合。NaN 有两种类型:信号型和静默型。FPU 将信号 NaN 定义为位 22 = ‘0’,而静态 NaN 定义为位 22 = ‘1’。

当执行无效操作(包括带有 NaN 操作数信号的操作)时,FI 将被置零,并产生一个静态 NaN 作为浮点运算结果。静态 NaN 包含无效操作的起始信息;

IEEE-754 建议对静态 NaN 进行传播,因此接收静态 NaN 作为操作数的指令(无信号 NaN 操作数)的结果应为静态 NaN。FPU 不以这种方式传播静 NaN。有一个(或多个)静 NaN 操作数而无信号 NaN 操作数的操作结果始终是静 NaN 7FC00000H。

9.2.4、下溢

当浮点运算的结果太小而无法以浮点表示形式存储时,就会发生下溢。

IEEE-754要求在标识溢流前满足两个条件:

- 结果必须是 “极小 ”的。

- 如果结果不为零,且幅度小于 2-126(单精度),则为 “极小 ”结果。IEEE-754 允许在四舍五入之前或之后进行检测。

- 存储结果必须有精度损失。

精度损失可以通过两种方式检测:要么作为非规范化损失,要么作为不精确的结果。

当计算结果假定指数范围不受限制,但使用 23 个小数位四舍五入为归一化数字时,就会出现去规范化损失。如果必须对四舍五入后的结果进行去规范化处理才能符合 IEEE-754 格式,而去规范化后的结果与使用无限制指数范围的规范化结果不同,则会出现去规范化损失。

不精确的结果是指无限精确的结果与存储的值不同。

FPU在舍入和不精确结果之前确定微小性,以确定精度损失。

在FPU的情况下,即使不正常的结果也不会产生精度损失,因为它被替换为零,精度丢失并且必须标记下流。

因此,检测到的任何微小数字都必须导致准确性的损失,因为它要么是一个异常值,要么被替换为零,要么被四舍五入。因此底流检测可简化为单独的微小数检测;即,其大小< 2-126的任何非零的未整入数。

9.2.5、融合式 MAC

IEEE-754标准不支持mac (Fused multiply and accumulate operations)。使用FPU的MAC操作(MADD)。F和MSUB.F)可以从使用单独的乘法(mull .F)和累加(ADD.F或SUB.F)操作得到不同的结果,因为结果在MAC结束时只四舍五入一次。

9.2.6、Traps

当异常情况发生时,IEEE-754 允许选择性地提供同步陷阱。在这种情况下,算术运算返回的结果可能不同于 IEEE-754 的要求,以便将中间结果传递给陷阱处理例程。提供这些陷阱是为了帮助调试例程和操作。

FPU 陷阱是异步的,因此不符合 IEEE-754 陷阱标准。由于 IEEE-754 陷阱是可选的,因此不会造成任何不符合 IEEE-754 的情况。

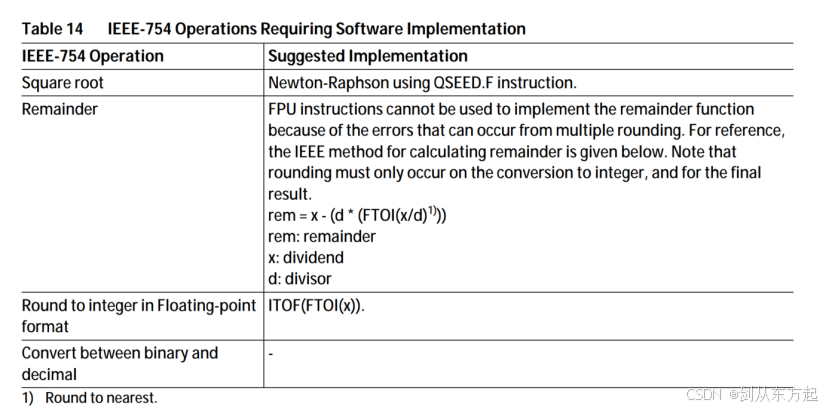

9.2.7、软件例程

符合IEEE-754要求的操作,但在FPU指令集中没有实现,详细请参见下图。

9.3、Rounding

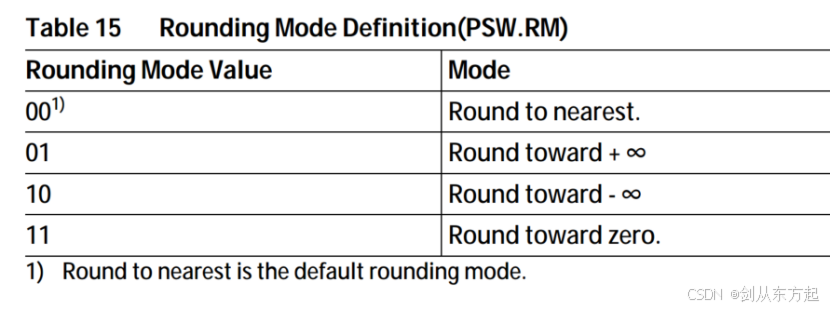

支持IEEE-754中指定的所有四种舍入模式。使用PSW (PSW[25:24])的RM字段来选择舍入方式。

IEEE-754 根据 “无限精确 ”结果的可表示结果定义四舍五入模式。无限精确结果是指在尾数和指数位数不受限制的情况下,运算计算出的数学精确结果。

四舍五入定义为返回最接近无限精确结果的可表示值。这是RTOS软件初始化任务时应该选择的默认舍入模式。

向+∞的四舍五入被定义为返回最接近且不小于无限精确结果的可表示值。

向-∞的四舍五入被定义为返回最接近且不大于无限精确结果的可表示值。

向零舍入定义为返回最接近且大小不大于无限精确结果的可表示值。它等价于截断。

舍入模式可以通过UPDFL(更新标志)指令来改变。

在每个相关的FPU指令结束时执行舍入,然后将所有不正常的数字替换为带有适当符号的0。

IEEE-754 没有规定将乘法和加法合并为一个运算的 MAC 指令(MADD.F 和 MSUB.F)。MAC 指令乘法部分的结果在 FPU 中用于加法运算之前不会舍入。相反,整个 MAC 以无限精度计算,并在加法运算结束时舍入。因此,MADD.F 指令的结果有可能与使用相同操作数的 MUL.F 和 ADD.F 指令的结果不同。

恢复舍入模式

在RET(从调用返回)指令上不恢复舍入模式。在RFE(从异常返回)指令或RFM(从监视器返回)指令上恢复舍入模式。

9.3.1、四舍五入:偶数

四舍五入 "的定义是返回最接近无限精确结果的可表示值。如果两个可表示值同样接近(即无限精确的结果正好是两个可表示值的一半),则返回 LSB(最小有效位)为零的那个值。这有时被称为四舍五入到最接近的偶数。

这通常很简单,但如果无限精确结果介于两个指数不同的可表示数之间,则总是选择指数较大的结果(其尾数的 LSB 为零)。例如,如果无限精确的结果是

1.111 1111 1111 1111 1111 1111 1000 0000 0000B * 20

这是两者的中间:

1.0000 0000 0000 0000 0000 000B * 21

和

1.111 1111 1111 1111 1111 1111B * 20

返回指数较大的结果。

9.3.2、四舍五入:异常和零替换

在计算之后,首先将结果四舍五入为IEEE-754可表示的数字,然后用适当的带符号的零替换可能出现的任何异常结果。这会产生一些看起来与直觉相反的结果。

考虑一个无限精确的计算结果,它介于最小的可表示的正IEEE-754正数(1.000…000 * 2-126)和最大的可表示的正IEEE-754正数(0.111…111 * 2-126)之间。

如果无限精确的结果更接近正常数,或者介于两者之间,那么结果必须四舍五入到正常数。

如果无限精确的结果更接近非正常值,则将结果四舍五入到非正常值。然后用零替换正常结果。

FPU 结构不能产生反常结果,但反常数的概念对 FPU 很重要。如果认为无限精确的结果应该四舍五入为最接近 FPU 的可表示数,即 (+1.000 ... 000 * 2-126) 或 (0),那就错了。这种实现方式意味着,介于 (+1.000 ... 000 * 2-126) 和 (+0.100 ... 000 * 2-126) 之间的所有未四舍五入结果都将四舍五入为可表示的最小 IEEE-754 正整数。

9.3.3、四舍五入到±∞:异形和零替换

下面的计算结果首先四舍五入到IEEE-754可表示的数字,然后用适当的带符号的零替换可能出现的任何异常结果。

根据 IEEE-754 对四舍五入模式的定义,在向 +∞ (- ∞) 舍入时,舍入结果不应小于(大于)无限精确的结果。但是,如果正数(负数)结果会被舍入为一个非正态数,那么它就会被替换为零。因此,返回的 0 结果小于(大于)无限精确结果。在这种情况下,返回的结果似乎与这些四舍五入模式的定义相矛盾。

9.4、异常处理

无效操作、溢出、除零、下流、不精确五种IEEE-754异常全部由FPU实现。当这些异常之一发生时,将断言PSW中相应的异常标志。

当发生异常时,可以选择采用异步trap,但是不实现符合IEEE-754的trap

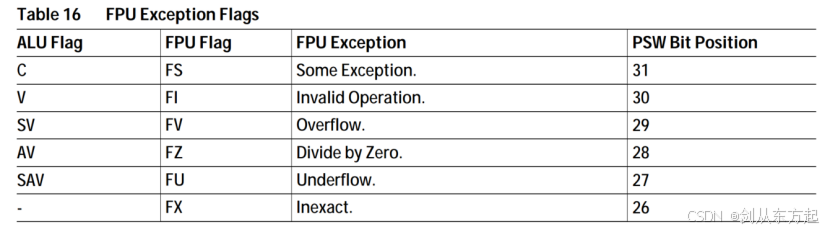

IEEE-754异常标志

IEEE-754 异常标志作为 PSW 寄存器的一部分存储,如下表所示。根据 IEEE-754 标准,每个位都具有粘性,因此 FPU 指令一般会在异常发生时断言这些标志位,而在异常未发生时不会否定这些标志位。UPDFL 指令可用于清除异常标志。

由于IEEE-754异常标志具有粘性,因此如果在执行最后一条指令之前断言了异常,则不可能判断最后一条指令上是否发生了异常。因此,实现了一个额外的、非粘性的异常标志(FS)来识别最后一个FPU指令是否导致了IEEE-754异常。

注意,用于存储异常标志的PSW位也用于存储ALU标志,如上表所示。当ALU指令更新这些标志时,相应的FPU异常标志将被覆盖并丢失。

以下条件适用于断言异常标志的所有FPU操作,UPDFL除外。

- 任何 FPU 操作只能断言 FI、FV、FZ 或 FU 中的一个异常标志。

- 只要 FI 和 FZ 被否定,任何操作都可以断言 FX。

- 当 FV 或 FU 被置信时,FX 也会被置信。

FS -一些例外

这个位不是粘性的,对于所有可能导致IEEE-754异常发生的指令都是断言或否定的。如果在该指令期间发生了任何IEEE-754异常(FI, FV, FZ, FU, FX),则也断言FS。

注:UPDFL可以断言IEEE-754异常而不断言FS。

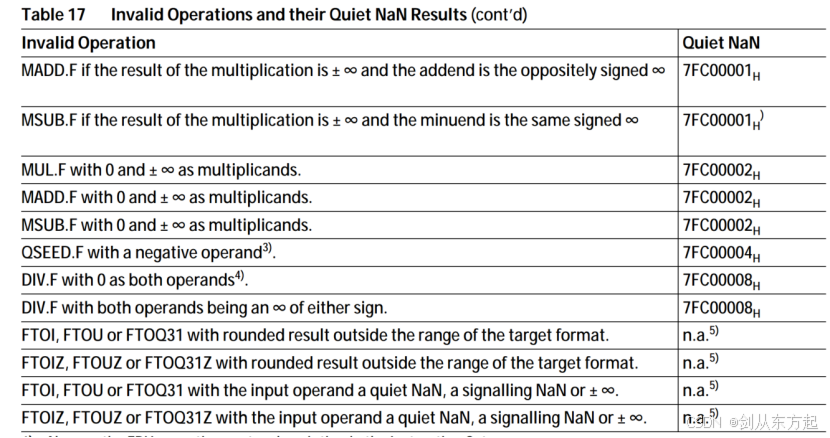

FI -无效操作

FI在三种情况下被断言:

当一个信号NaN(见NaN(非数字),第9-3页)是FPU指令的操作数时。

对于无效的操作,如QSEED。F(ª1/÷ x)为负数。

从浮点数转换为舍入结果超出目标范围的其他格式。

当产生浮点结果的指令将FI断言为信号NaN或无效操作的结果时,结果是一个安静的NaN。

1) 另请参阅指令集中的 FPU 运算语法说明。

2)以任何 NaN 为操作数的算术运算结果会产生静 NaN (7FC00000H)。只有当这些 NaN 中的一个发出信号时,FI 才会

。参见 NaNs(非数字),第 9-3 页。

3)-0 不是负数,因此 -0 的 QSEED.F 是 -∞

4)0/0 被定义为无效操作 (FI),而不是除以零 (FZ)。

5)结果不是浮点格式,因此不可能是静态 NaN。请参阅指令说明,了解结果应该是什么。

FV - Overflow

对于返回浮点结果的操作,FV标志的设置如IEEE-754所述;当目标格式的最大有限数的大小超过了四舍五入的浮点结果时,指数范围是无界的。

返回的结果由舍入模式和未舍入结果的符号决定:

- 四舍五入后,所有溢出数都归零到无穷大,并保留未四舍五入结果的符号。

- 四舍五入为零,将所有溢出都转为格式中最大的有限个数,结果的符号不四舍五入。

- 向负无穷大舍入会将正溢出带到格式的最大有限数值,并将负溢出带到负无穷大。

- 向正无穷大取整会导致负溢出到格式的最大有限负数,正溢出到正无穷大。

当溢出被标记时(断言 FV),返回的结果不可能与未舍入的结果完全相等。因此,只要断言 FV,也就断言 FX。

FZ -除以0

如果除数操作数为零,而被除数操作数为有限非零数,则由DIV.F设置FZ标志。结果是一个由通常规则决定的带符号的无穷。

要注意的是

- 0/0 被定义为无效运算,因此断言 FI 而不是 FZ。

- 所有以± ∞为操作数的算术运算都被定义为精确运算,但无效运算除外,在无效运算中,FI 被断言。因此,对于 ± ∞/ ± 0,FZ 不会被置信,结果将返回适当符号的 ∞,而不会出现其他异常。

FU -下溢

正如在第9-4页的Underflow中所讨论的,当未舍入的结果小于最小可表示的正数(2-126)时,检测到下流,因此断言FU。

Q31TOF指令可以引起下流,也可以引起算术指令ADD.F、SUB.F、MUL。F,MADD。F, MSUB。F和DIV.F。

由于FPU处理非正常数字的方式,标记下流的指令返回结果变得复杂。

FX-不准确

如果操作的舍入结果不完全等于未舍入结果,则设置FX标志。

传递的结果是四舍五入的结果,除非在此指令期间也发生了溢出(FV)或下溢出(FU),此时遵循溢出或反规范化返回结果规则。

9.5、异步的陷阱

FPU可以配置为当FPU指令导致IEEE-754异常时向TriCore内核发送trap信号。产生的trap是协处理器异步错误(CAE), trap类4 - tin4。FPU CAE陷阱不应与IEEE-754可选的同步异常陷阱混淆,后者允许软件例程纠正算术溢出或下溢。

FPU CAE陷阱仅用于调试目的,对异常指令或可能在FPU内执行的任何其他指令都没有影响。引起CAE陷阱的异常指令返回的结果与不采取陷阱时返回的结果相同。指令完成后发出CAE陷阱信号。

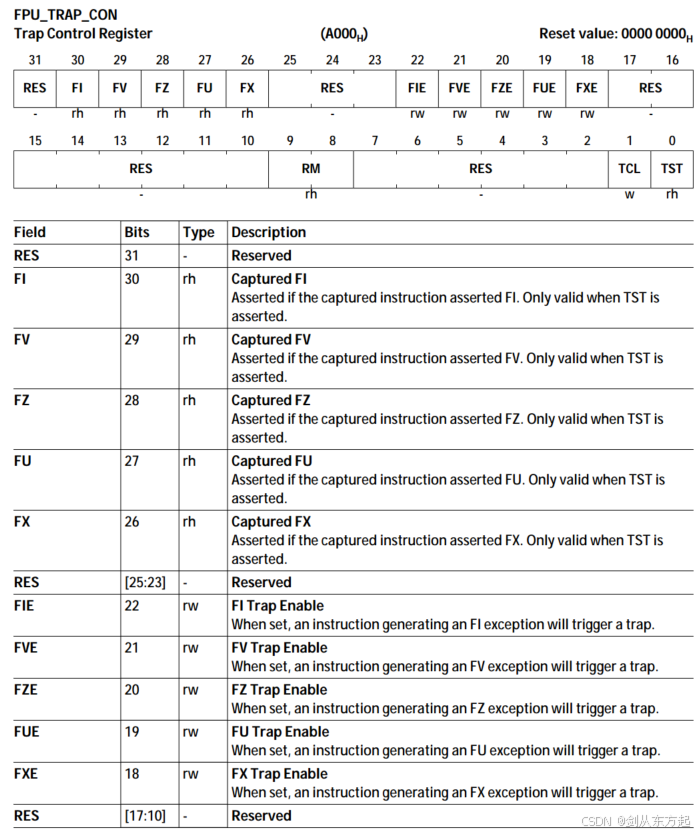

导致FPU CAE trap产生的具体异常条件由软件控制。要为特定异常类型启用trap生成,必须断言FPU_TRAP_CON寄存器中适当的启用位(FIE, FVE, FZE, FUE或FXE)。可以设置任意数量的这些使能位,以便在发生任何异常时采取trap。外汇是一个经常发生的情况,在启用这个陷阱时应该小心。

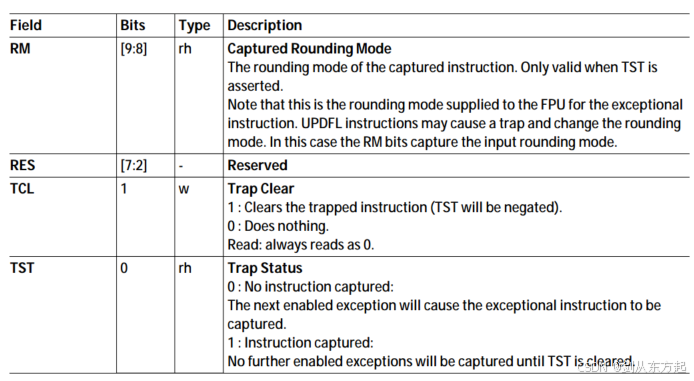

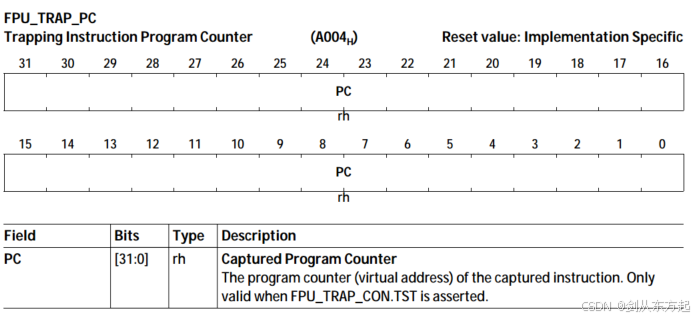

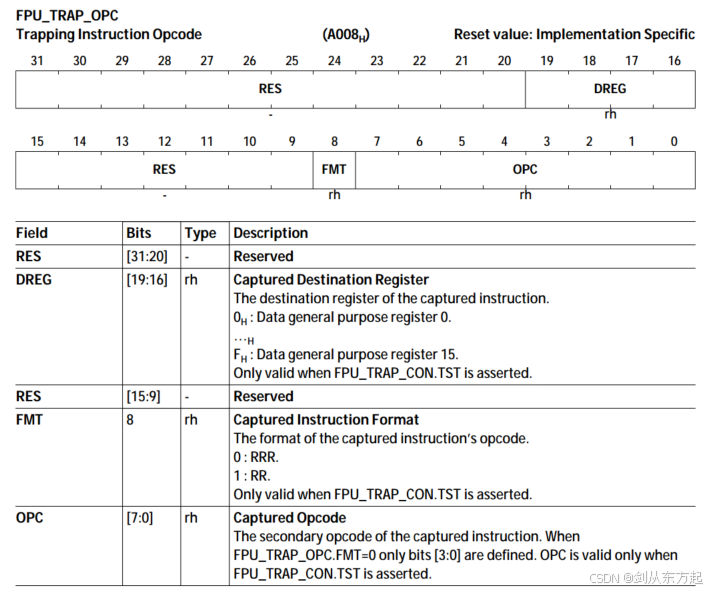

当一条指令引起了一个已启用的异常时,有关该异常指令的信息,包括指令PC、操作码和源操作数,将被捕获到FPU特殊功能寄存器中。同时,在FPU_TRAP_CON寄存器内设置Trap状态标志(TST),表示FPU Trap捕获寄存器的内容是有效的。另外,只要FPU_TRAP_CON。TST保持不变,抑制FPU CAE trap的进一步产生。这避免了从同一个根源问题产生多个陷阱和原始信息丢失。一旦trap处理程序询问FPU以确定trap的原因,FPU_TRAP_CON。可以清除TST位以启用进一步的陷阱。

引起陷阱的异常指令的结果不存储在FPU寄存器中。结果将在指令的目标寄存器中可用,只要它在异步陷阱触发之前没有被覆盖。

9.6、FPU CSFR寄存器

FPU CSFR寄存器用于存储引起陷阱的指令的详细信息。

FPU Trap Control Register

FPU捕获指令程序计数器寄存器

FPU_TRAP_PC

FPU捕获指令操作码寄存器

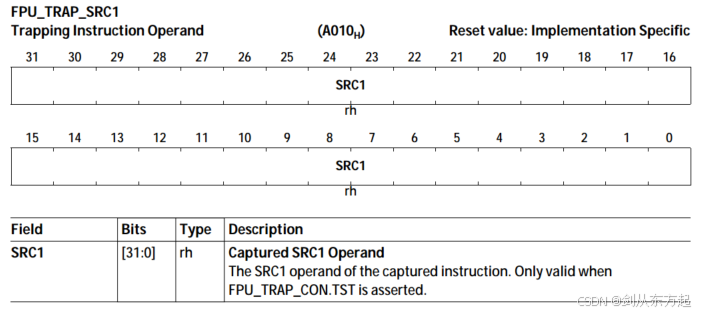

FPU捕获指令操作数SRC1寄存器

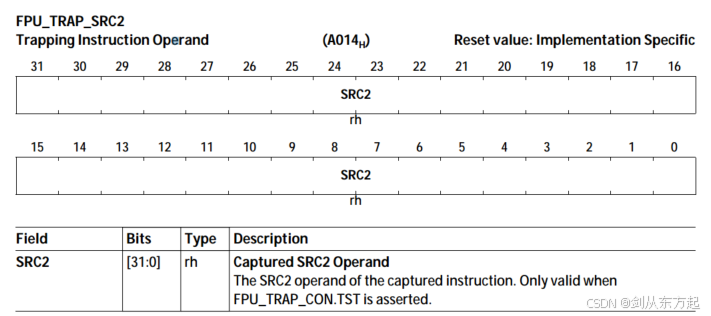

FPU捕获指令操作数SRC2寄存器

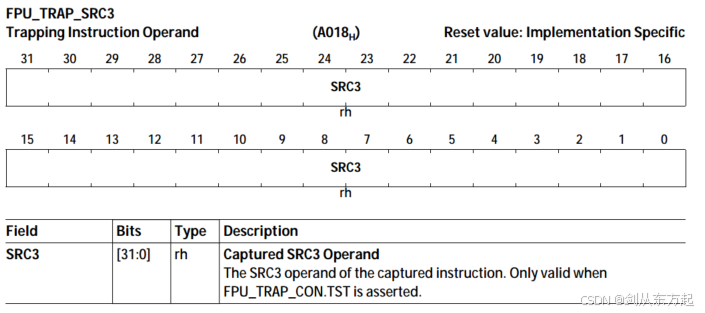

FPU捕获指令操作数SRC3寄存器

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?