1.什么是协处理器?

协处理器co-processor:顾名思义,协助主处理器完成计算处理的工作。

2.16个协处理器(CP0-CP15)

arm32一共支持16个协处理器,从cp0-cp15共16个,为何强调arm32,从arm-v8架构引入了aarch64的架构,因为在arm64中,弱化了协处理器的概念(注:arm64、aarch64同一个说法)

CP15协处理器:arm中重要的协处理器,mmu、cache等都是由其所配置。

CP14协处理器:debug调试使用。

CP10 、CP11协处理器:浮点与向量处理。

CP8 9 12 13预留给ARM厂家。

CP0-CP7预留给第三方厂家使用。

3.CP15协处理器介绍

在此主要介绍CP15协处理器,cp15是一个寄存器组,主要管理mmu 、cache、以及系统控制等,ARM对CP15主要通过mrc读指令 mcr写指令进行配置,以下为arm的描述。

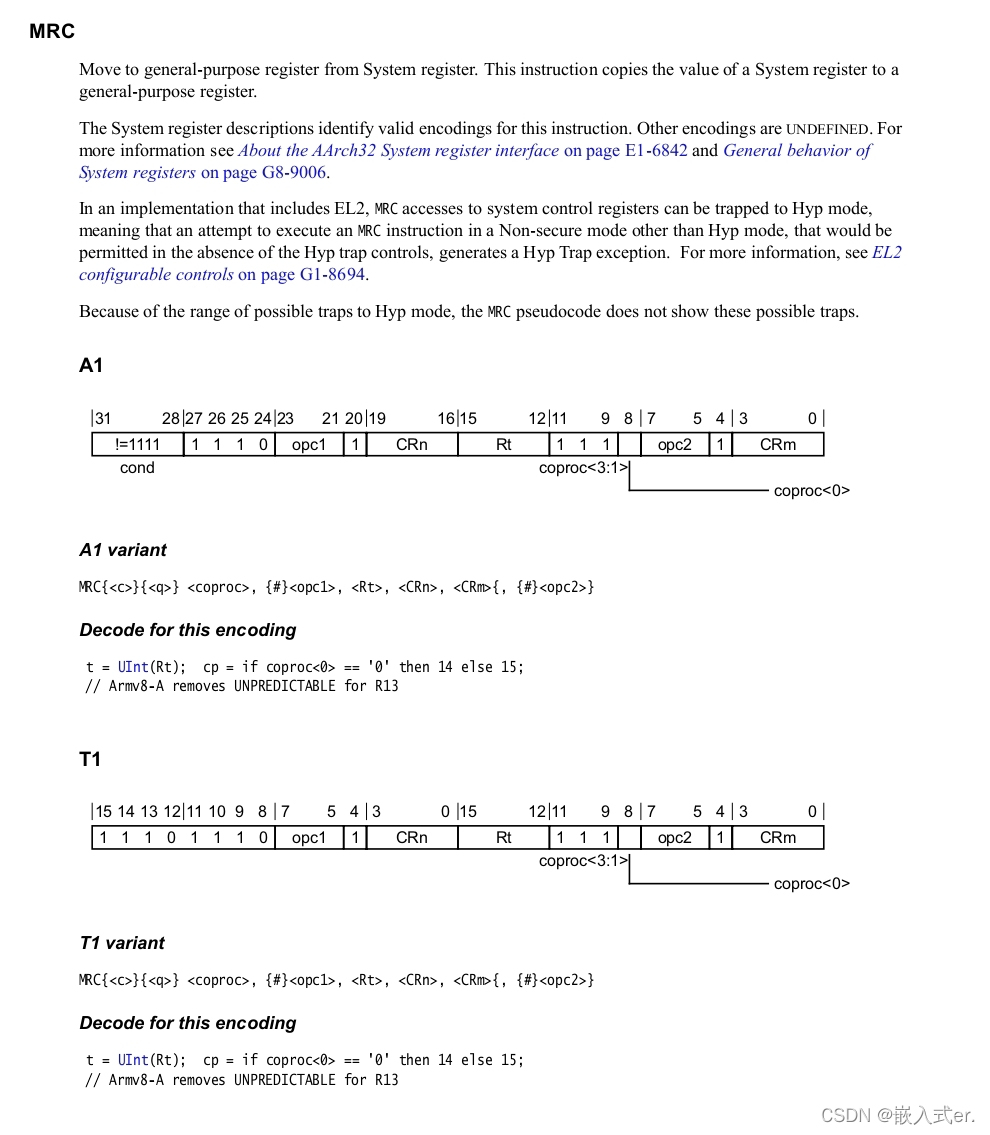

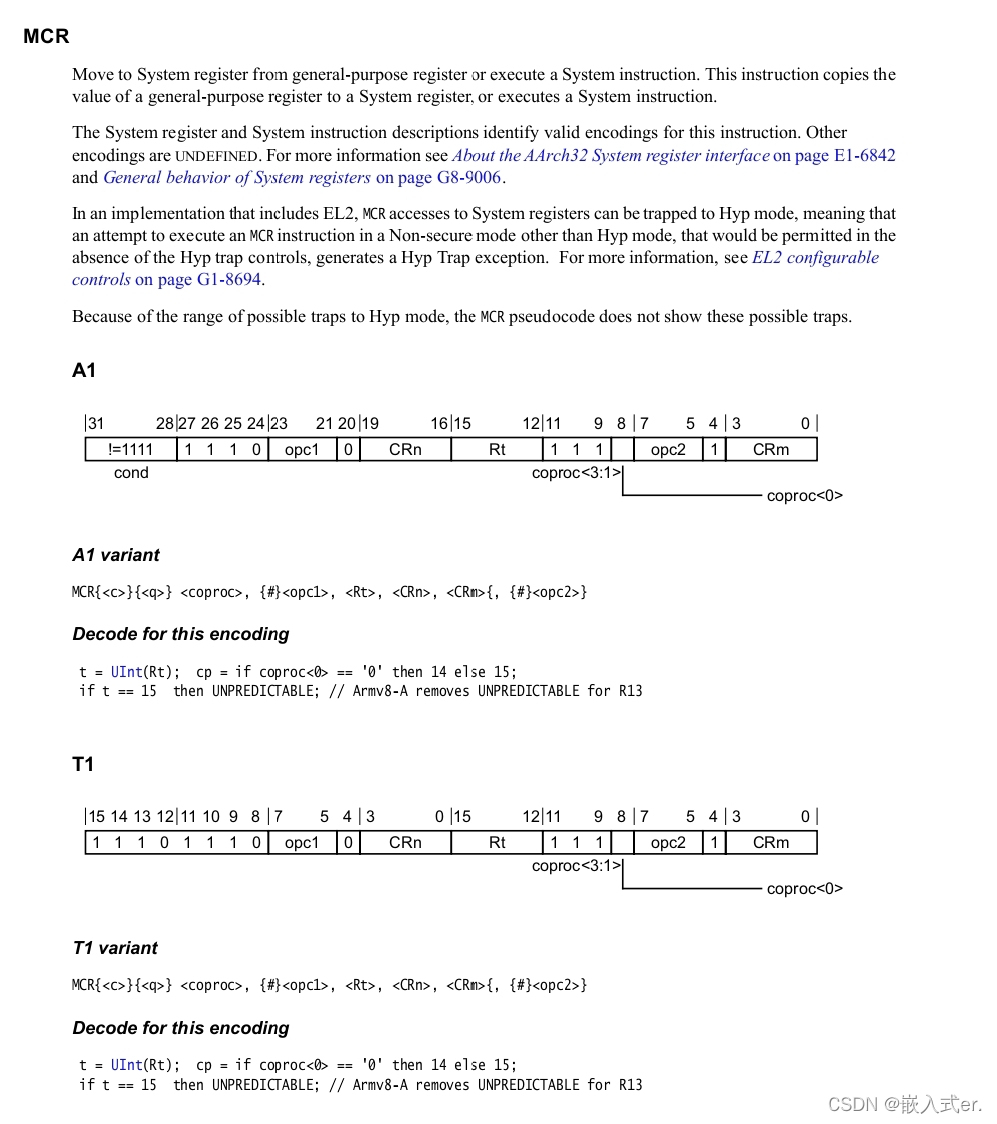

协处理器的指令操作MRC MCR,其中A1为A32指令集、T1为thumb指令集,在此主要说明A32指令集。

//eg:

MRC p15, 0, <Rt>, c1, c0, 0

// Read System Control Register

MCR p15, 0, <Rt>, c1, c0, 0

//Write System Control Register

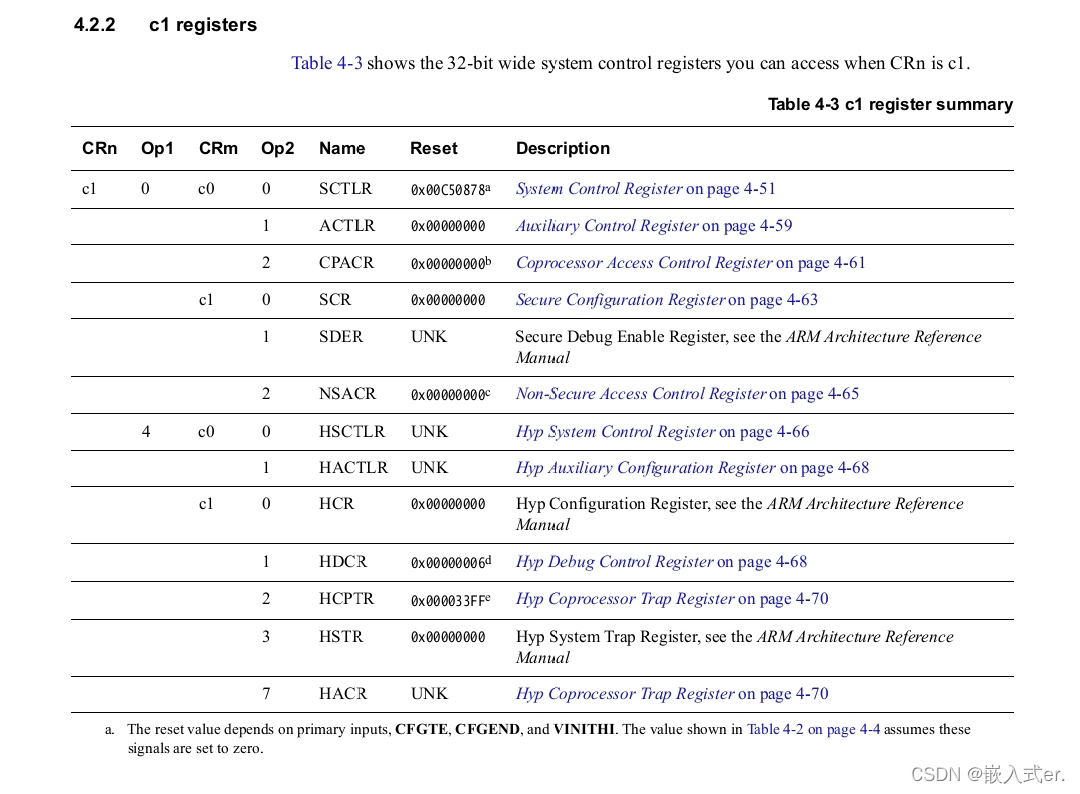

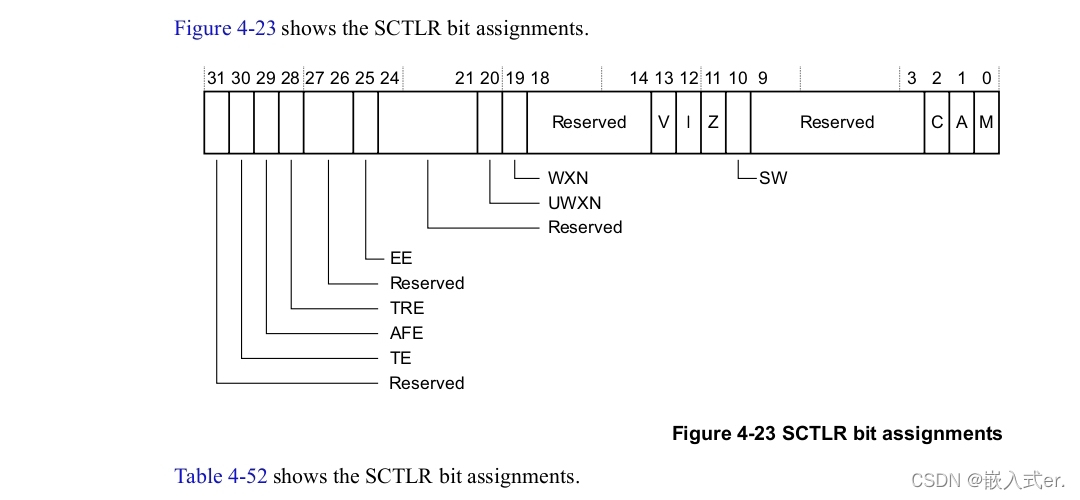

其中c1 c0以及编号共同组成SCTLR寄存器,其中Rt为通用寄存器,通过MRC MCR实现对此寄存器的读写操作。

4.u-boot中的cp15使用

在armv7的start.s中可以看到cp15使用的身影。u-boot下载http://www.denx.de/wiki/U-Boot/u-boot-2020.07-rc3.tar.bz2

代码路径:u-boot-2020.07-rc3\arch\arm\cpu\armv7\start.S

/*

* disable MMU stuff and caches

*/

mrc p15, 0, r0, c1, c0, 0

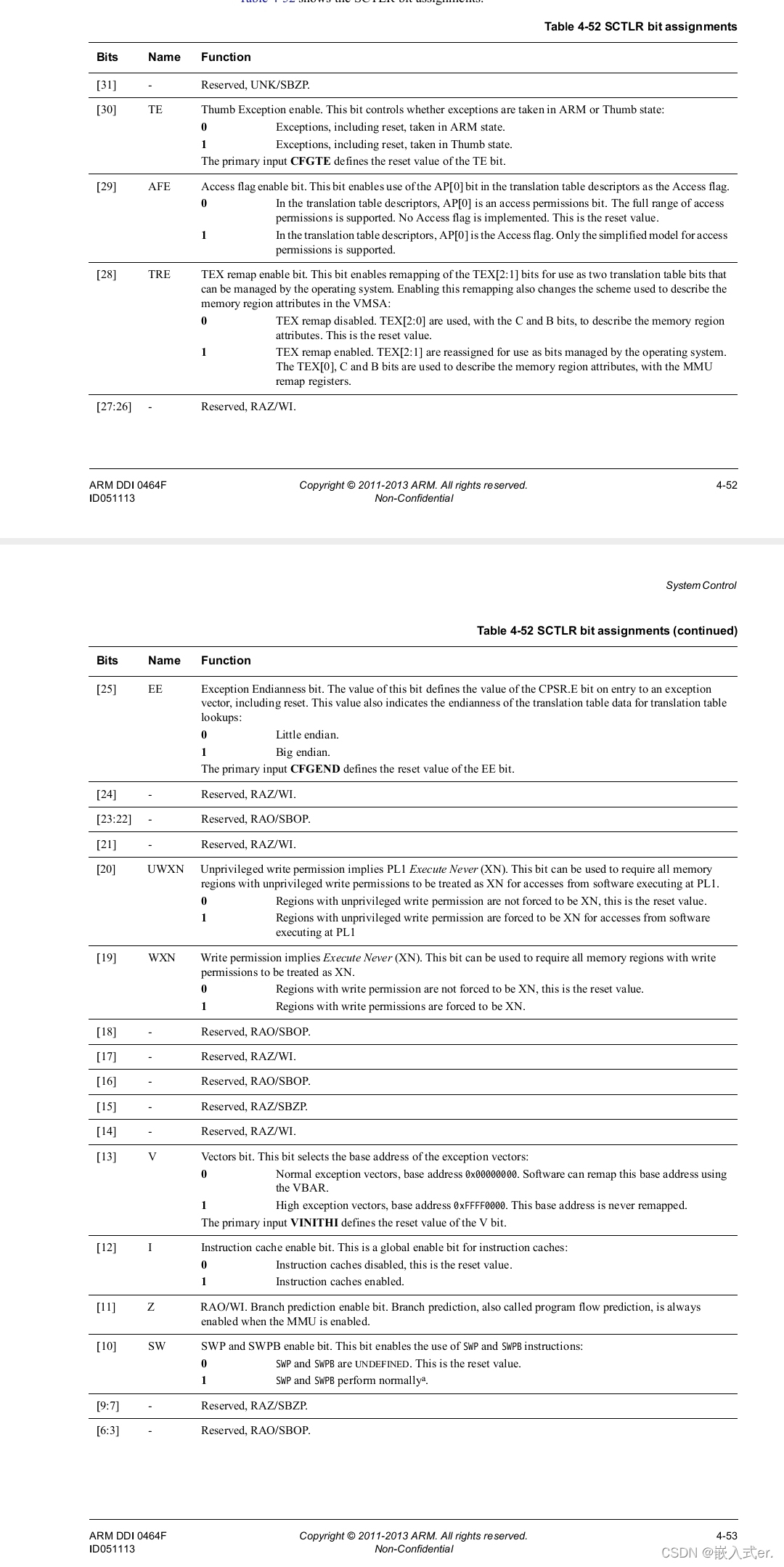

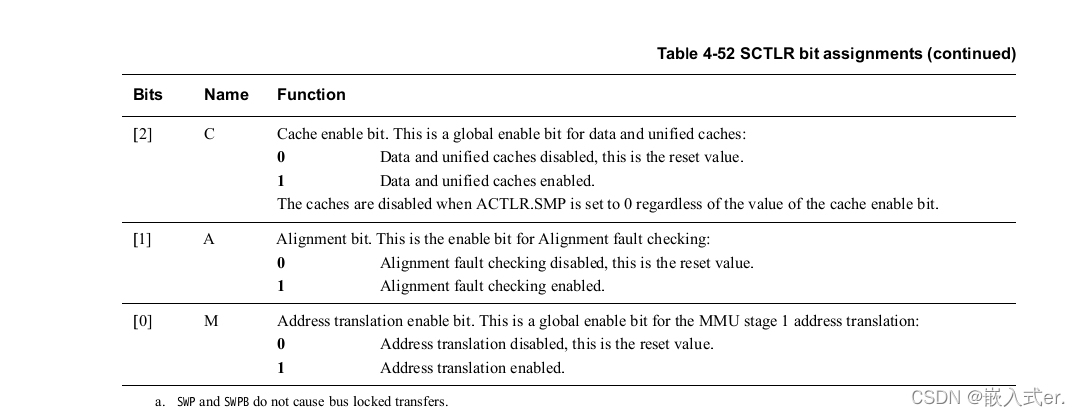

bic r0, r0, #0x00002000 @ clear bits 13 (--V-)

bic r0, r0, #0x00000007 @ clear bits 2:0 (-CAM)

orr r0, r0, #0x00000002 @ set bit 1 (--A-) Align

orr r0, r0, #0x00000800 @ set bit 11 (Z---) BTB

#if CONFIG_IS_ENABLED(SYS_ICACHE_OFF)

bic r0, r0, #0x00001000 @ clear bit 12 (I) I-cache

#else

orr r0, r0, #0x00001000 @ set bit 12 (I) I-cache

#endif

mcr p15, 0, r0, c1, c0, 0

其中r0为通用寄存器;

通过查表可以看出使用的是SCTLR寄存器;

其中mrc实现了读取协处理器cp15的SCTLR寄存器的值—>r0通用寄存器中;

bic为位清除指令,orr为位或指令,通过对r0的数据操作;

最终通过mcr将r0配置到SCTLR中;

本文介绍了ARM32架构中的CP15协处理器,它是管理MMU、Cache和系统控制的关键组件。通过MRC和MCR指令进行配置,例如在u-boot的启动代码中用于管理CPU状态和缓存设置。此外,还探讨了CP15在u-boot中的实际使用,如禁用MMU和缓存的操作。

本文介绍了ARM32架构中的CP15协处理器,它是管理MMU、Cache和系统控制的关键组件。通过MRC和MCR指令进行配置,例如在u-boot的启动代码中用于管理CPU状态和缓存设置。此外,还探讨了CP15在u-boot中的实际使用,如禁用MMU和缓存的操作。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?