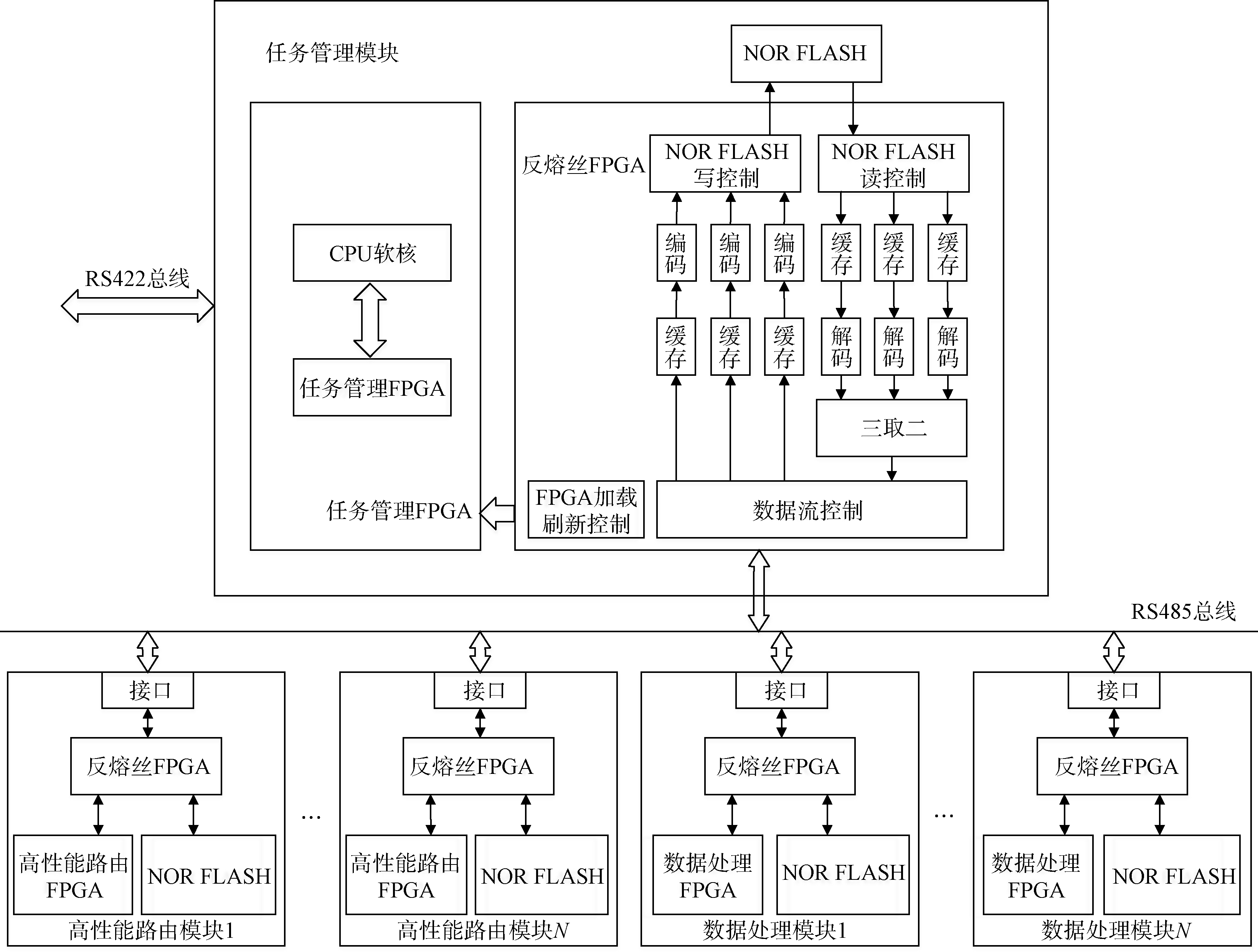

某航天器星载设备在轨重构系统的功能框图如下图所示,在轨重构系统集成在任务管理模块、高性能路由模块及数据处理模块中。

该在轨可重构系统具备可扩展、高可靠性等特点。

该航天器在轨重构控制处理单元由任务管理FPGA的内嵌CPU软核实现。

任务管理FPGA属于SRAM型FPGA,能够嵌入CPU软核,CPU软核开发过程灵活,能够与外围的FPGA逻辑进行灵活的信息交互,可以替代DSP 或CPU等微处理器执行核心的软件控制功能。

任务管理模块为在轨可重构主处理单元, 由任务管理FPGA(SRAM 型FPGA)、反熔丝FPGA 和NOR FLASH 芯片构成。

高性能路由模块、数据处理模块等为在轨重构从处理单元, 由SRAM 型FPGA、反熔丝FPGA 和

NOR FLASH芯片构成。RS 422 总线实现重构数据及重构指令的接收,内部RS 485 总线实现主处

理单元和从处理单元的数据及指令交互。

对于任务管理主处理单元,通过RS 422 总线接收重构数据并校验完成后, 通过任务管理模块的反熔丝FPGA写入NOR FLASH芯片中。

任务管理模块通过RS 485 总线与路由模块、数据处理模块传输上注重构数据、重构指令并返回遥测信息。

对于从处理单元,将重构数据经RS 485 总线发送到指定模块,由目标模块中的反熔丝FPGA 接收并写入NOR FLASH芯片中。

主、从处理单元中的反熔丝FPGA实现的功能是相同的, 功能框图如上图所示。

本型号采用ACTEL FPGA 实现反熔丝FPGA 的功能,ACTEL FPGA对单粒子翻转具有免疫功能,可以保证重构数据接收、处理的可靠性。

ACTEL FPGA 将重构数据复制三份,经编码、缓存后分别写入NORFLASH 的三块地址中。上电或接收到重加载指令后,ACTEL FPGA 会分别从三块地址中读取重构数据,经缓存、解码、三取二判别后写入SRAM型FPGA 的配置管脚中对其进行重构。

该航天器采用的编译码方式为EDAC 扩展汉明码,采用(8,4)码字,在纠1 bit 错误的同时能检测2 bit 错误,可以解决航天器上存储芯片因单粒子翻转效应导致的单比特误码错误,最大程度地保证重构数据存储的可靠性。

在轨实施重构过程如下:

- 根据在轨任务升级需求或在轨发现的故障隐患,对SRAM型FPGA逻辑重新进行设计,并在地面进行测试验证;

- 将升级后的可执行程序转换成上注配置数据的格式;

- 向航天器发送重构指令及重构数据,重构指令指定需要升级的目标模块地址;

- 航天器设备通过RS 422 总线接收重构指令及重构数据,并通过内部总线将相应的数据传递给目标模块,目标模块中的反熔丝FPGA对重构数据进行接收、解析、校验,并存储到相应的NORFLASH 芯片中,重构数据存储时采用EDAC 扩展汉明码及三模冗余的方式保证数据的可靠性;

- 停止目标模块SRAM型FPGA 的工作,启动配置模式,将重构数据加载至目标FPGA,重构完成后通过内部总线返回配置成功遥测信息。

342

342

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?