1、处理器

冯·洛伊曼1964年提出电子数字计算机:

①使用二进制 (第一台ENIAC使用十进制,比较复杂)

②提出存储程序工作原理

1、 运算器ALV:在控制器的控制下完成算术运算和逻辑运算,由算术逻辑运算部件ALU、累加器、通用寄存器组成

2、 控制器:中央处理器核心,控制并协调计算机各部件自动切连续地执行各条指令,由指令寄存器IR、指令译码器ID、定时与控制电路、程序计数器PC以及冲源、中断组成

3、 存储器:存放程序和数据,程序是计算机操作的依据;数据时计算机操作的对象。由存储体、地址译码器、读写控制器、地址总线、数据总线组成

4、输入装置

5、输出装置

中央处理器:计算机的控制、运算中心,通过总线和其它设备联系。嵌入系统中,外设常常直连到处理器外部i/o脚的中断脚上。运算器位数,即运算器一次能对多少位的数据做加法,是衡量中央处理器的一个重要指标。

1、 指令寄存器:即将执行的操作码表存放在这

2、 指令译码器:将操作码解码,告诉中央处理器该做什么

3、定时与控制电路:产生各种微操作控制型号

4、 程序计数器:存放下一条指令的地址

5、 标志寄存器:记录运算器的重要状态或特征,典型应用是作为跳转指令的判断条件

6、 堆栈和堆栈指针:堆栈可以是一组寄存器或在存储器内的特定区域。堆栈顶部指针称为堆栈指针

寄存器组:通用寄存器功能由程序指令决定,最常见的应用是放置计算的中间结果,减少对存储器的访问次数。通常寄存器的宽度是和运算器的位数相一致的。

为了使得计算机各部件同步工作,计算机中都有一个脉冲源,通常是晶振。这个脉冲源产生主振脉冲,主振脉冲的时间间隔为主振周期,即时钟周期。中央处理器执行指令的时间(包括取址)为指令周期。CPU 周期也称为机器周期,一般是从内存中读一个指令的最短时间。

CPU 执行指令的各个微操作遵循的时间顺序称为时序

组合逻辑控制和微过程控制是两种基本的控制方式。

组合逻辑控制器是使用专用门的逻辑电路:硬件接线控制和可编程逻辑阵列两种

微过程控制:为提高控制的灵活性,许多中央处理器采用微过程控制的控制方法

2、输入/输出及其控制

输入/输出控制器协调和控制数据的输入/输出,具体功能:缓冲锁存数据、地址译码、传递命令、码制转换、电平转换等

(1) 数据寄存器:CPU 或外设数据的缓冲。

(2) 状态寄存器:向中央处理器指示控制器和外设的状态。

(3)控制寄存器:由中央处理器写入该输入/输出控制器的识别指令,指示输入/输出控制器去和外设交互,将数据寄存器的内容写入外设,或者将外设的数据写入数据寄存器,并将此过程的状态写入状态寄存器。

(4)控制电路:是输入/输出控制的核心,负责输入/输出控制器的行为。

外设识别:独立编址方式、统一编址方式

外设访问:程序查询方式、中断方式

串行接口有两种方式:同步通信和异步通信

3、总线结构、指令流和数据流

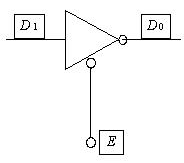

三态门的结构

和 0、1 两个状态的门电路相比,三状态增加了一个高阻状态,又称为“悬空”、“断开”等。这个状态实际上意味着什么也得不到,实现三状态的逻辑电路称为三态门。

E 对于能否输出显得非常重要,在作为总线结构的关键原件时,就称为“总线有效信号”

总线Bus:计算机CPU、内存、输入、输出设备等各功能部件间的传递信息的公用通道,由导线组成的传输线束

处理器内部总线:内部各部件间信息传送线。如寄存器间

片总线C-Bus:把不同芯片连接在一起构成特定功能模块的信息传输通路----部件内总线,如显卡

内总线I-Bus:系统总线,模块间信息通路,如:cpu与存储器间

外总线E-Bus:通信总线,计算机系统间或与其它系统间的信息传输通路

系统总线按功能分为:

数据总线:传递数据信息,双向三态形式的总线。中央处理器通过数据总线和主存、外设交换

数据。

地址总线:专门用来传送地址,三态门控制的单向数据信道。8位微机地址总线16位,最大可寻址空间为2^16=64kb16位微机总线20位最大可寻址空间为 2^20=1MB。由中央处理器“点名”取数的位置

控制总线:传送控制信号和时序信号。如读/写信号、中断请求、复位等信号

总线控制方式分为集中式控制和分布式控制

1.链式查询方式

2.计数器定时查询方式

3.独立请求方式

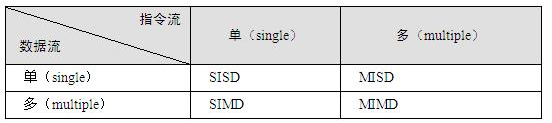

指令流:机器执行的指令序列。

数据流:由指令流调用的数据序列,包括输入数据和中间结果。

1.根据多倍性的分类

按照计算机同时处于一个执行阶段的指令或数据的最大可能个数,人们把计算机分成 4种

单指令流单数据流SISD:传统的顺序执行的单处理器计算机

单指令流多数据流SIMD:复制多个操作,将其打包在大型寄存器的一组指令集,以同步方式在同一时间执行同一条指令

多指令流单数据流MISD:n个处理单元按n个不同指令的要求处理同一数据流及其中间结果

多指令流多数据流MIMD:全面的并行处理,多个处理单元根据不同的控制流程执行不同的操作,处理不同的数据

2.按照程序流程机制的分类

1) 控制流计算机

2) 数据流计算机

3) 归约机

4、存储器系统

存储器体系包括寄存器、Cache、主存储器、磁盘存储器、光盘存储器、磁带存储器等。

存储器系统的性能主要由存取时间、存储器带宽、存储器周期和数据传输率等衡量。

(1)顺序存取:存储器的数据以记录的形式进行组织。对数据的访问必须按特定的线性顺序进行。

(2)直接存取:与顺序存取相似,也使用一个共享的读写装置对所有的数据进行访问。但是每个数据块都拥有唯一的地址标识,读写装置可以直接移动到目的数据块所在的位置进行访问。

(3) 随机存取:存储器的每一个可寻址单元都具有自己唯一的地址和读写装置,系统可以在相同的时间内对任意一个存储单元的数据进行访问,而与先前的访问序列无关。主存储器采用随机存取的方式。

(4) 相联存取:也是一种随机存取的形式,但是选择某一单元进行读写取决于其内容而不是其地址。与普通的随机存取方式一样,每个单元都有自己的读写装置,读写时间也是一个常数。使用相联存取方式,可以对所有的存储单元的特定位进行比较,选择符合条件的单元进行访问。为了提高地址映射的速度,Cache 采取相联存取的方式。

CPU 需要访问的内容大多都能在 Cache 中找到(称为访问命中,hit),则可以大大提高系统性能

如果以 p 代表对 Cache 的访问命中率,t1 表示 Cache 的周期时间,t2 表示主存储器

周期时间。以读操作为例,使用“Cache+主存储器”的系统的平均周期为 t3,则 t3=p× t1+(1–p)× t2。其中,(1–p)又称为失效率(未命中率)

若命中,则直接对 Cache 进行访问。这个过程称为 Cache 的地址映射。常见的映射方法有直接映射、全相联映射和组相联映射。

Cache 的替换算法主要有以下 3 种。

(1) FIFO 算法:把一组中最先调入 Cache 的字块替换出去,实现较简单。

(2) LRU(Least Recently Used)算法:把一组中近期最少使用的字块替换出去,命中率较高。

(3) RAND 算法:用随机数发生器产生需替换的字块号,因为不能很好反映程序局部性,命中率较低。

各寄存器彼此分离,CPU 不能直接完成将寄存器 R0 的内容传送到寄存器 R1 中的操作

虚拟存储器:调度方式:页式调度、段式调度、段页式调度。地址变换:全联想变换、直接变换、联想变换

相联存储器:按内存访问存储器,不根据地址而根据存储内容来存取的存储器高速缓冲存储器Cache:位于CPU与内存之间,读写速度比内存更快

随机访问存储器:存储单元的内容可按需随意取出或存入,且存取速度与存储单元的位置无关

源码:数值前加符号位,0为正,1为负

反码:正数反码为本身,负数反码为绝对值逐位取反。0为正,1为负

补码:正数补码为本身,负数补码符号位1,其余为绝对值按位取反,然后加1—符号一起计算,高

位溢出

移码:是符号位取反的补码,一般做浮点数的阶码

流水线:将重复过程分解为若干个子过程,前一个子过程为下一个子过程创造执行条件,每个子过程可同时进行。时间最长的一段是瓶颈,称为“流水线的周期”

RISC精简指令集计算机:精简指令、采用大量寄存器、采用缓存–主机–外存三级存储结果

CISC复杂指令集计算机:简化编译器结构,减少编译代码中指令数目

吞吐量:单位时间内中央处理器从存储设备读取、处理、存储信息的量。受以下影响:

1.存储设备读取速度

2.CPU性能

3.系统结构

平均故障时间等于失效率的倒数:1/(500元件*10-7)=2*104

立即数寻址方式:操作数在指令中,紧跟在操作码之后

寄存器寻址方式:操作数在CPU的内存寄存器时,可在指令中指出寄存器名:

直接寻址:指令中地址即为操作数的有效地址

寄存器间接寻址:操作数地址在寄存器

寄存器相对寻址:以指定的寄存器内容,加上指令中位移量,并以一个寄存器为基准作为操作数的地址

基址加变址寻址:把一个基址寄存器BX或BP的内容加上变址寄存器SI或DI 的内容,并以一个段寄存器作为地址基准作为操作数的地址

相对基址加变址寻址:在基址加变址寻址的方式基础上增加一个位移量

磁盘计算

(1) 总磁道数 = 记录面数×磁道密度×(外直径–内直径)/2

(2) 非格式化容量 = 位密度×3.14×最内圈直径×总磁道数

(3) 格式化容量 = 每道扇区数×扇区容量×总磁道数

(4) 平均数据传输速率 = 每道扇区数×扇区容量×盘片转速

bit = 0/1

8位:bit=1字节:byte

1024B=1KB

压缩算法(compaction algorithm)指的就是数据压缩的算法,主要包括压缩和还原(解压缩)的两个步骤

无损压缩:能够无失真地从压缩后的数据重构,准确地还原原始数据。

有损压缩:有失真,不能完全准确地恢复原始数据,重构的数据只是原始数据的一个近似

字长:指参与一次运算的数的位数,主要影响计算机精度和运算速度,8的倍数如32、64位

主频:CPU的时钟频率,单位MHz

存储周期:存储器执行一次完整的存取操作所需时间

CPU中行指令的地址,访问内存时, 首先将内存地址送入存储器地址寄存器(MAR) 中, 向内存写入数据时待写入的数据要首先放入数据寄存器(MDR) 中。程序中的指令一般放在内存中, 执行时首先要访问内存取得指令并保存在指令寄存器(IR)中。

串联系统可靠度等于各系统可靠度乘积

计算机软件:为运行、维护、管理及应用计算机编写的所有程序和数据的总和。

1.系统软件:操作系统、数据库管理系统、语言处理系统、网络系统、标准程序库、服务性程序。

2.应用软件:通用、专用软件

1191

1191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?