前言

在上一期中,我们讲解了verilog的基础语法。本文主要整理intel FPGA创新中心,FPGA初级工程师考试,verilog中wire数据类型考试的重点、难点。请同学们做好笔记!

一、wire到底是什么?

1.模块中wire连接输入输出

verilog中的wire数据类型,可以看成是单向的物理连线。我们来看模块中,通过wire连接输入输出的情况。如下图1所示,通过单向的wire,从模块定义的入口,流向模块定义的出口。

现在我们通过代码,实现图1中的连线,输入端in和输出端out,都没有声明数据类型,那么就默认其为wire数据类型。out=in表明:in作为驱动端,驱动着out改变信号,这就是连续赋值的物理意义。

module top_module( input in, output out );

assign out = in;

endmodule

对应生活中的例子:你有两根线,现在你想把它们连接起来,但是线的距离不够打上一个结。于是,你需要一根额外的线,将它们连接起来。

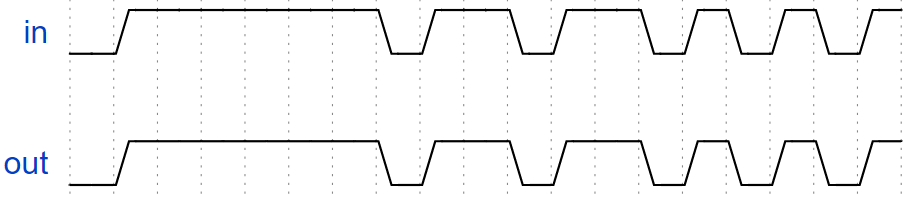

我们来看看波形图,输入端作为驱动端,驱动着输出端改变。一般情况下,输入端需要有驱动源,比如时钟信号,输出随输入进行改变,如下图3。

通过观察仿真信号,in和out信号是同步的,可以总结连续赋值:只要右边表达式任一个变量有变化,表达式立即被计算,计算的结果立即赋给左边信号。

2.wire的位宽

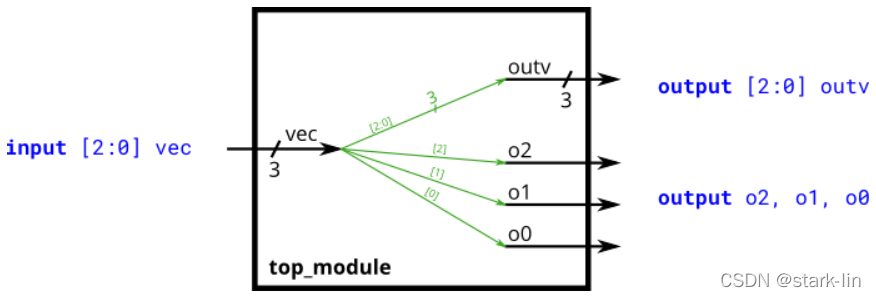

在verilog中不申明位宽时,默认wire的位宽为1位。图4模块的输入是一个3位宽度的wire类型数据,从低位的0到高位的2,现在要把vec连续赋值给输出端outv,以及分别把vec[0]、vec[1]、vec[2]连续赋值给三个1位的输出端o0、o1、o2。

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 );

assign outv = vec;

assign o0 = vec[0];

assign o1 = vec[1];

assign o2 = vec[2];

endmodule

从波形图中,vec是使用的十进制表示,vec与outv波形图肯定是一致的。我们再看看vec为2的时候o0、o1、o2情况是否正确,vec为2时的二进制为010,所以对应的o0为0、o1为1、o2为0,所以仿真的波形是没有问题的。

3.申明一个wire

既然我们知道了wire数据类型以及wire的位宽,现在看看申明不同的wire。

wire [7:0] w; // 8-bit 位宽的wire,没有指明是端口。

output wire [0:0] y; // 1-bit 位宽的wire,指明为输出端口。

input wire [3:-2] z; // 6-bit 位宽的wire 指明为输入端口,负值范围是允许的。

output [3:0] a; // 4-bit 位宽的wire. 没有申明数据类型,默认为wire。

wire [0:7] b; // 8-bit 位宽的wire,b[0] 是重要的bit位。

注意:字节顺序是很重要,如[3:0]与[0:3]是不同的。当声明了[3:0]的一个wire类型,指明了高位3是符号位。

4.wire位拼接

{3'b111, 3'b000} => 6'b111000

{1'b1, 1'b0, 3'b101} => 5'b10101

{4'ha, 4'd10} => 8'b10101010 // 十进制和十六进制转二进制再拼接

位拼接的时候必须指明位宽,如{1, 2, 3} 是不合法的,会报错误: unsized constants are not allowed in concatenations。

5.wire位复制

{5{1'b1}} // 5'b11111 (or 5'd31 or 5'h1f)

{2{a,b,c}} // 等同于{a,b,c,a,b,c}

{3'd5, {2{3'd6}}} // 9'b101_110_110. 5-->101,6-->110,101和两个重复的110粘连起来。

复制操作符的一个常见的场景是,将较小的位宽数字扩展为较大的位宽数字,同时保留其带符号的值。这是通过将较小位宽数字的符号位(最重要的位)复制到左边来实现的。例如,符号扩展4’b0101(5)到8位的结果是8’b00000101(5),而符号扩展4’b1101(-3)到8位的结果是8’b11111101(-3)。

问题:构建一个将8位数字扩展到32位的电路。这需要连接符号位的24个副本(即,复制[7]位24次),然后是8位数字本身。注意:在有符号的二进制中最高位1表示负数,0表示正数。

module top_module (

input [7:0] in,

output [31:0] out );

assign out = {{24{in[7]}},in[7:0]};//符号位复制24次,粘贴原来的数据比特

endmodule

二、综合训练

问题描述:给定几个输入向量,将它们连接在一起,然后将它们分割成几个输出向量。有6个5位输入向量:a、b、c、d、e和f,总共有30位输入。对于32位的输出,有四个8位输出向量:w、x、y和z。输出应该是输入向量的连接,后面跟着两个1位,如图6所示。

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );//

assign w = {a,b[4:2]};//5位a加3位高位b,一共8位

assign x = {b[1:0],c,d[4]};//2位b加5位c加1位d,一共8位

assign y = {d[3:0],e[4:1]};//4位d加4位e,一共8位

assign z = {e[0],f,2'b11};//1位e加5位f加2位二进制11,一共8位

endmodule

总结

以上是本期wire的重点、难点,后期将根据考试的真题进行更新。谢谢你的观看!

本文详细介绍了Verilog语言中wire数据类型的作用,包括其在模块间单向连接输入输出的原理,位宽设置,申明方法,位拼接和位复制操作。通过实例和波形图演示,帮助读者掌握wire在FPGA设计中的关键应用。

本文详细介绍了Verilog语言中wire数据类型的作用,包括其在模块间单向连接输入输出的原理,位宽设置,申明方法,位拼接和位复制操作。通过实例和波形图演示,帮助读者掌握wire在FPGA设计中的关键应用。

5083

5083

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?