文章目录

Abstract

固态硬盘(SSD)如今被广泛应用于各种计算机系统,包括数据中心和企业服务器。随着这些系统的输入/输出(I/O)需求不断增加,制造商正在改进SSD架构以满足这些需求。例如,制造商引入了新的高带宽接口,以取代传统的串行高级技术附件(SATA)主机接口协议。这些新接口(例如非易失性内存主机控制器接口规范,NVMe)被设计为能够实现SSD能够提供的高并发I/O带宽。尽管具有复杂功能的现代SSD(例如采用NVMe协议的SSD)已经上市,但现有的SSD模拟工具已经落后,因为它们未能捕捉到这些新特性。我们发现,现有的SSD模拟器存在三个不足之处,导致它们无法准确模拟实际市售SSD的性能。首先,这些模拟器未能模拟新协议(例如NVMe)的关键特性,例如它们使用的多个应用级队列以及消除操作系统对I/O请求处理的干预。其次,这些模拟器通常未能准确捕捉高级SSD维护算法(例如垃圾回收)的影响,因为它们无法正确或快速地模拟稳态条件,这些条件会显著改变这些算法在实际SSD中的行为。第三,这些模拟器未能捕捉I/O请求的完整端到端延迟,这可能会错误地影响使用新兴非易失性存储技术的SSD的报告结果。由于未能准确模拟这三个特性,现有模拟器报告的结果与实际SSD性能有显著偏差。在本文中,我们介绍了一个名为MQSim的新模拟器,它能够准确模拟现代SSD和传统SATA基SSD的性能。MQSim准确模拟了新的高带宽协议实现、SSD的稳态条件以及现代SSD中请求的完整端到端延迟。我们验证了MQSim,发现其报告的性能结果与四个实际最先进的SSD的实际性能仅相差6%-18%。我们表明,通过模拟现代SSD的关键特性,MQSim揭示了现有模拟器未能捕捉到的几个真实且重要的问题,例如性能受流量间干扰的影响。我们已将MQSim作为开源工具发布,希望它能帮助研究人员探索新的不同方向。

1 Introduction

固态硬盘(SSD)如今被广泛应用于计算机系统。由于其高吞吐量、低响应时间和成本的下降,SSD已经在许多数据中心和企业服务器以及消费设备中取代了传统的机械硬盘(HDD)。随着企业级和消费级应用的I/O需求不断增长,SSD架构正在迅速发展以提供更高的性能。例如,一个主要的创新是引入了新的主机接口协议以替代传统的SATA协议。过去,许多SSD使用了为HDD设计的串行高级技术附件(SATA)协议。然而,随着时间的推移,SATA被证明对SSD来说效率低下,因为它无法实现当代SSD能够提供的快速I/O访问和每秒数百万次I/O操作(IOPS)。新的协议,如NVMe,克服了这些障碍,因为它们是专门为SSD的高吞吐量而设计的。NVMe通过使用多队列SSD(MQ-SSD)的概念,实现了I/O请求的高吞吐量和低延迟。虽然SATA仅向操作系统暴露一个请求端口,但MQ-SSD协议为应用程序提供了多个请求队列,直接暴露给SSD设备控制器。这使得(1)应用程序可以绕过操作系统对I/O请求的处理,以及(2)SSD控制器可以根据SSD资源的繁忙程度调度I/O请求。因此,SSD可以做出更高性能的I/O请求调度决策。

随着SSD及其相关协议的发展以跟上系统需求的变化,研究社区需要能够可靠地模拟这些新特性的仿真工具。不幸的是,现有的SSD模拟器未能模拟已经上市的现代SSD的许多关键特性。我们评估了几款实际的现代SSD,发现现有的SSD模拟器未能捕捉到三个对准确模拟现代SSD行为至关重要的特性。首先,这些模拟器未能正确模拟现代SSD协议中使用的多队列方法。相反,它们仅实现了传统HDD协议(如SATA)中使用的单队列方法。因此,现有的模拟器未能捕捉到(1)请求级并行性的高度以及(2)现代SSD中缺乏操作系统干预。其次,许多模拟器未能在合理的模拟时间内充分模拟稳态行为。许多基本的SSD维护算法(如垃圾回收)在SSD是新的(即,尚未向驱动器写入任何数据)时不会执行。因此,制造商设计这些维护算法以在SSD达到稳态工作点时(即,SSD中的所有页面至少被写入一次后)表现最佳。然而,不能捕捉稳态行为(在合理模拟时间内)的模拟器在新的SSD上执行这些维护算法。因此,许多现有的模拟器未能在实际条件下充分捕捉到算法行为,通常报告不切实际的SSD性能结果(正如我们在第3.2节中讨论的)。第三,这些模拟器未能捕捉到执行I/O请求的完整端到端延迟。现有的模拟器仅捕捉在SSD内部操作期间发生的请求延迟部分。然而,许多新兴的高速非易失性存储器大大降低了SSD内部操作的延迟,因此,未被捕捉的部分延迟现在占总请求延迟的很大一部分。例如,在使用3D XPoint存储器的英特尔Optane SSD中,处理请求和在系统I/O总线(例如PCIe)上传输数据的开销比存储器访问延迟要高得多。通过不捕捉完整的端到端延迟,现有的模拟器未能报告使用新兴存储技术的SSD的真实性能。

基于我们对实际现代SSD的评估,我们发现这三个特性对于模拟器捕捉至关重要。由于现有的模拟器未能充分模拟这些特性,它们的结果与实际SSD的性能有显著偏差。我们的目标是开发一个新的SSD模拟器,能够可靠地模拟现代多队列SSD和传统SATA基SSD的特性和性能。为此,我们介绍了MQSim,这是一个新的模拟器,为评估SSD提供了一个准确且灵活的框架。MQSim通过(1)提供传统(例如SATA)和现代(例如NVMe)主机接口的详细模型;(2)准确且快速地模拟SSD的稳态行为;以及(3)测量从应用程序将请求放入队列到请求响应到达主机的请求的完整端到端延迟,解决了我们发现的现有模拟器的三个不足。为了使MQSim能够轻松适应未来的SSD发展,我们采用了模块化设计。我们的模块化方法允许用户轻松修改单个组件(例如I/O调度器、地址映射)的实现,而无需更改模拟器的其他部分。我们为MQSim提供了两种执行模式:(1)独立执行模式,以及(2)与gem5全系统模拟器集成的执行模式。我们使用几款实际的SSD验证了MQSim的性能,发现MQSim报告的响应时间结果与实际SSD的响应时间非常接近,平均(最大)误差仅为11%(18%),用于实际存储工作负载跟踪。通过准确模拟现代SSD的关键特性,MQSim能够揭示现有模拟器无法展示的几个问题,例如多队列SSD中流量间干扰对公平性和系统性能的影响。我们已将MQSim作为开源工具提供给研究社区,希望MQSim能够帮助研究人员探索新的不同方向。我们在这项工作中做出了以下关键贡献:

- 我们使用实际的现成SSD展示了现有的SSD模拟器未能充分捕捉现代SSD的三个重要特性:(1)现代主机接口协议(如NVMe)使用的多队列模型;(2)SSD的稳态行为;以及(3)端到端I/O请求延迟。

- 我们介绍了MQSim,这是一个能够准确模拟基于NVMe的现代SSD和传统基于SATA的SSD的模拟器。据我们所知,MQSim是第一个公开可用的能够准确模拟NVMe协议的SSD模拟器。我们通过与几款实际的多队列SSD进行对比验证了MQSim的结果。

- 我们展示了MQSim如何揭示现有模拟器无法捕捉的现代SSD中的重要问题,例如流量间干扰对公平性和系统性能的影响。

2 Background

在本节中,我们简要介绍多队列固态硬盘(MQ-SSD)设备的背景知识。首先,我们讨论MQ-SSD的内部组织结构(第2.1节)。接下来,我们讨论SSD常用的主机接口协议(第2.2节)。最后,我们讨论SSD闪存转换层(FTL)如何处理请求并执行维护任务(第2.3节)。

2.1 SSD Internals (内部结构)

现代MQ-SSD通常使用NAND闪存芯片构建。NAND闪存支持以闪存页面(通常为4 kB)为粒度的读写操作。在NAND闪存芯片内部,多个页面被组织成一个闪存块,这是擦除操作的粒度。只有擦除(即空闲)的页面才能进行写入操作。为了最小化写入延迟,MQ-SSD执行原地更新(即,当逻辑页面被更新时,其数据被写入到不同的空闲物理页面,并更新逻辑到物理的映射)。这避免了在写入操作期间擦除旧物理页面的需要。相反,旧页面被标记为无效,垃圾回收程序在后台回收无效的物理页面。图1展示了MQ-SSD的内部组织结构。MQ-SSD中的组件被分为两组:(1)后端,包括存储设备;(2)前端,包括控制和管理单元。存储设备(例如NAND闪存、相变存储器、STT-MRAM、3D XPoint等)在后端以高度层次化的方式组织,以最大化I/O并发性。后端包含多个独立的总线通道,将存储设备连接到前端。每个通道连接到一个或多个存储芯片。对于基于NAND闪存的SSD,每个NAND闪存芯片通常被划分为多个芯片,每个芯片可以独立执行存储命令。芯片内的所有芯片共享一个通用通信接口。每个芯片由一个或多个平面组成,平面是闪存单元的数组。每个平面包含多个块。如果每个平面都在相同地址偏移处对同一命令执行操作,则单个芯片内的多个平面可以并行执行存储操作。在MQ-SSD中,前端包括三个主要组件:(1)主机接口逻辑(HIL),实现与主机通信的协议(第2.2节);(2)闪存转换层(FTL),管理闪存资源并处理I/O请求(第2.3节);(3)闪存芯片控制器(FCCs),向后端的存储芯片发送命令并传输数据。前端包含板载DRAM,供这三个组件使用,用于缓存应用程序数据和存储闪存管理的数据结构。

2.2 Host–Interface Logic(主机接口逻辑)

主机接口逻辑(HIL)在利用NAND闪存内存的内部并行性以向主机提供更高I/O性能方面发挥着关键作用。SATA协议通常用于传统SSD,因为它在企业和客户端系统中得到了广泛支持。SATA采用原生命令队列(NCQ),允许SSD并发执行I/O请求。NCQ允许SSD根据后端资源的空闲情况调度多个I/O请求。非易失性内存主机控制器接口规范(NVMe)协议旨在缓解SATA的瓶颈,并通过PCIe总线实现可扩展的高带宽和低延迟通信。当应用程序在NVMe中发出I/O请求时,它绕过了操作系统中的I/O堆栈和块层队列,而是直接将请求插入到应用程序专用的提交队列(图1中的SQ)中。然后,SSD从SQ中选择一个请求,执行该请求,并将请求的完成信息(例如,确认、读取数据)插入到相应应用程序的完成队列(CQ)中。NVMe已经在现代SSD产品中被广泛采用。

2.3 Flash Translation Layer(闪存转换层)

FTL在SSD内的微处理器上执行,执行I/O请求和闪存管理程序。在使用NVMe的SSD中,处理I/O请求需要FTL中的四个步骤。首先,当HIL从SQ中选择一个请求时,它将请求插入到设备级队列中。其次,HIL将请求分解为多个闪存事务,每个事务的粒度为单个页面。接下来,FTL检查请求是否为写入操作。如果是,并且MQ-SSD支持写入缓存,则写入缓存管理单元将每个事务的数据存储在DRAM内的写入缓存空间中,并要求HIL准备响应。否则,FTL将事务的逻辑页面地址(LPA)翻译为物理页面地址(PPA),并将事务排队到相应的芯片级队列中。读取(RDQ)和写入(WRQ)事务有单独的队列。事务调度单元(TSU)解决芯片级队列中待处理事务的资源争用,并将可以执行的事务发送到其对应的FCC。最后,当请求的所有事务完成时,FTL要求HIL准备响应,然后将响应发送到主机。FTL中的地址翻译模块在实现原地更新中起着关键作用。当事务写入LPA时,页面分配方案将LPA分配给空闲的PPA。LPA到PPA的映射记录在映射表中,该表存储在非易失性存储器中,并缓存在DRAM中(以减少映射查找的延迟)。当事务从LPA读取时,该模块搜索LPA的映射并检索PPA。FTL还负责内存磨损管理(即磨损均衡)和垃圾回收(GC)。当空闲页面数量低于阈值时,触发GC。GC程序通过回收无效页面来回收空间,方法是选择一个包含大量无效页面的候选块,将该块中的任何有效页面移动到空闲块中,然后擦除候选块。在GC期间生成的任何读取和写入事务都被插入到专用的读取(GC-RDQ)和写入(GC-WRQ)队列中。这允许事务调度单元在空闲时段调度与GC相关的请求。

3 Simulation Challenges for Modern MQ-SSDs

在本节中,我们将现有的先进SSD模拟器的能力与现代SSD设备的常见特性进行比较。如图1所示,我们确定了现代SSD的三个显著特性,这些特性尚未得到当前模拟工具的支持:多队列支持、快速建模稳态行为以及正确建模端到端请求延迟。虽然这些特性在某些传统SSD中也存在,但它们在评估现代和新兴的MQ-SSD时更为关键,因为现有模拟器对这些特性的缺失会导致模拟结果与实际测量性能之间存在较大偏差。

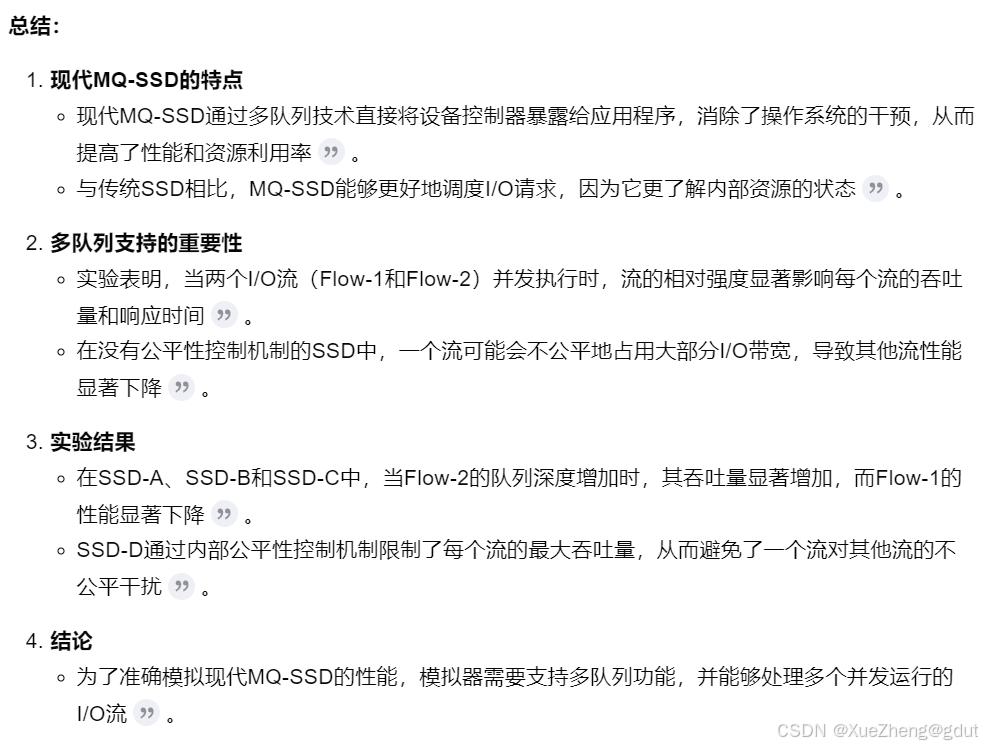

3.1 Multi-Queue Support

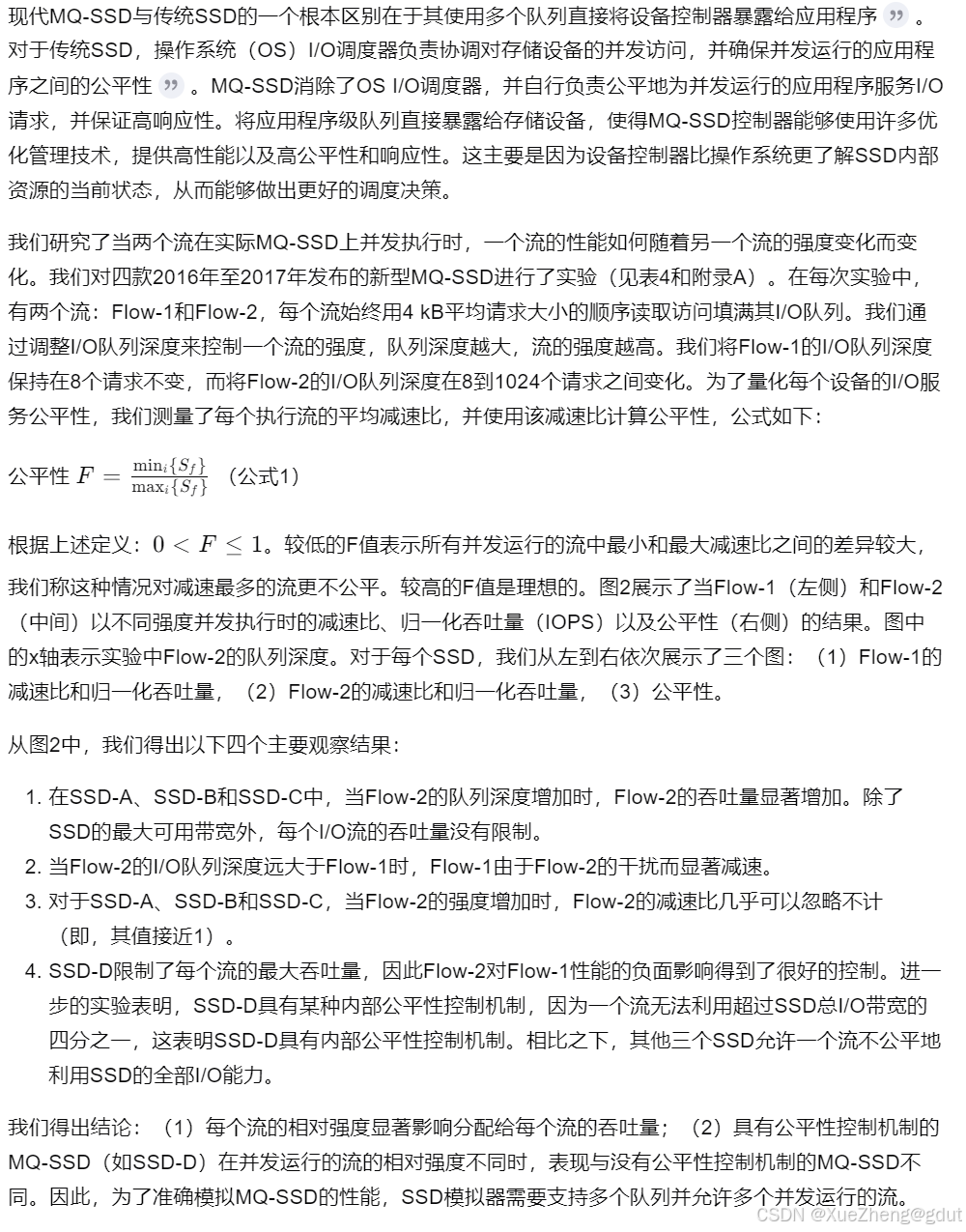

现代MQ-SSD与传统SSD的一个根本区别在于其使用多个队列直接将设备控制器暴露给应用程序。对于传统SSD,操作系统(OS)I/O调度器负责协调对存储设备的并发访问,并确保并发运行的应用程序之间的公平性。MQ-SSD消除了OS I/O调度器,并自行负责公平地为并发运行的应用程序服务I/O请求,并保证高响应性。将应用程序级队列直接暴露给存储设备,使得MQ-SSD控制器能够使用许多优化管理技术,提供高性能以及高公平性和响应性。这主要是因为设备控制器比操作系统更了解SSD内部资源的当前状态,从而能够做出更好的调度决策。

3.2 Steady-State Behavior (稳态行为)

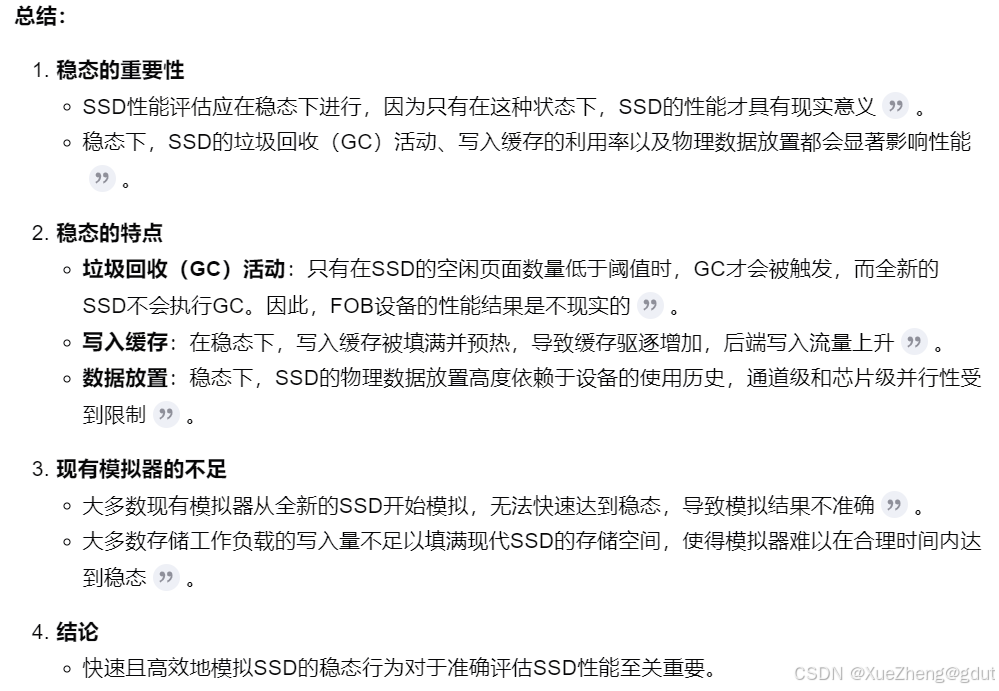

SSD性能评估标准明确指出,SSD性能应在稳态下报告。因此,快速达到稳态(即预处理)是SSD设备性能评估的一个基本要求,以确保结果是在稳态下收集的。这一政策的重要性基于以下三个原因。

首先,只有当设备执行了一定数量的写入操作,导致SSD中空闲页面数量低于垃圾回收(GC)阈值时,才会触发GC活动。GC活动会干扰用户I/O活动,并显著影响设备的持续性能。然而,一个全新的未使用(FOB,Fresh Out-of-Box)设备不太可能执行GC。因此,FOB设备上的性能结果是不现实的,因为它们没有考虑到GC。

其次,稳态下写入缓存的益处可能低于短期益处,尤其是对于写入密集型工作负载。更具体地说,在稳态下,写入缓存被应用程序数据填满并预热,很可能会没有空闲槽位分配给新的写入请求。这会导致缓存驱逐和后端闪存写入流量增加。

第三,当前运行应用程序的物理数据放置高度依赖于设备使用历史和之前进程的数据放置情况。例如,哪些物理页面当前是空闲的,取决于之前I/O请求是如何写入和验证物理页面的。因此,在稳态下,SSD的通道级和芯片级并行性受到限制。

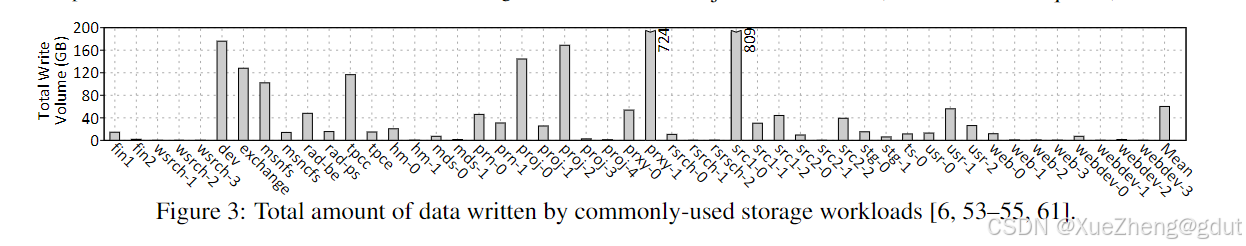

尽管一些研究成功地对稳态进行了预处理和模拟,但许多先前的研究并未探索稳态行为对其提案的影响。相反,它们的模拟从全新的SSD开始,从未达到稳态(例如,当SSD中的每个物理页面至少被写入一次时)。大多数知名存储跟踪记录都不足以填满现代SSD的整个存储空间。图3展示了常用存储工作负载的总写入量。我们观察到,大多数工作负载的总写入量远小于大多数SSD的存储容量,平均写入量为60 GB。即使对于少数足够大以填满SSD的工作负载,对于许多现有模拟器来说,模拟每个I/O请求并达到稳态也是耗时的(见第5节)。因此,拥有一个能够高效且高性能地模拟SSD稳态的模拟器至关重要。

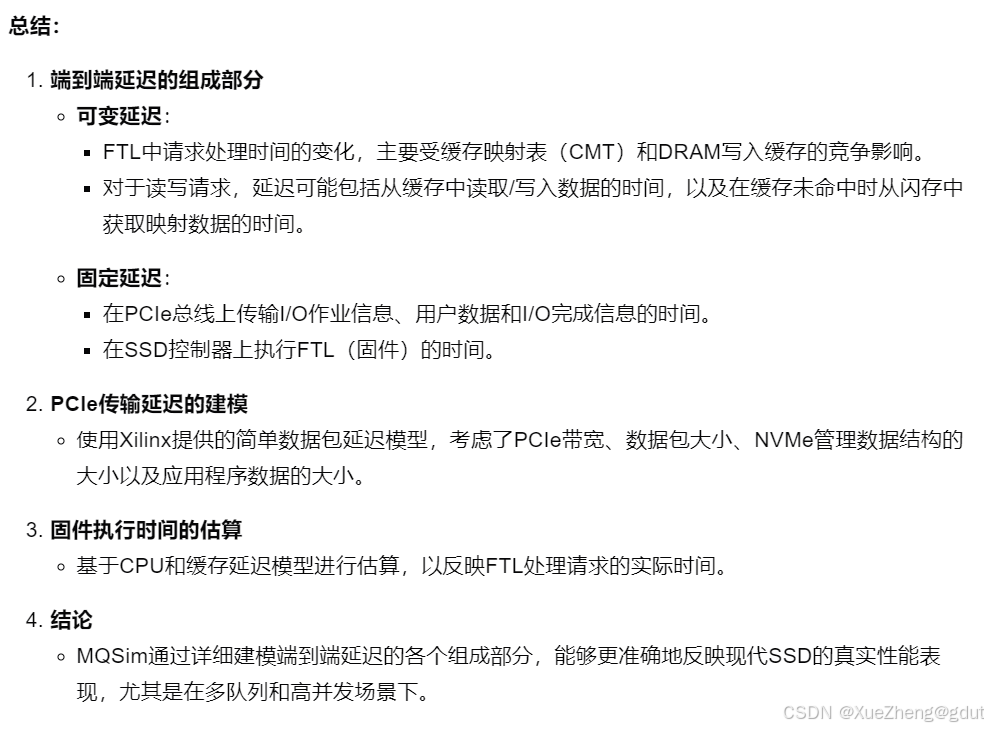

3.3 Real End-to-End Latency

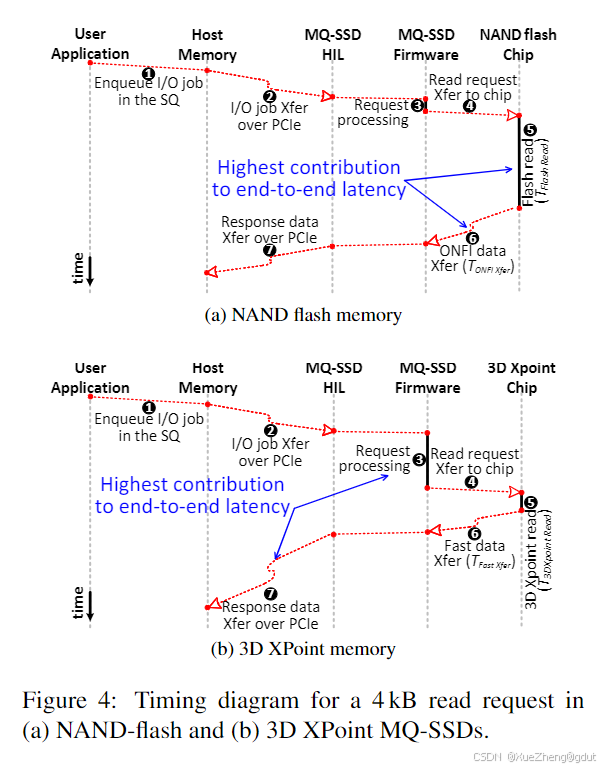

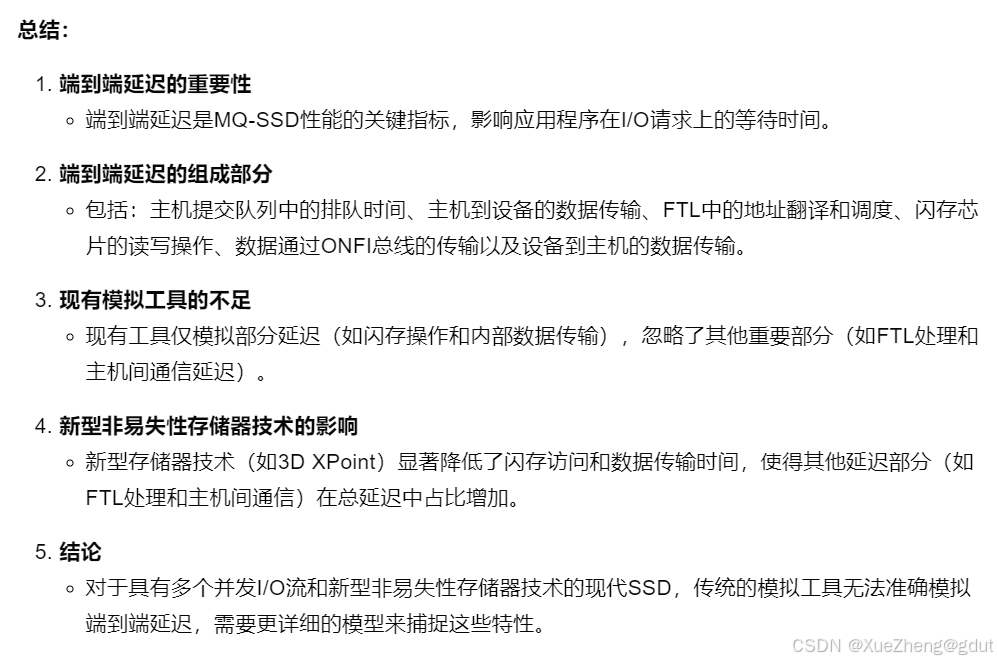

请求延迟是MQ-SSD性能的关键因素,因为它影响应用程序在I/O请求上的等待时间。I/O请求的端到端延迟,从请求被插入主机提交队列到响应从MQ-SSD设备发送回完成队列,包括七个不同的部分,如我们在图4中所示。现有的模拟工具仅模拟端到端延迟的某些部分,这些部分通常被认为是端到端延迟的主要组成部分。

图4a展示了典型NAND闪存基MQ-SSD中4 kB读取请求的端到端延迟图。它包括:在提交队列(SQ)中排队I/O作业(步骤1)、通过PCIe总线传输主机到设备的I/O作业(步骤2)、在FTL中进行地址翻译和事务调度(步骤3)、将读取命令和地址传输到闪存芯片(步骤4)、闪存芯片读取(步骤5)、通过Open NAND Flash Interface(ONFI)总线传输读取数据(步骤6)以及通过PCIe总线将设备到主机的读取数据传输(步骤7)。步骤5和6被认为是端到端请求处理延迟中最耗时的部分。考虑到典型的8 kB页面读取操作,I/O作业插入(小于1微秒,如我们在实际SSD上测量的)、FTL请求处理(1微秒)[47](假设映射表缓存命中)以及I/O作业和数据通过PCIe总线的传输(4微秒)[41, 46]与闪存读取(50-110微秒)[49, 51, 52, 69]和ONFI NV-DDR2 [65]闪存传输(20微秒)相比,贡献可以忽略不计。

然而,上述假设是不现实的,主要有两个原因。首先,对于某些I/O请求,FTL请求处理可能并不总是可以忽略不计,甚至可能与闪存读取访问时间相当。例如,先前的工作[26]表明,如果FTL使用页面级地址映射,则没有局部性的 workload 会导致缓存映射表(CMT)中出现大量未命中。在这种情况下,用户读取操作会一直停滞,直到从SSD后端读取映射数据并传输到前端[24]。这可能导致步骤3的延迟显著增加,甚至比步骤5和6的总延迟还要长。

其次,如图4b所示,新兴的高速非易失性存储器技术(如3D XPoint)[7, 9, 16, 48]显著降低了SSD后端的访问和数据传输时间,与NAND闪存相比,降低了多达三个数量级[25, 40, 42, 43]。3D XPoint读取和传输的总延迟(小于1微秒)占端到端I/O请求处理延迟(小于10微秒)的比例不到10%[7, 16]。在这种情况下,传统的模拟工具将不准确,因为它没有模拟端到端延迟的主要部分。

总之,对于具有(1)多个并发I/O流(这可能导致CMT未命中显著增加)以及(2)非常快的新型非易失性存储器技术(如3D XPoint)的现代SSD设备,详细的、现实的端到端延迟模型是准确模拟的关键。现有的模拟工具对于这些设备来说是不准确的。

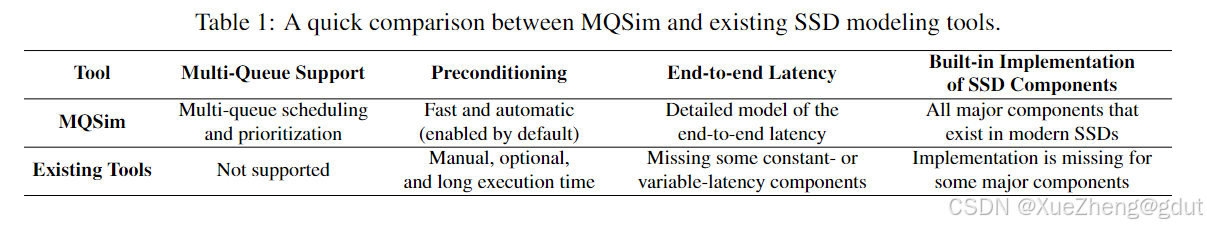

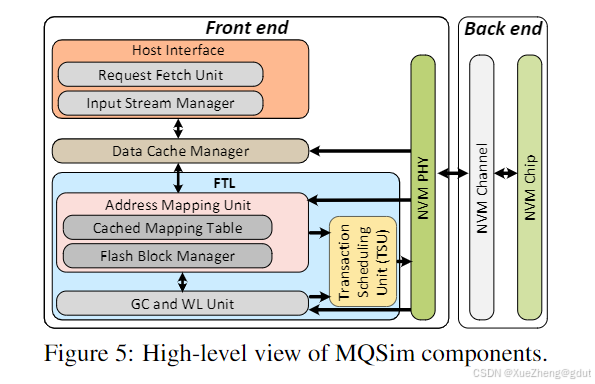

4 Modeling a Modern MQ-SSD with MQSim

据我们所知,目前没有任何SSD建模工具支持多队列I/O执行、快速高效地建模SSD的稳态行为以及完整的端到端请求延迟估计。在本工作中,我们提出了MQSim,这是一个全新的模拟框架,能够支持这些对于准确建模现代MQ-SSD的性能和设计空间探索至关重要的特性。尽管MQSim主要为MQ-SSD模拟而设计,但它也支持传统基于SATA的SSD模拟,这些SSD实现了原生命令队列(NCQ)。我们的新模拟器模拟了图1中现代SSD中存在的所有组件。表1提供了MQSim与先前SSD模拟器的快速比较。MQSim是一个离散事件模拟器,使用C++编写,并在宽松的MIT许可下发布。图5展示了MQSim主要组件的高级视图及其相互作用。在本节中,我们将简要描述这些组件,并解释它们相对于先前模拟器的新特性。

4.1 SSD Back End Model

MQSim为闪存芯片提供了一个简单但详细的模型。它考虑了SSD后端的三个主要延迟组成部分:(1)地址和命令传输到存储芯片;(2)不同技术存储的闪存读写执行,这些技术可以存储1、2或3比特/单元;以及(3)数据在存储芯片之间的传输。MQSim的闪存模型考虑了芯片级和晶片级并行性的约束,以及先进的命令执行。MQSim的一个重要新特性是,它可以配置或轻松修改以模拟新型NVM芯片(例如,那些不需要先擦除再写入的芯片)。由于NVM芯片通信接口与芯片内部存储操作的实现是解耦的,因此可以在不改变MQSim其他组件实现的情况下修改NVM芯片。另一个新特性是,MQSim解耦了读写操作的大小。这一特性有助于利用现代闪存芯片的大页面尺寸,从而在不降低读取性能的情况下提高写入性能。对于闪存芯片写入,操作始终是页面大小。MQSim的数据缓存控制器可以延迟写入,以避免对部分更新的逻辑页面进行回写(更新大小小于物理页面大小)。当需要将部分更新的逻辑页面写回到闪存存储时,首先从存储该页面数据的物理页面中读取未更改的子页面(扇区)。然后,将未更改和已更新的页面部分合并。最后,将整个页面数据写入一个新的空闲物理页面。对于闪存芯片读取,操作可以小于物理页面大小。当读取操作完成时,仅将I/O请求中请求的数据部分从闪存芯片传输到SSD控制器,避免了大物理页面的数据传输开销。

4.2 SSD Front End Model

MQSim的前端模型包括现代SSD控制器的所有基本组件,并提供了许多新特性,这些特性在之前的SSD建模工具中并不存在。

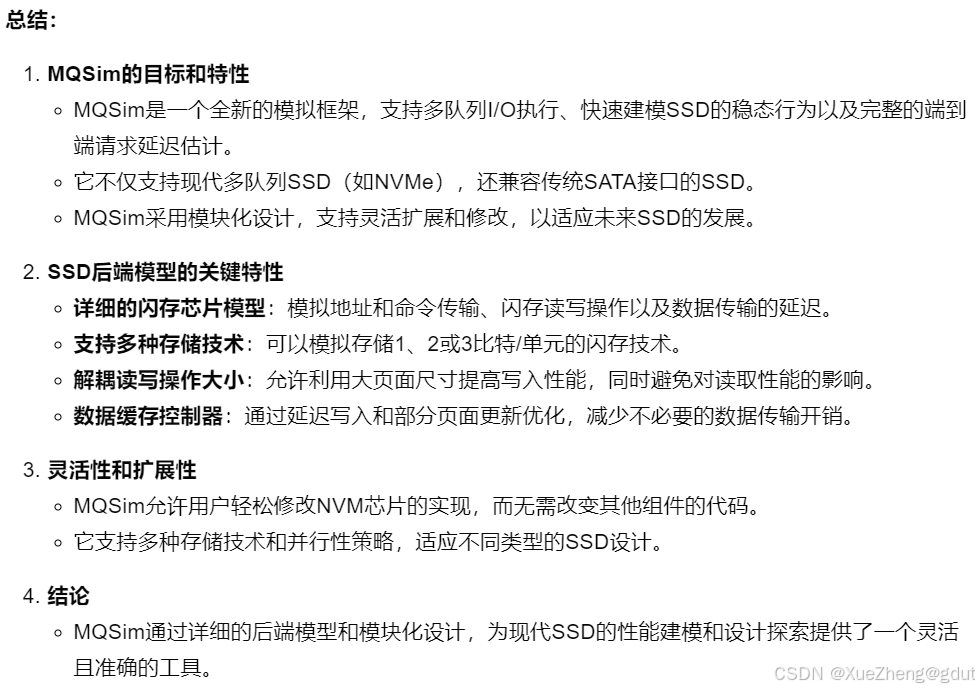

4.2.1 Host–Interface Model

MQSim的主机接口组件提供了对现代SSD的NVMe多队列(MQ)和SATA原生命令队列(NCQ)模型的支持。据我们所知,MQSim是第一个支持MQ I/O请求处理的建模工具。在MQSim的主机接口中,有一个请求获取单元,它从不同的输入队列中获取并调度应用程序的I/O请求。NVMe主机接口为用户提供了“QueueFetchSize”参数,该参数可用于调整请求获取单元的行为,以准确模拟真实MQ-SSD的行为。具体来说,该参数定义了可以从每个提交队列(SQ)中并发服务的I/O请求数量的最大值。更准确地说,任何给定时间,从主机SQ获取到设备级队列中的I/O请求数量总是小于或等于QueueFetchSize。此参数对MQ-SSD的多流请求处理特性有重大影响(见第3.1节,即每个I/O流的最大可实现吞吐量和流间干扰的概率)。附录A.3分析了此参数对性能的影响。MQSim还模拟了主机端请求队列的不同优先级类别,这些是NVMe标准规范的一部分。

4.2.2 Data Cache Manager

MQSim的数据缓存管理器组件实现了一个基于DRAM的缓存,采用最近最少使用(LRU)替换策略。与之前的SSD建模工具相比,MQSim的DRAM缓存可以配置为缓存(1)最近写入的数据(默认模式)、(2)最近读取的数据,或(3)最近写入和读取的数据。MQSim的缓存管理器的新特性是,它实现了一个DRAM访问模型,其中考虑了对DRAM芯片的并发访问竞争以及DRAM命令的延迟。MQSim中的DRAM缓存模型可以扩展为使用详细的快速DRAM模拟器(如Ramulator),以进行关于DRAM缓存性能对整体MQ-SSD性能影响的详细研究。我们将此留作未来工作。

4.2.3 FTL Components

MQSim实现了所有主要的FTL组件,包括(1)地址翻译单元、(2)垃圾回收(GC)和磨损均衡(WL)单元,以及(3)事务调度单元。MQSim为这些组件的每一种都提供了不同的选项,包括最先进的地址翻译策略[24, 78]、GC候选块选择算法[10, 18, 23, 45, 81, 91]和事务调度方案[34, 87]。MQSim还实现了几种最先进的GC和闪存管理机制,包括可抢占的GC I/O调度[44]、使用复制读写命令对在同一平面内从一个物理页到另一个物理页的数据移动[27],以及程序/擦除暂停[87],以减少GC操作对应用I/O请求的干扰。MQSim的一个新特性是,其所有FTL组件都支持多流(即多输入队列)请求处理。例如,地址映射单元可以将缓存映射表空间分配给并发运行的流。这种对多队列感知请求处理的内在支持有助于设计空间探索,以实现MQ-SSD的性能隔离和QoS方案。

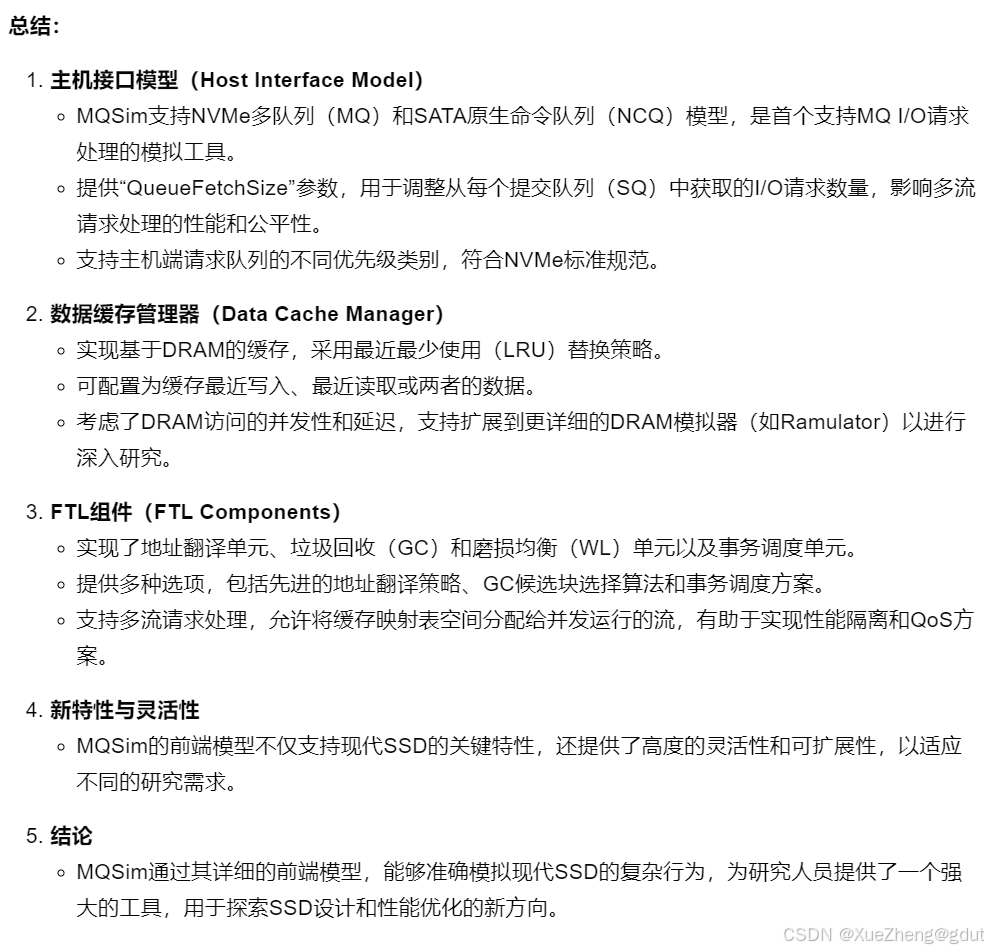

4.3 Modeling End-to-End Latency

除了闪存操作和SSD内部数据传输延迟(图4中的步骤3、4、5和6)之外,MQSim还对端到端请求延迟建模,包括可变延迟和固定延迟。

可变延迟包括:

FTL中由于缓存映射表(CMT)和DRAM写入缓存的竞争而导致的可变请求处理时间。

根据请求类型(读或写)和请求的逻辑地址,FTL中的请求处理时间可能包括以下内容:

- 从/向数据缓存读取/写入所需的时间,以及在缓存地址映射表未命中时,从闪存存储中获取映射数据所需的时间。

固定延迟包括: - 在PCIe总线上传输I/O作业信息、完整用户数据以及I/O完成信息所需的时间,以及在控制器微处理器上执行FTL(固件)的时间。

PCIe传输延迟是基于Xilinx提供的简单数据包延迟模型计算的,该模型考虑了以下因素: - PCIe通信带宽,

- PCIe事务层数据包(TLP)的有效载荷和头部大小,

- NVMe管理数据结构的大小,以及应用程序数据的大小。

- 固件执行时间是使用包含CPU和缓存延迟的模型估算的。

4.4 Modeling Steady-State Behavior

MQSim的基本假设是所有模拟都应在设备处于稳态时执行。为了建模稳态行为,MQSim默认在实际模拟过程开始之前自动执行一个预处理函数。该函数在短时间内(例如,在800 GB的MQ-SSD上运行tpcc [53]时少于8分钟)将所有可用的物理页面转换为有效或无效状态,基于提供的稳态有效/无效页面分布模型[82](只有少数闪存块保持为空闲并添加到空闲块池中)。MQSim预处理输入跟踪以提取应用I/O请求的逻辑页面地址(LPA)访问特征,并将提取的信息作为输入提供给有效/无效页面分布模型。此外,输入跟踪特征(如平均写入到达率和写入地址分布)用于预热写入缓存。

4.5 Execution Modes

MQSim提供了两种运行模式:(1)独立运行模式,其中它接受真实的磁盘跟踪记录或合成工作负载;(2)集成运行模式,其中它从执行驱动的引擎(例如gem5)接收磁盘请求。

5 Comparison with Previous Simulators

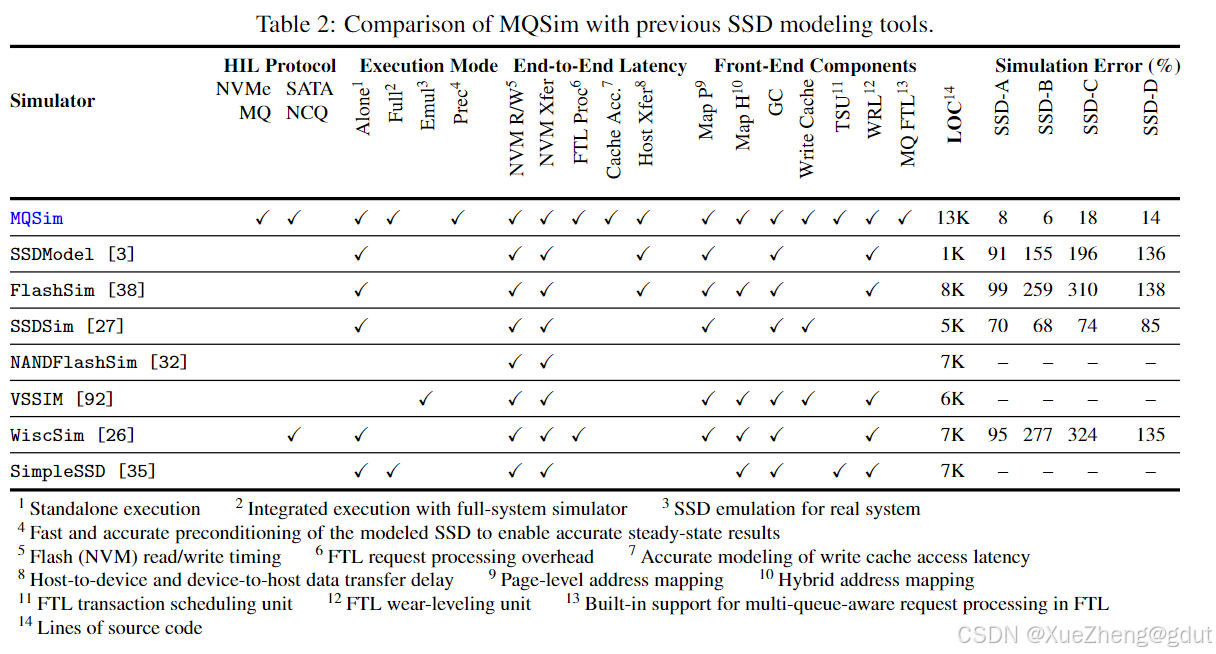

随着SSD在现代计算系统中的使用不断增加,人们对SSD设计空间探索的兴趣也日益增加。近年来,已经开发了多种SSD模拟器。表2总结了MQSim和流行的现有SSD建模工具的特性。该表还显示了每个模拟器在模拟四款实际MQ-SSD(见附录A.1中的方法论)的性能时与实际测量结果的平均误差率。现有的工具要么没有模拟现代SSD的一些主要组件,要么提供了过于简化的组件模型,导致不切实际的I/O请求延迟估计。相比之下,MQSim为现代SSD的所有主要组件提供了详细的实现。MQSim使用C++编写,拥有1.3万行代码(LOC)。接下来,我们将讨论MQSim相对于先前工具的主要优势。

主机接口逻辑(Host-Interface Logic)

如表2所示,大多数现有模拟器假设了一个非常简化的主机接口逻辑模型,没有明确的I/O请求队列管理机制。这导致了对NVMe和SATA协议要求的不切实际的SSD模型。如我们在第3节中提到的,并发执行I/O流给MQ-SSD的性能可预测性和公平性带来了许多挑战。没有现有的模拟器实现了NVMe和多队列I/O请求管理,因此无法准确模拟MQ-SSD的行为。此外,除了WiscSim之外,我们发现没有现有的模拟器实现了对SATA协议和NCQ请求处理的准确建模。这导致了对基于NCQ的I/O调度在实际SSD设备性能中起关键作用的不切实际的SATA设备模拟[15, 26]。

稳态模拟(Steady-State Simulation)

据我们所知,许多现有的SSD建模工具并不提供快速且准确的稳态行为建模。在表2中列出的工具中,只有SSDSim提供了一个名为“make aged”的功能,用于在实际执行输入跟踪之前将一组物理页面的状态更改为有效。然而,这种方法无法准确复制SSD的稳态行为,原因有两个。首先,在执行“make aged”后,物理块将只包含有效页面或空闲页面。这与实际设备中稳态下块的状态相去甚远,因为实际中每个非空闲块都包含有效和无效页面的混合[28, 81, 82]。其次,稳态下数据缓存的状态没有被建模,即模拟从一个完全空的写入缓存开始。一般来说,虽然有可能将这些模拟器带入稳态,但没有快速预处理支持,预处理必须通过执行跟踪来完成。对800 GB SSD进行预处理可能会使模拟时间增加多达80倍[3]。

详细的端到端延迟模型(Detailed End-to-End Latency Model)

如第3.3节所述,应用I/O请求的端到端延迟包括不同的组成部分。表2显示,现有模拟器的延迟建模主要集中在闪存芯片操作的延迟和SSD内部数据传输上。如我们在第3.3节中解释的,这是对应用I/O请求处理延迟的不切实际的模型,即使是对于传统SSD也是如此。为了研究现有工具在建模实际设备方面的准确性,我们在每个模拟器中创建了表4中所示的四款实际SSD的模型,并执行了三个真实跟踪,即tpcc、tpce和exchange。我们排除了不支持基于跟踪的执行的模拟器。表2中最后四列显示了每个模拟器在模拟这四款实际设备的性能(即读写延迟)时的平均误差率。这些模拟器的误差率几乎比MQSim高出一个数量级。我们相信这些高误差率是由于以下四个主要原因:(1)缺乏写入缓存或对写入缓存访问延迟的不准确建模,(2)缺乏对稳态建模的内置支持,(3)对FTL中请求处理延迟的不完整建模,以及(4)缺乏对主机到设备通信延迟的建模。

6 Research Directions Enabled by MQSim

MQSim是一个灵活的模拟工具,能够对现代和传统的SSD设备进行不同的研究。在本节中,我们讨论了两个新的研究方向,这些方向使用MQSim可以轻松探索,而使用现有的模拟工具则难以实现。首先,我们使用MQSim对现代MQ-SSD中的流量间干扰进行了详细分析(第6.1节)。我们解释了在MQ-SSD中共享不同内部资源(如写入缓存、缓存映射表和后端资源)如何引入公平性问题。其次,我们解释了MQSim的全系统模拟模式如何能够实现详细的应用程序级研究(第6.2节)。

6.1 Design Space Exploration of Fairness and QoS Techniques for MQ-SSDs

如我们在第1节中所述,公平性和QoS应被视为现代数据中心SSD的首要设计标准。MQSim提供了一个准确的框架,用于研究流量间干扰,从而能够设计出能够感知干扰的MQ-SSD管理算法,以共享MQ-SSD的内部资源。正如我们在第3.1节中所展示的,两个并发运行的I/O流可能会导致每个流的减速比差异显著,极大地降低公平性和比例进步。这在高端SSD设备中尤其重要,这些设备为每个I/O流提供了更高的吞吐量,正如我们在附录A.3中所展示的。我们发现,这种流量间干扰主要是由于在MQ-SSD中的三个位置发生竞争:1)前端的写入缓存,2)前端的缓存映射表(CMT),以及3)后端的存储资源。在本节中,我们使用MQSim探讨了这些三个竞争点对性能和公平性的影响,而这些影响无法使用现有的模拟器准确探索。

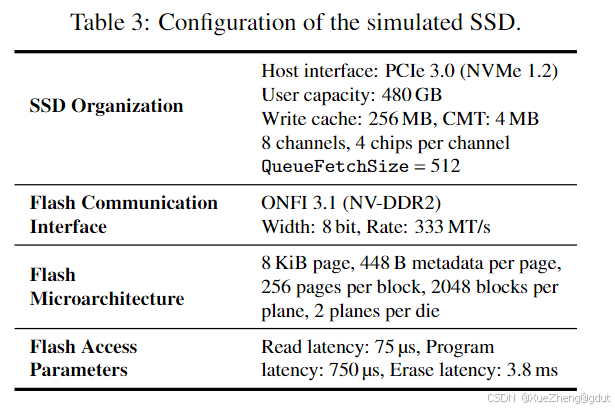

6.1.1 Methodology

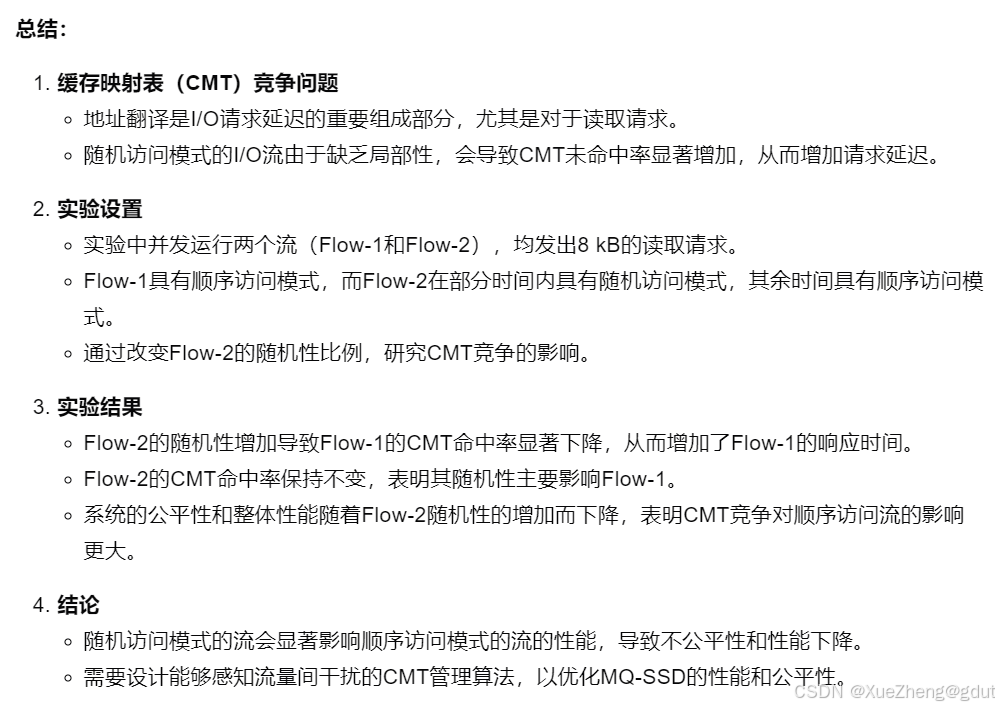

6.1.2 Contention at the Write Cache

在并发运行的多个I/O流中,MQ-SSD的一个竞争点是写入缓存。对于低到中等写入强度的流(平均I/O队列深度小于16),或者具有高空间局部性的流,写入缓存通过避免请求等待底层存储完成写入操作,从而减少了写入请求的响应时间。对于高写入强度或具有高度随机访问模式的流,写入请求会迅速填满写入缓存的有限容量,导致显著的缓存抖动,从而限制了写入请求响应时间的降低。这样的流不仅自身无法从写入缓存中受益,还会阻止其他低写入强度的流从写入缓存中受益,尽管这些低强度流本可以从中获益,从而导致低强度流的性能大幅下降。

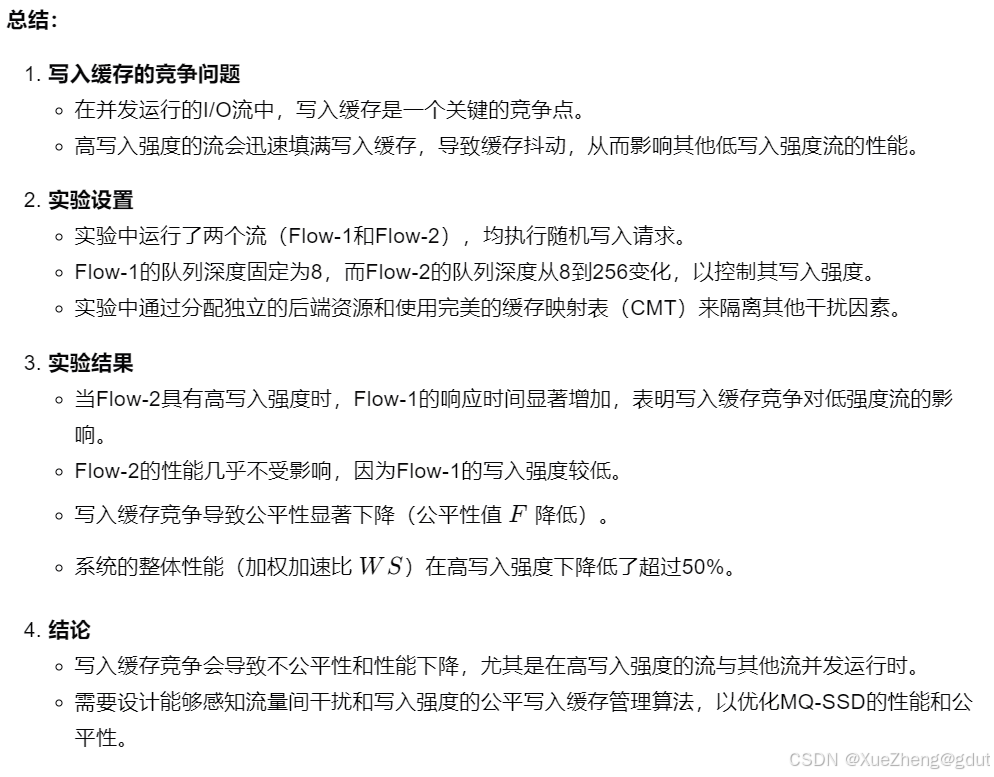

为了理解写入缓存竞争对系统性能和公平性的影响,我们进行了一系列实验,其中运行了两个流,Flow-1和Flow-2,它们都仅执行随机访问写入请求。在这两个流中,平均请求大小都设置为8 kB。我们将Flow-1的队列深度限制为8个请求,以保持其低写入强度。我们通过改变Flow-2的队列深度,从8个请求到256个请求,来控制Flow-2的写入强度。为了隔离写入缓存干扰的影响,我们在实验中(1)为每个流分配了后端资源的专用子集(即Flow-1使用通道1-4,Flow-2使用通道5-8),以避免在后端引入任何干扰;(2)使用了一个完美的缓存映射表(CMT),其中所有地址翻译请求都是命中,以避免由于有限的CMT容量而产生的干扰。图6a显示了当两个流并发运行时,与每个流单独运行时相比,每个流的减速比。图6b显示了当两个流并发运行时系统的公平性和整体性能。从图中我们得出了四个关键观察结果。首先,当Flow-2具有高写入强度(即其队列深度大于16)时,Flow-1显著减速,这表明Flow-2在高写入强度下引起了写入缓存抖动。其次,Flow-2的减速比可以忽略不计,因为Flow-1的写入强度较低。第三,由于写入缓存竞争,当Flow-2具有高写入强度时,公平性显著下降。第四,写入缓存竞争导致MQ-SSD在并发运行多个I/O流时效率低下,因为当Flow-2具有高写入强度时,与Flow-2具有低写入强度时相比,加权加速比降低了超过50%。

我们得出结论,当一个流具有高写入强度时,写入缓存竞争会导致不公平性以及并发运行的流的整体性能下降。在这种情况下,高写入强度的流(1)本身无法从写入缓存中受益;(2)阻止其他低写入强度的流利用写入缓存,尽管这些流本可以从缓存中受益。这激发了为MQ-SSD设计公平的写入缓存管理算法的需求,这些算法需要考虑流量间干扰和流的写入强度。

6.1.3 Contention at the Cached Mapping Table

正如我们在第3.3节中讨论的,地址翻译可能会显著增加I/O请求的端到端延迟,尤其是对于读取请求。我们发现,对于具有随机访问模式的I/O流,由于地址翻译映射的重用性差,缓存映射表(CMT)的未命中率很高,这导致I/O请求生成的流在地址翻译时长时间停滞。而对于具有顺序访问模式的I/O流,由于空间局部性,CMT未命中率保持较低。然而,当两个I/O流并发运行时,其中一个流具有随机访问模式,而另一个流具有顺序访问模式,随机访问模式的流的不良局部性可能会导致两个流的CMT未命中率都很高。

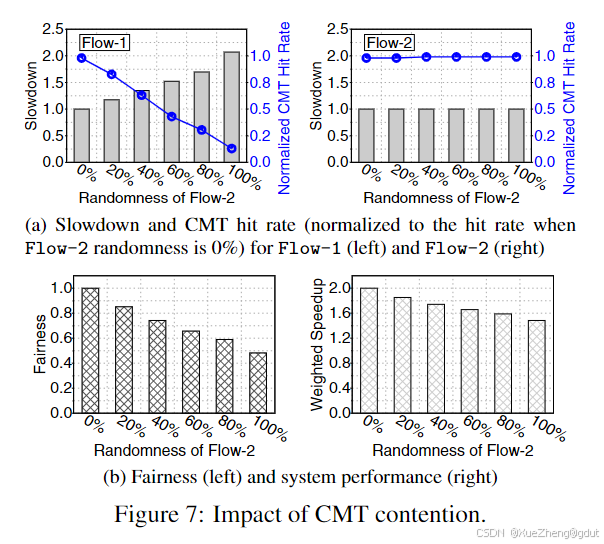

为了理解CMT竞争对系统性能和公平性的影响,我们进行了一系列实验,其中并发运行两个流,它们发出平均请求大小为8 kB的读取请求。在这些实验中,Flow-1具有完全顺序的访问模式,而Flow-2在总执行时间的一部分内具有随机访问模式,其余时间具有顺序访问模式。我们改变了Flow-2的随机性(即执行时间内随机访问模式的比例)。为了隔离CMT竞争的影响,我们将Flow-1分配到后端的通道1-4,Flow-2分配到通道5-8。

图7a显示了当Flow-1和Flow-2并发运行时,与每个流单独运行时相比,每个流的减速比以及CMT命中率的变化。图7b显示了当两个流并发运行时系统的公平性和整体性能。我们从图中得出了两个观察结果。首先,随着Flow-2的随机性增加,Flow-1的CMT命中率降低,而Flow-2的CMT命中率保持不变。这表明Flow-2的随机性引入了CMT竞争,损害了Flow-1的CMT命中率。其次,随着Flow-1的CMT命中率降低,该流的减速比增加,在Flow-2的访问模式完全随机时,Flow-1的减速比达到2.1倍。第三,随着Flow-2的随机性增加,系统的公平性和整体性能都下降,因为Flow-2引入的干扰损害了Flow-1的性能,而对Flow-2自身没有任何显著的好处。

我们得出结论,具有随机访问模式的I/O流引入的CMT竞争不成比例地减慢了具有顺序访问模式的并发运行流,这些流本可以从CMT中受益,从而导致高不公平性和系统性能下降。为了避免这种不公平性和性能损失,MQ-SSD应该使用能够感知流量间干扰的CMT管理算法。

6.1.4 Contention at the Back End Resources

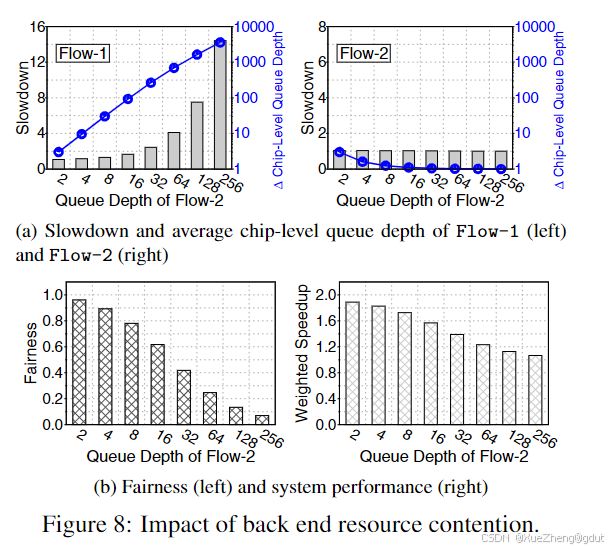

第三个竞争点是MQ-SSD内的后端资源(见第2.1节)。如果一个高带宽流在短时间内发出大量请求,它可以占用大部分后端资源,从而导致低带宽流的请求被延迟,直到后端资源完成对高带宽流的请求处理。

为了理解后端资源竞争对系统性能和公平性的影响,我们进行了一系列实验,其中并发运行两个I/O流,它们发出8 kB的随机读取请求。Flow-1是一个低带宽I/O流,我们将它的提交队列大小限制为2个请求。我们通过改变Flow-2的提交队列大小,从2个请求到256个请求,来控制Flow-2的带宽。为了隔离后端资源竞争的影响,我们禁用了写入缓存,并模拟了一个地址翻译请求总是命中的缓存映射表(CMT)。

图8a显示了当Flow-1和Flow-2并发运行时,与每个流单独运行时相比,每个流的减速比以及后端芯片级队列深度的平均变化。图8b显示了当两个流并发运行时系统的公平性和整体性能。我们从图中得出了四个观察结果。首先,当Flow-2的带宽增加时,Flow-1的后端芯片级队列深度显著增加。其次,当Flow-2的主机端队列深度超过16时,Flow-1显著减速。例如,当Flow-2的队列深度为256个请求时,Flow-1的减速比达到了14.4倍。第三,Flow-2的减速比几乎为1,表明其带宽增加对自身几乎没有影响。第四,由于Flow-1和Flow-2的不对称减速比(即Flow-1显著减速,而Flow-2几乎没有减速),系统的公平性和整体性能都下降了。

我们得出结论,高带宽流可以显著增加后端芯片级队列的深度,从而导致并发运行的低带宽流大幅减速。FTL事务调度单元必须能够感知MQ-SSD后端的流量间干扰,以使每个流的性能更加公平,从而保持整体性能的高效性。

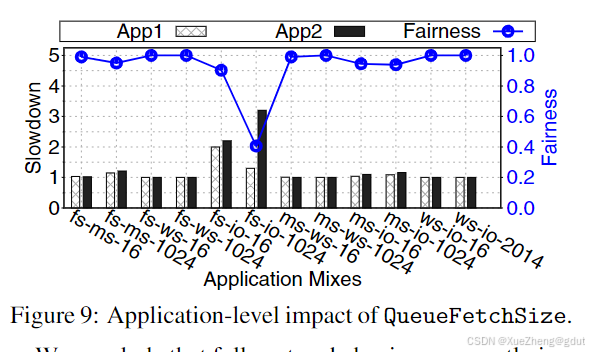

了研究SSD设备级设计选择对应用程序级性能指标(如每周期指令数IPC)的影响,SSD模拟器必须与全系统模拟器集成并一起运行。我们通过将MQSim与gem5 [8]集成,提供了一个完整的多队列I/O执行和完整计算机系统的模型。如表2所示,在现有的SSD模拟器中,只有SimpleSSD [35]与全系统模拟器集成,但SimpleSSD不支持多队列I/O执行。在本节中,我们通过研究QueueFetchSize(见第4.2.1节)的变化如何影响由于存储级干扰而导致的并发执行应用程序的IPC,来展示我们集成模拟器的有效性。

我们使用集成执行模式的MQSim运行文件服务器(fs)[77]、邮件服务器(ms)[77]、Web服务器(ws)[77]和IOzone大文件访问(io)[62]应用程序的实例。我们首先单独运行每个应用程序(即,没有来自其他应用程序的干扰),然后并发运行一个应用程序与另一个应用程序,以研究应用程序间的干扰效果。为了隔离存储级干扰的影响(每个流属于一个应用程序),我们将每个应用程序分配给一个单独的处理器核心和一个单独的内存通道。我们测试了两个不同的QueueFetchSize值(16个条目和1024个条目),以查看QueueFetchSize如何影响应用程序间的干扰。对于这些实验,我们测量了应用程序的减速比(Sapp),计算公式为:

图9显示了六对并发执行应用程序的每个应用程序的减速比和系统公平性。在x轴上,我们列出了每对应用程序中使用的应用程序,以及我们使用的QueueFetchSize值。我们从图中得出了两个观察结果。首先,对于应用程序对中包含ms或ws的应用程序,QueueFetchSize对公平性的影响可以忽略不计。ms和ws主要通过将大部分数据集缓存在主内存中受益,因此很少向SSD发出请求。这使得存储级干扰保持在较低水平,因为ms和ws不会经常与其他应用程序竞争对SSD的访问。其次,fs和io具有较高的存储访问强度,因此当它们配对时会显著干扰。在这种情况下,我们观察到较大的QueueFetchSize值会导致公平性显著下降(降低60%)。

我们得出结论,全系统行为可以显著影响MQ-SSD上I/O流的公平性和性能,因为它影响每个流的存储级强度。

7 Related Work

据我们所知,MQSim是第一个能够(1)准确模拟现代和传统SSD,(2)忠实建模现代主机接口协议(如NVMe),以及(3)支持使用新兴超快速存储技术的SSD的准确模拟的模拟器。我们在第5节中将MQSim与现有的最先进的SSD模拟工具进行了比较,并展示了MQSim提供了更强大的功能和准确的结果。在本节中,我们简要总结其他相关工作。

许多先前的研究考虑了多队列固态硬盘(MQ-SSD)的性能和实现挑战 [5, 31, 89, 90]。Xu等人 [89] 分析了MQ-SSD对现代超大规模和数据库应用性能的影响。Awad等人 [5] 评估了不同NVMe主机接口实现对系统性能的影响。Vuˇcini´c等人 [83] 指出,当前的NVMe协议将成为未来PCM(相变存储器)基础存储设备的性能瓶颈。作者们修改了NVMe标准,以提高其在未来PCM基础SSD中的性能。其他研究 [31, 72] 关注于管理现代SSD中的多个流。Song和Yang [72] 将SSD后端资源分配给并发运行的I/O流,以提供性能隔离并减轻流间干扰。Jun和Shin [31] 提出了一种适用于MQ-SSD的设备级调度技术,并支持虚拟化。这些先前的研究均未提供MQ-SSD的模拟框架,也未研究MQ-SSD内部的流间干扰来源。

8 Conclusion

我们介绍了MQSim,这是一个新的模拟器,能够准确地模拟现代多队列固态硬盘(SSD)和传统基于SATA的SSD的行为。MQSim忠实建模了现有先进模拟器所缺乏的多个关键特性,包括(1)现代基于多队列的主机接口协议(例如NVMe),(2)SSD的稳态行为,以及(3)I/O请求的端到端延迟。MQSim可以作为独立工具运行,也可以与全系统模拟器集成。我们通过对真实现成的SSD进行验证,证明了MQSim能够提供高度准确的结果。通过准确建模现代SSD,MQSim能够揭示现有模拟器无法准确模拟的重要问题,例如流量间干扰对性能的影响。我们已将MQSim作为开源工具发布(https://github.com/CMU-SAFARI/MQSim),希望它能够帮助研究人员探索新的想法和方向。

A MQSim Validation

A.1 Evaluation Methodology

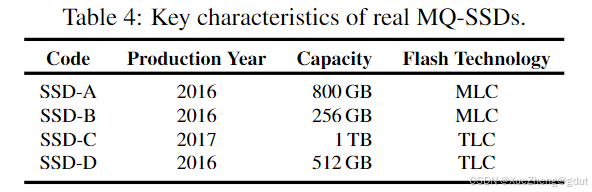

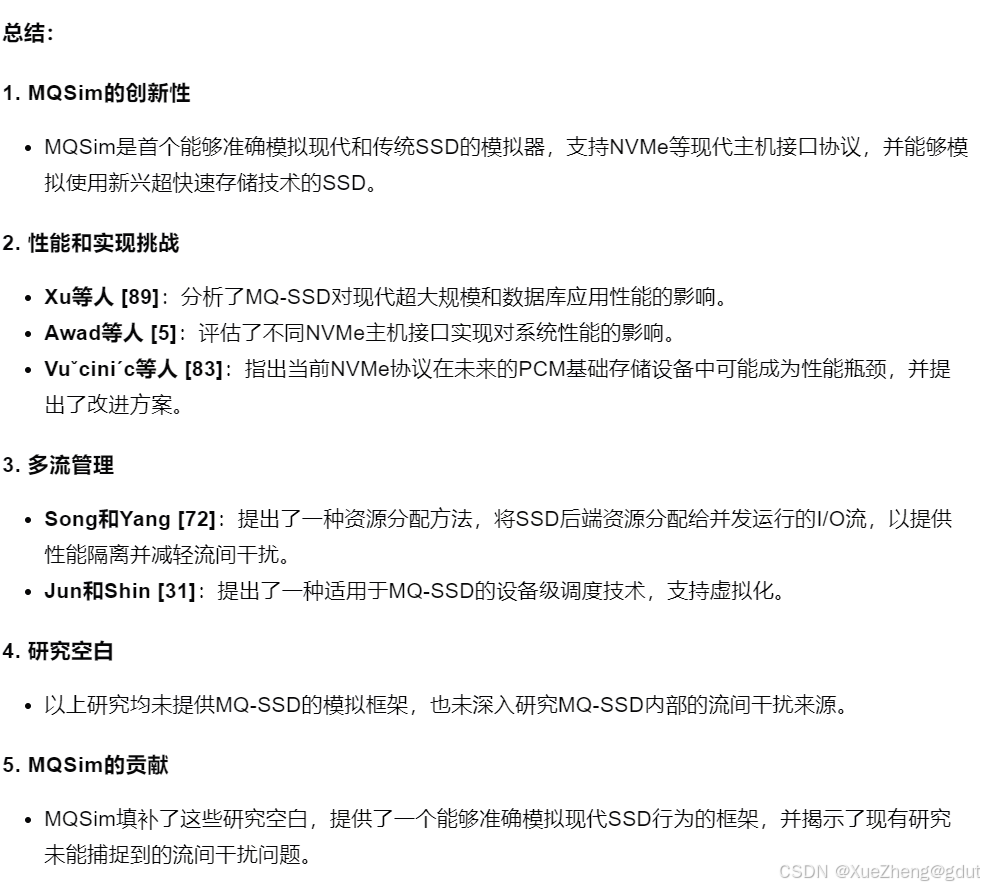

为了验证MQSim的准确性,我们将MQSim的性能结果与四款2016年至2017年间生产的最先进的多队列固态硬盘(MQ-SSD,分别命名为SSD-A、SSD-B、SSD-C和SSD-D)进行了比较。表4列出了这四款MQ-SSD的关键特性。我们对每款设备进行了全负载写入操作,以写入70%的可用逻辑空间[71]。设备预处理过程包括两个阶段,每个阶段持续4小时。在第一阶段,我们执行顺序写入操作;在第二阶段,我们执行随机写入操作。我们在一台包含Intel Xeon E3-1240 v6 3.70GHz处理器和32GB DDR4内存的服务器上进行真实系统实验。系统使用Ubuntu 16.04.2,搭载2.6.27版本的Linux内核,操作系统安装在一块500GB的Western Digital硬盘上。我们使用fio基准测试工具进行性能评估,所有存储设备均通过PCIe总线连接作为附加卡。

我们使用四种不同的配置来验证我们的模拟器,这些配置分别对应于我们实际的四款多队列固态硬盘(MQ-SSD)。为了实现这一目标,我们使用微基准测试程序提取每款实际SSD的主要结构参数。该程序基于先前的SSD建模研究[14, 15, 36]中描述的方法,分析并估计SSD的内部配置(例如,NAND闪存页面大小、NAND闪存读写延迟、SSD中的通道数量、地址映射策略、写入缓存大小等)。我们已经开源了我们的微基准测试程序[1]。对于垃圾回收(GC)管理,我们在MQSim中启用了所有高级GC机制(除了写入暂停,因为根据所使用的两种闪存芯片的规格,写入暂停不被支持)。

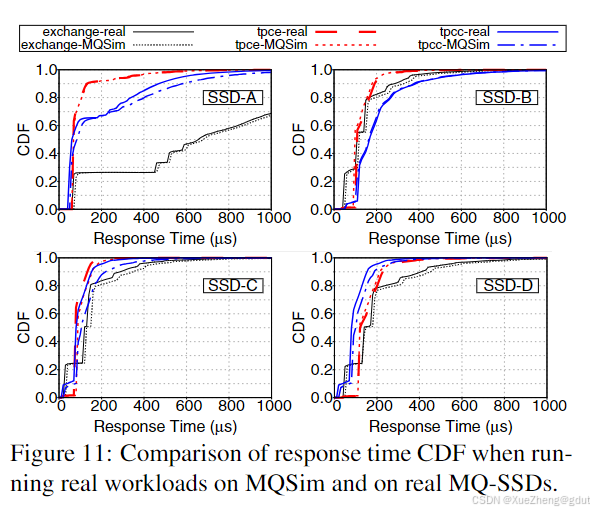

A.2 Performance Validation

我们使用合成和真实工作负载对MQSim进行验证。合成工作负载发出随机访问请求,仅包含读请求或写请求,队列深度设置为1个请求。图10比较了在四款真实MQ-SSD设备上测量的读写请求响应时间与MQSim报告的延迟。图10a和10b分别显示了读和写延迟。x轴表示不同的I/O请求大小,范围从4 kB到1 MB。蓝色曲线显示了模拟模型的误差百分比。我们发现,MQSim报告的响应时间与真实设备的测量结果非常接近,尤其是在SSD-B和SSD-D上。平均而言,对于所有四种MQ-SSD和所有I/O请求大小,读和写请求的误差率分别为2.9%和4.9%。图11以累积分布函数(CDF)的形式显示了MQSim报告的请求响应时间的准确性,针对三个真实工作负载[53]:tpcc、tpce和exchange。我们发现,MQSim报告的响应时间与真实MQ-SSD上测量的响应时间非常接近。SSD-A、SSD-B、SSD-C和SSD-D的平均误差率分别为8%、6%、18%和14%。我们得出结论,MQSim能够准确模拟真实MQ-SSD的性能。

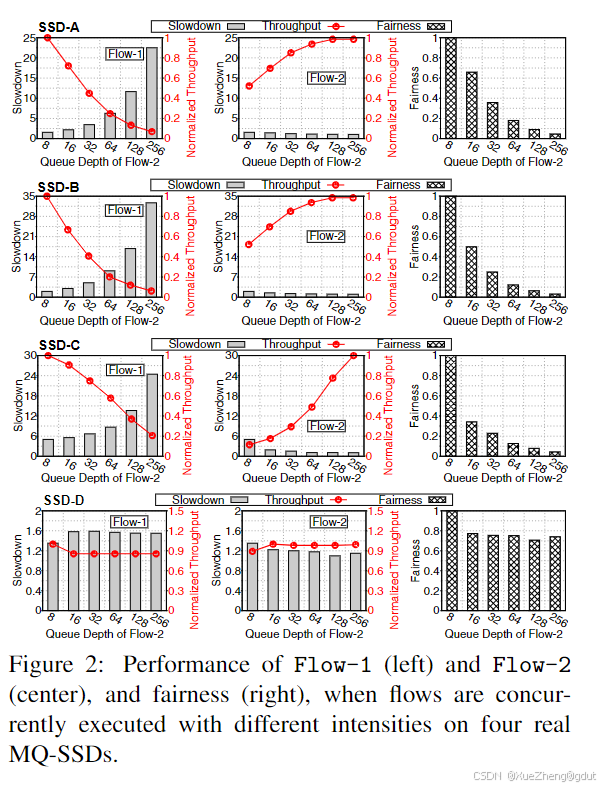

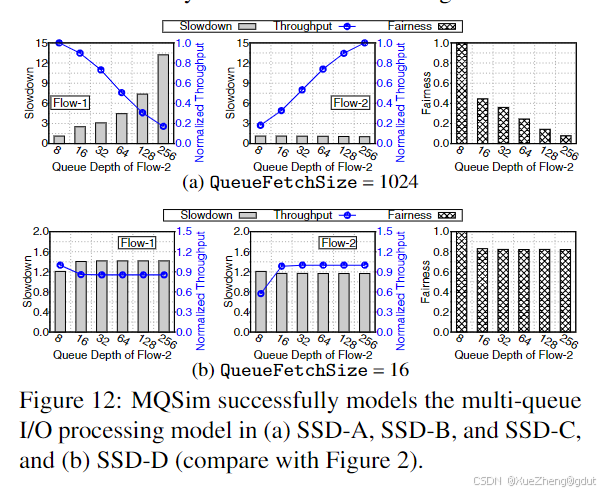

A.3 Multi-Queue Simulation

为了验证MQSim中多队列I/O执行模型的准确性,我们进行了一系列模拟实验,使用了两个I/O流(Flow-1和Flow-2),每个流仅生成顺序读取请求。我们保持Flow-1的请求强度不变,将其I/O队列深度设置为8个请求。我们通过改变Flow-2的I/O队列深度(从8个条目到256个条目)来控制Flow-2的强度。对于每个Flow-2的I/O队列深度,我们测试了两个不同的QueueFetchSize值(16和1024,见第4.2.1节)。图12展示了Flow-1(左侧)和Flow-2(中间)的减速比和归一化吞吐量(IOPS),以及系统的公平性(见第3.1节)。我们从图中得出了两个关键观察结果。

首先,我们发现当QueueFetchSize设置为1024时,MQSim成功地模拟了那些针对每个流的高吞吐量进行优化的实际MQ-SSD的行为(例如SSD-A、SSD-B、SSD-C)。图12a显示了与我们在实际MQ-SSD上进行的测量结果相似的减速比、吞吐量和公平性趋势(见图2)。当QueueFetchSize设置为1024时,每个流的更多I/O请求被取入MQ-SSD的设备级队列。在我们的MQSim结果和实际MQ-SSD的测量结果中,我们都观察到,随着Flow-2强度的增加,其吞吐量显著增加且几乎不减速,而Flow-1的吞吐量显著下降,导致Flow-1大幅减速。这是因为当Flow-2强度较高时,它不公平地占用了MQ-SSD后端的大部分资源,导致Flow-1的请求需要等待更长时间才能得到服务。

其次,当QueueFetchSize设置为16时,MQSim准确地模拟了那些实现了控制流间干扰机制的实际MQ-SSD产品(例如SSD-D)。图12b中显示的趋势与我们在图2中观察到的SSD-D的实际测量结果相似。当QueueFetchSize设置为16时,后端仅服务每个并发运行流的有限数量的I/O请求,防止任何一个流不公平地占用MQ-SSD内的大部分资源。因此,即使Flow-2强度很高,Flow-1也不会经历显著的减速。

我们得出结论,通过调整QueueFetchSize,MQSim能够成功地模拟现代MQ-SSD设备中不同的多队列I/O处理机制。

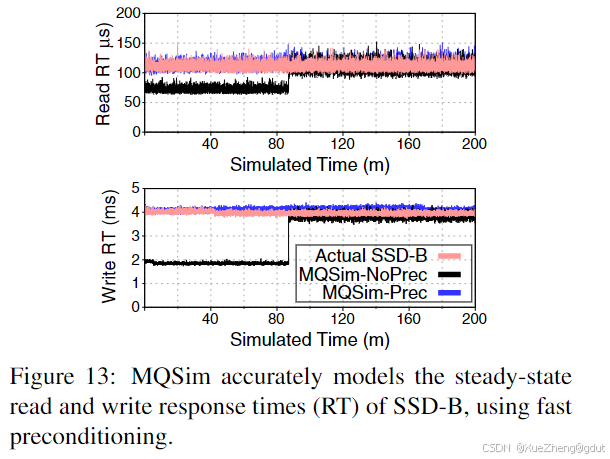

A.4 Steady-State Behavior Modeling

正如我们在第4.4节中讨论的,MQSim假设所有模拟都应该在模拟设备处于稳态时执行。为了建模稳态行为,MQSim默认在实际模拟过程开始之前自动执行一个预处理函数。该函数在短时间内(例如,在800 GB的MQ-SSD上运行tpcc [53]时少于8分钟)将所有可用的物理页面转换为有效或无效状态,基于提供的稳态有效/无效页面分布模型[82](只有少数闪存块保持为空闲并添加到空闲块池中)。MQSim预处理输入跟踪以提取应用I/O请求的逻辑页面地址(LPA)访问特征,并将提取的信息作为输入提供给有效/无效页面分布模型。此外,输入跟踪特征(如平均写入到达率和写入地址分布)用于预热写入缓存。

为了验证MQSim中的稳态模型,我们在高写入强度下使用MQSim进行一系列实验,并将结果与实际MQ-SSD设备的结果进行比较。图13绘制了(1)在SSD-B上实际执行I/O操作的读写响应时间(SSD-B代表我们评估的最先进的SSD的典型行为);(2)MQSim-NoPrec,即MQSim在没有预处理的情况下运行;(3)MQSim-Prec,即MQSim在有预处理的情况下运行。

我们从图中得出两个观察结果。首先,经过预处理的MQSim成功地跟随了从SSD-B提取的响应时间结果。其次,未经过预处理的MQSim在实验开始时报告了较低的响应时间结果,因为模拟的SSD尚未进入稳态。一旦整个存储空间被写入,响应时间结果变得与实际设备相似,因为模拟中的垃圾回收和写入缓存驱逐现在以与SSD-B上测量的速率相似的速率发生。我们得出结论,MQSim的预处理能够快速且准确地建模实际MQ-SSD的稳态行为。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?