大多数arm芯片从0开始启动

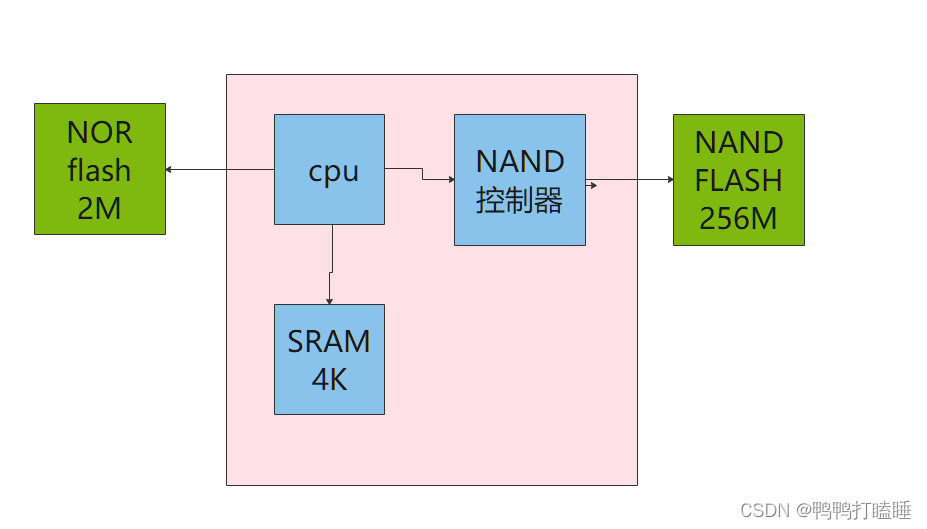

nand_flash控制器外接nand_flash 256M

cpu直接接nor_flash 2M

nor_flash启动时候 nor_flash上面烧了bin文件 nor_flash基地址为0

cpu直接读nor上的第一个指令(前4字节),执行

cpu继续读取其他指令 执行

如果使用nor启动,片内的sram的地址就是 0x4000,0000

nand_启动 片内4kram 基地址为0()cpu都从0开始启动

2440硬件把nand前4K内容复制到片内内存sram,cpu从0地址开始启动 从0地址取出第一条指令

如果用 nand启动0地址对应的是片内的ram 这时候nor_flash不能访问 也就是设置nand_flash 就用不了nor_flash

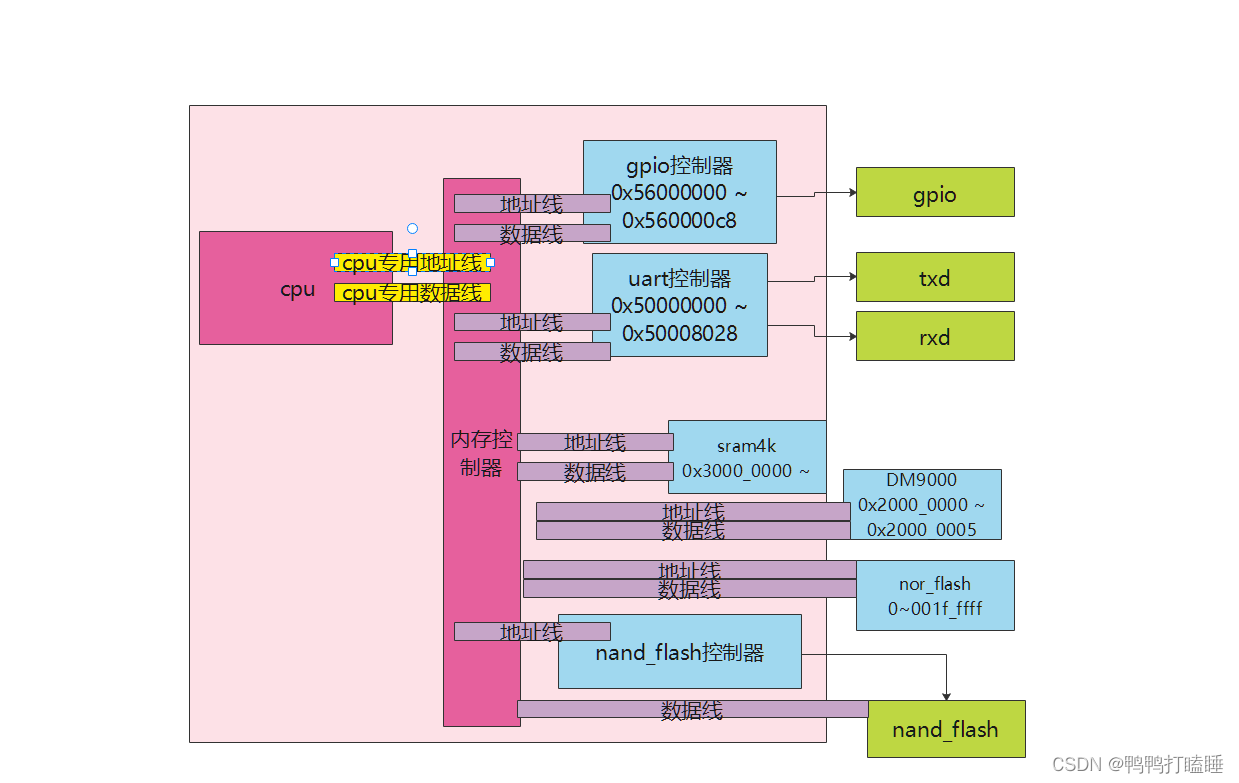

cpu写的寄存器地址,映射关系

soc上面有很多的控制器 比如 gpio控制器 uart控制器

cpu根据地址把某些值写给某些寄存器 这些对应的控制器就会发出特定的波形 满足特点的时序

因为根据地址把某些值写个某些寄存器 所以有一个新的控制单元 叫内存控制器

cpu把地址给内存控制器 内存控制来选择不同的模块 模块把数据给内存控制器 内存控制器再给cpu

一般接口中cpu发送的信号并不会传输到外面 (如gpio的管脚上拉下拉) 只是给到gpio控制器

特殊接口中 --> 内存接口(nor flash 网卡 sdram这些接口 注意nandflash不是) cpu发出来的地址会直接传给这个设备

问:cpu的地址总线和数据总线 都连接到了 nor flash 网卡 sdram 怎么才会互不干扰

答有个片选引脚 只有片选引脚状态置位 说明地址和数据总线在这上面交互

问: 给个全部图

gpio控制器 uart控制器 iic控制器 到片外的 sdram dm9000 norflash 都参与cpu的统一编址

cup也能访问nand flash控制器 nand_flash不属于cpu统一编址

nand_flash从原理图看 数据线可以从cpu得到 但是地址线没有 nand_flash不参与cpu统一编址 但是nand_flash 也在data线上

为了数据线上有数据的时候 nand_flash不受干扰 也有nand_flash一个片选信号 被nand_flash控制器控制

只有cpu访问nand_flash控制器的某个寄存器 这个nand_flash 片选信号才有用

浅蓝色都参与cpu的统一编址,cpu发送的地址能直接给这些设备 ,浅绿色通过控制器进行控制

问: 谁来控制片选引脚?

答:内存控制器 当cpu根据指令发出地址信号 发到内存控制器 内存控制器根据地址来控制片选引脚

问:地址和片段信号的关系怎么确认

答:datasheet 第五章有个memory_control

当使用norflash 启动时候 如果地址在 0x0000_0000~ 0x0800_0000 内存控制器会让 nGCS0输出低电平

使用nandfalsh启动时候 CPU认为的0地址 是片内的4kram 如果想获取nand_flash的0地址 只能操作nand_flash控制器去发送

自己的感觉是什么

https://www.eetopic.com/article/61725.html

自己感觉是 cpu发出的全部寄存器地址都要给内存控制器,内存控制器根据寄存器地址 来进行数据的输出和拿取

低于4000_000 当作内存,需要调用内存控制器的时序在数据线和地址线进行时序上的一些控制 更改数据传输给内存芯片

获取内存芯片的数据

如果高于这个地址,就是datasheet中的其他控制器寄存器地址,就把这个数据原封不动的给其他控制器了

问:地址的范围有多大呢

如图上的 0x0000_0000~ 0x0800_0000 = 134217728b(字节)/1024/1024 = 128M

所以每个片选信号能选择的空间范围为 128M = 2^27 也推算出至少需要 A0~A26 27根线才能访问完一个片选信号的空间

问:cpu怎么发出地址信号,为什么寄存器是32位的 数据线只有27根

比如ldr r0 = addr

str r1 [r0]

这些指令会让cpu把32位的addr 发给内存控制器

如果addr的范围是偏外的内存 内存控制器就会 发出块内存的片选信号 同时发出addr0,addr1...addr26 发送到外设

所以cpu确实发送到32位地址,但是内存控制器能力有限 只能控27根

问:为什么soc上的laddr1接到 芯片上的laddr0,为什么不是一一对应的接入呢

当使用8bitrom的时候 一一对应 使用两块芯片拼起来

一次读取的为16bit rom 因为拼接后读取的长度不一样 地址有所增加

反正cpu把想要的地址发送给内存控制器 内存控制器根据地址进行组装

不做过多解释

问:怎么根据原理图确定芯片访问地址

看见原理图上面片选引脚名字 对应datasheet里面 比如 :nGCS0

1.根据片选信号确定基地址

如nor_flash使用片选nGCS0 基地址为 0

用到A20~A0 21条线 a1~a20接到cpu发出的线,a0给内存控制器选择低八位还是高八位,共2^21 =2M

地址选中 范围 base~base+2^21 = 0~001f_ffff 访问nor_flash

如网卡dm9000使用片选nGCS4 基地址为 0x2000_0000

只接了addr2,没有addr1和0 还接了data15~data0(16位) ,最终内存控制器用addr0分辨低8位还是高8位

所以用到addr2和addr0 范围是 base +二进制0b00000000~ base +二进制0b00000101 = 0x2000_0000 ~ 0x2000_0005

地址选中0x2000_0000 ~ 0x2000_0005 访问dm9000网卡

如sdram使用片选nGCS6 基地址为 0x3000_0000

地址线接了laddr2~laddr14,laddr24,laddr25,17条地址线 2^17 =128k,但是因为分为列地址和行地址,地址总线用两次

cpu只是发送地址,给内存控制器进行选择发往哪个内存芯片,因为是sdram,内存控制器还要拆分为列地址和行地址再进行发送

2.根据连接的地址线确定范围

3210

3210

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?