前提知识:存储器芯片容量=单元数×数据线位数

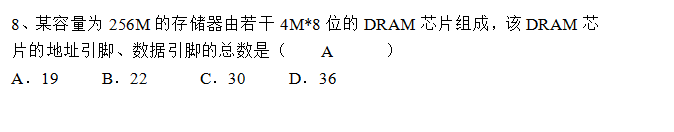

1、遇到的题目1–2014年统考题

因为DRAM芯片存储容量为 4M * 8位,因此可寻址范围是

4

∗

2

20

B

=

2

22

B

4*2^{20} B =2^{22} B

4∗220B=222B

按字节寻址,地址线应该为

l

o

g

2

(

2

22

)

=

22

根

log_2(2^{22})=22根

log2(222)=22根

而DRAM采用地址复用技术,地址线是原来的1/2根,且地址信息通过 行通选、列通选 分行、列两次传送。因此地址线数减半为11根,而数据线就是8根,就是同时能传输16位的数据,所以地址引脚与数据引脚的总数为

11

+

8

=

19

根

11+8=19根

11+8=19根

这里注意到,SRAM和DRAM的区别:DRAM采用地址复用技术,而SRAM不采用。

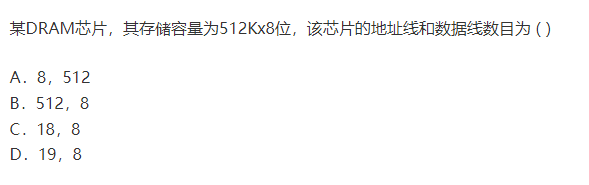

2、DRAM类似题目–某网站看到

-D

因为其存储容量是512K*8位,则它的数据线为8根,地址线数为

l

o

g

2

(

512

k

)

=

l

o

g

2

(

2

19

)

=

19

log_2(512k)=log_2(2 ^ {19})=19

log2(512k)=log2(219)=19

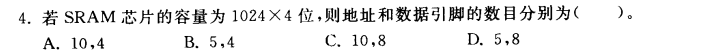

3、SRAM题目–某网站看到

-A

同上理,因此1024*4位芯片的地址引脚是10根,数据线是4根。

本文详细解析了存储器芯片容量的计算方式,包括DRAM和SRAM的地址线和数据线计算,强调了DRAM采用地址复用技术的特点。通过具体实例,如4M*8位DRAM和1024*4位SRAM的分析,阐述了如何确定存储器芯片的地址引脚和数据引脚数量。

本文详细解析了存储器芯片容量的计算方式,包括DRAM和SRAM的地址线和数据线计算,强调了DRAM采用地址复用技术的特点。通过具体实例,如4M*8位DRAM和1024*4位SRAM的分析,阐述了如何确定存储器芯片的地址引脚和数据引脚数量。

700

700

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?