1 HDL发展

1.1基础概念

IC(Integrated Circuit)集成电路:将逻辑门安装在单个芯片上。

SSI(Small Scale Integreted)小规模集成电路:逻辑门的数量很少

MSI(Medium Scale Integreted)中规模集成电路:逻辑门数量有上百个

LSI(Large Scale Integreted)大规模集成电路:数千个逻辑门

EDA(Electronic Design Automation):电子设计自动化,因为LSI的设计过程变得复杂,希望设计阶段自动完成而出现的概念。(早期都是在面包板上测试)

VLSI(Vert Large Scale Integrated)超大规模集成电路,不可能在面包板上验证,出现逻辑仿真工具验证(可以尽早排除设计结构中存在的问题),模块化搭建高层功能模块。

CAD(Computer-Aided-Design)计算机辅助设计:完成布局,布线,芯片版图绘制工作的工具

CAE(Computer-Aided-Engineering)计算机辅助工程:HDL仿真、逻辑综合、时序分析的工具

EDA包含CAD与CAE,所有设计工具。

HDL(Hardware Description Languages)硬件设计语言(硬件设计领域,设计人员希望使用标准语言进行硬件设计)

RTL寄存器传输级(Register Transfer Level):设计者说明数据如何在寄存器中移动,等,逻辑综合工具自动从RTL描述中提取出来

HDL也可以单独设计每个芯片,仿真验证系统功能

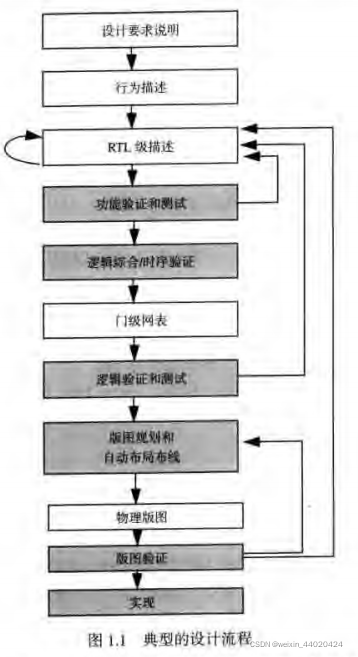

1.2典型设计流程

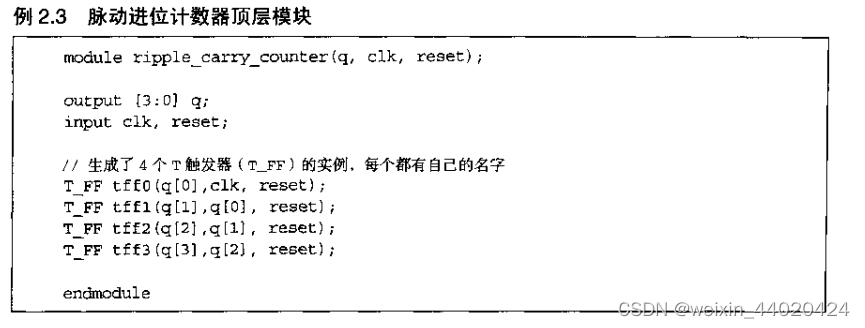

2 层次建模

2.1设计理念

数字电路设计中有底层向上和自顶向下设计方法。

自顶向下:首先定义顶层功能模块,分析顶层功能模块必要的子模块,在分解子模块,直到无法分解。

自底向上:根据现有功能模块不断组合

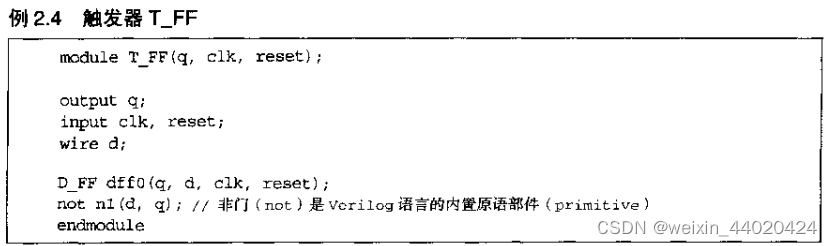

2.2模块

Verilog使用模块(module)概念代表一个基本功能模块。组合模块构建新的功能模块,实现代码重用,隐藏内部细节等。

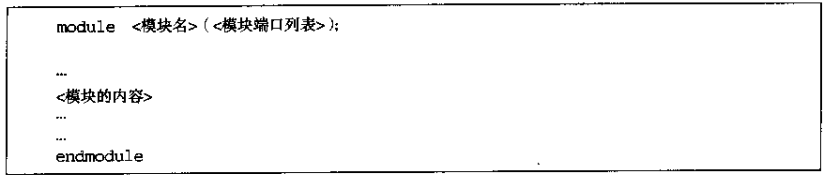

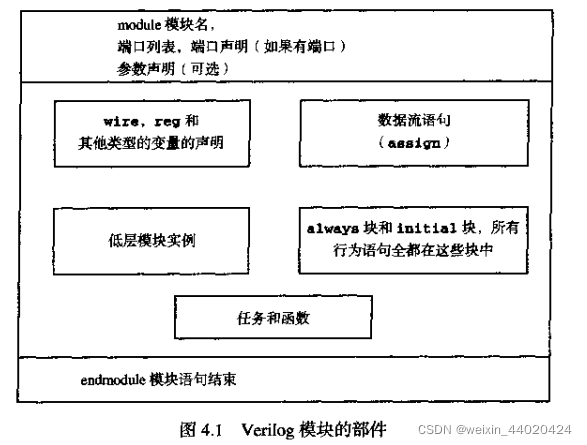

模块语法(声明)

- 模块声明以module开始,以endmodule结尾,

- 每个模块必须具有一个模块名,唯一标识这个模块

- 端口列表描述模块的输入和输出端口

- 功能描述放置于module与endmodule中间

- "//"表示单行注释

- 模块内不允许嵌套模块

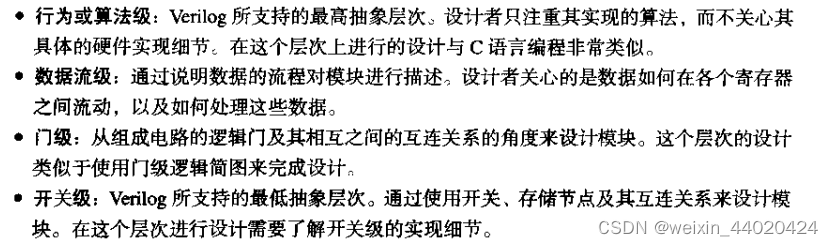

模块内部的四个抽象层次,

模块内部的四个抽象层次, - 模块内部抽象层次的更改不会影响外部环境。

- 允许在一个模块内混用多个抽象层次。

- 抽象层次越高,灵活性艺术无关性提高,反之降低

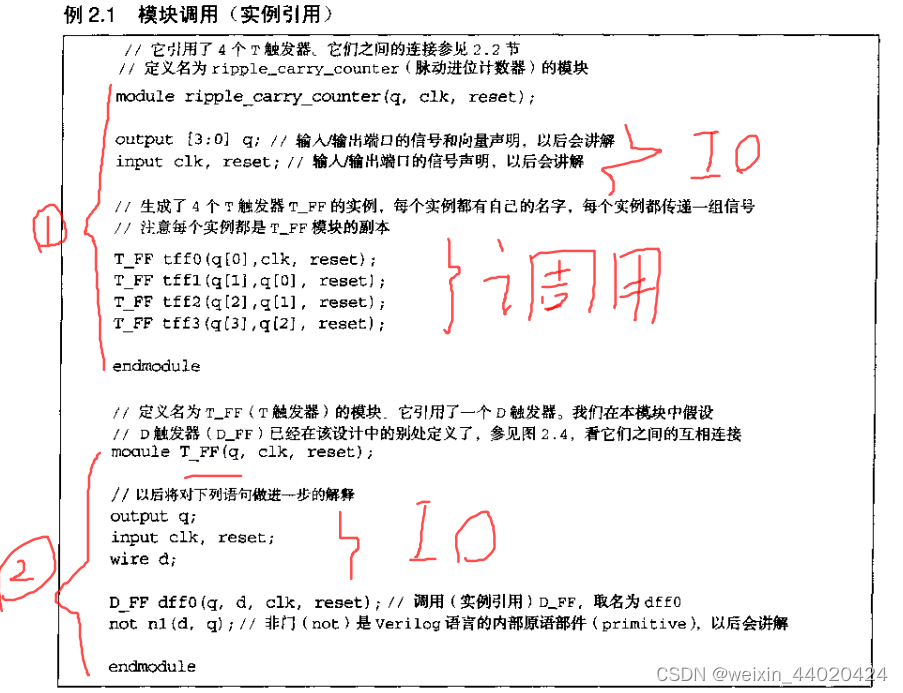

2.3 模块实例

模块声明是一个模板,通过模板创建实际对象。

从模板创建对象的过程称为实例化(instantiation),创建的对象称为实例(instance)。

展示了输入输出端口如何定义,模块如何调用。

2.5逻辑仿真的构成

如果队设计的正确性进行测试?

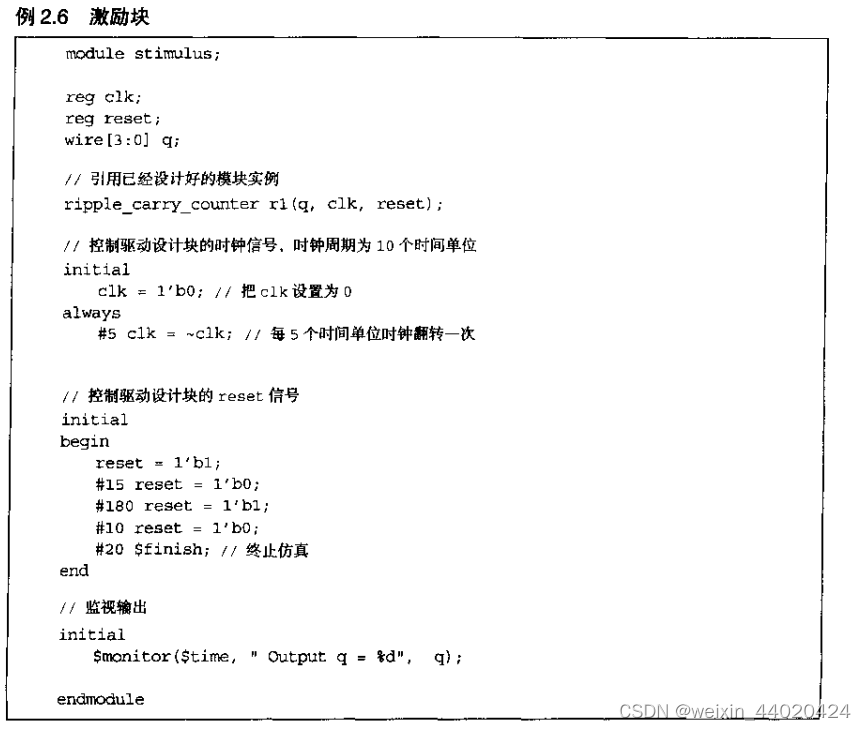

对设计模块施加激励,检测输出来验证功能的正确性。完成测试功能的块称为激励块(又叫测试台test bench)

激励块有两种模式,

1、激励块调用测试模块。

2、虚拟顶层模块调用激励块和测试模块。

2.5设计块

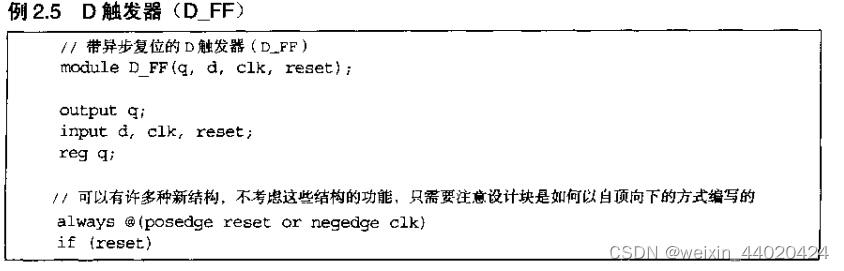

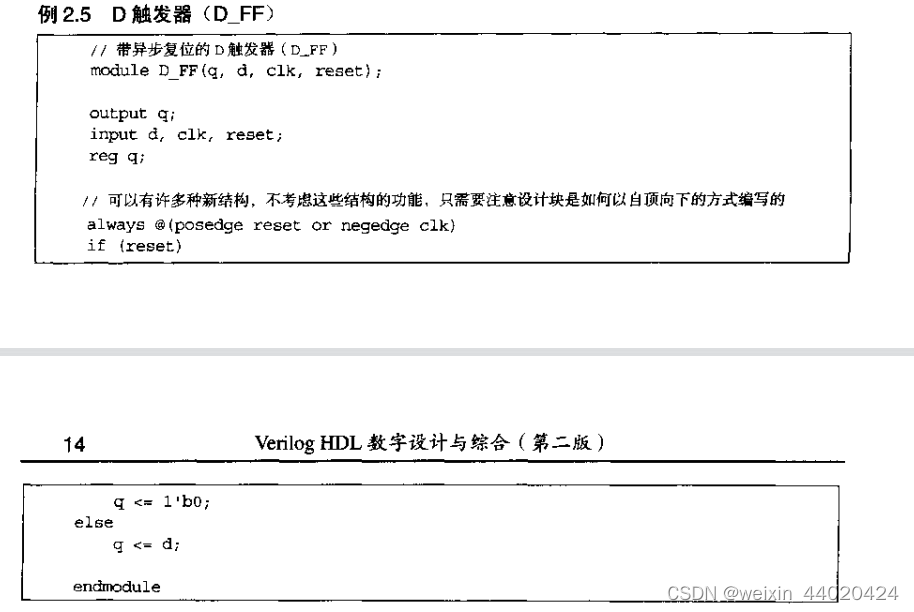

1、D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

3基本概念

3.1词法约定

1、Verilog大小写敏感,关键词都为小写

2、空白符由\b为空格,\t为制表符,和换行符组成。空白符的唯一作用是分割标识符,编译期间忽略

3、多行注释以/开头/结束

4、单行注释为//

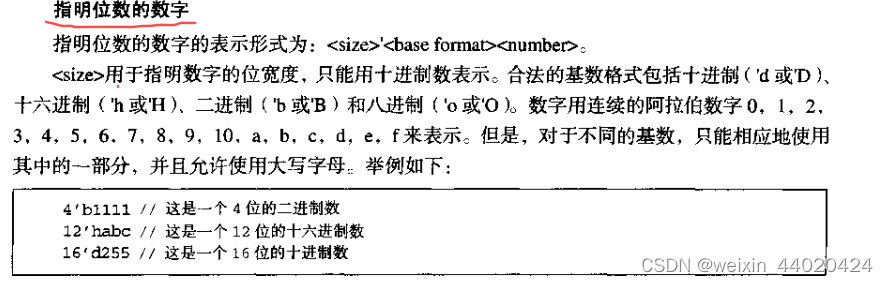

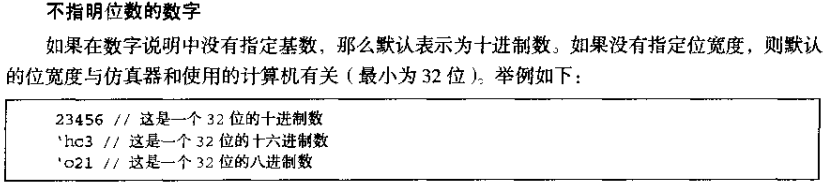

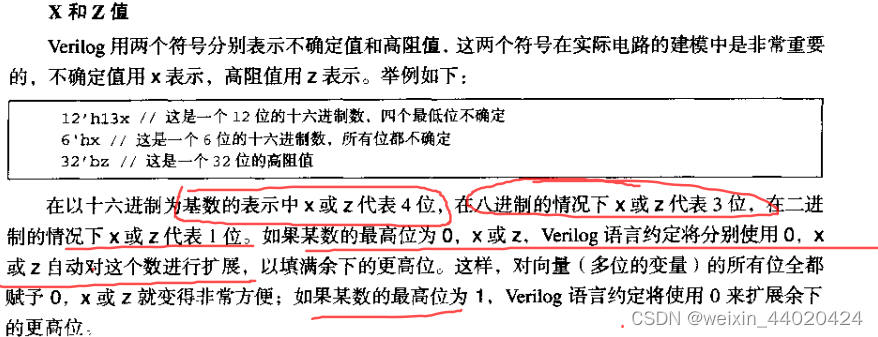

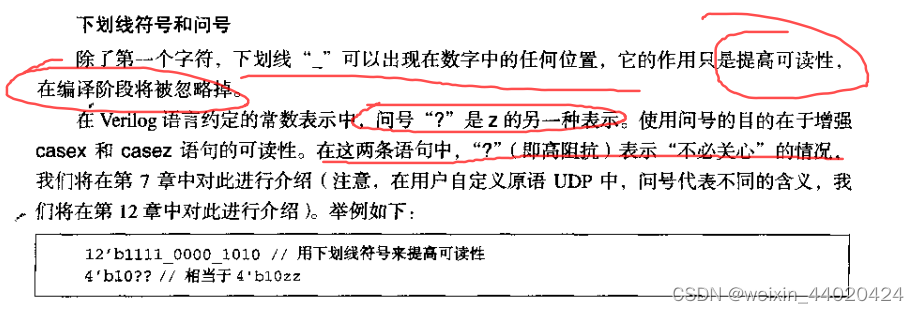

5、数字的表示方法

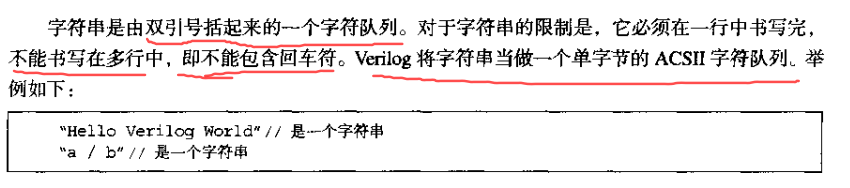

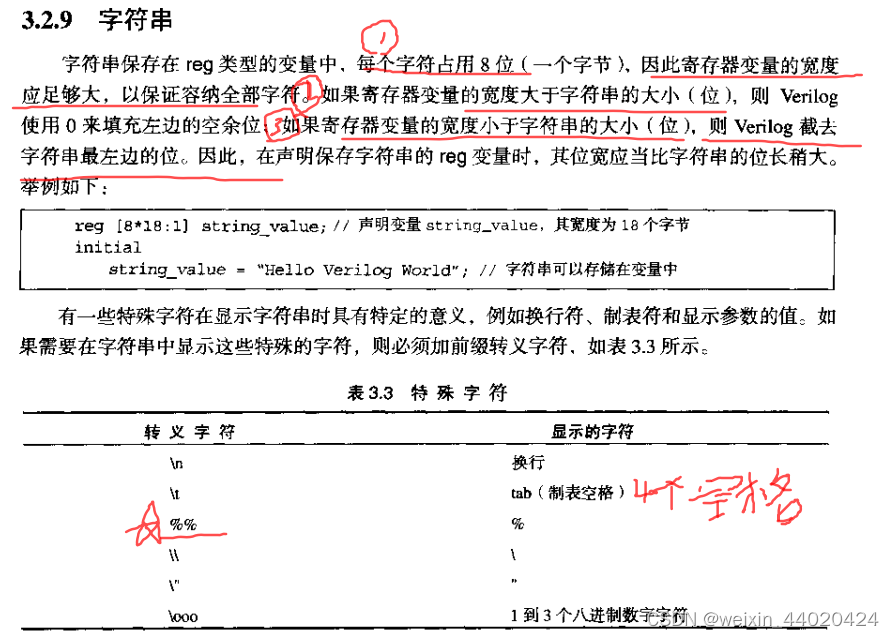

6、字符串

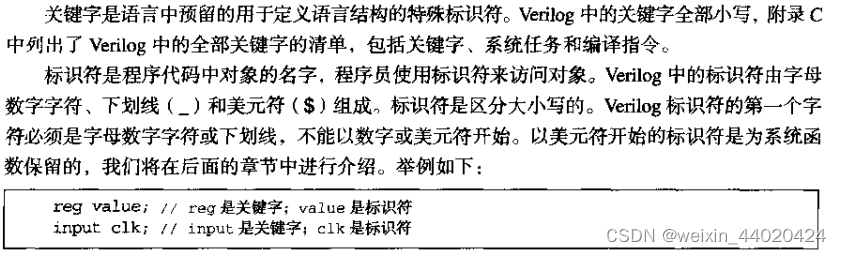

7、标识符

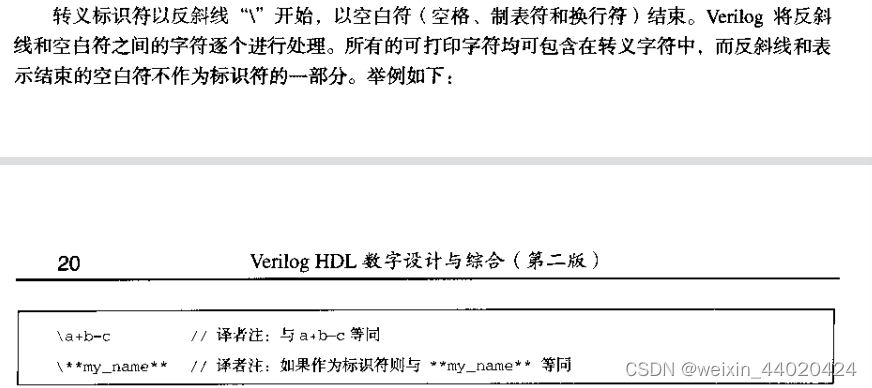

8、转义字符

3.2 数据类型

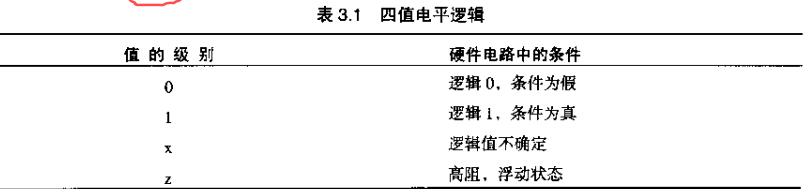

3.2.1 值的种类

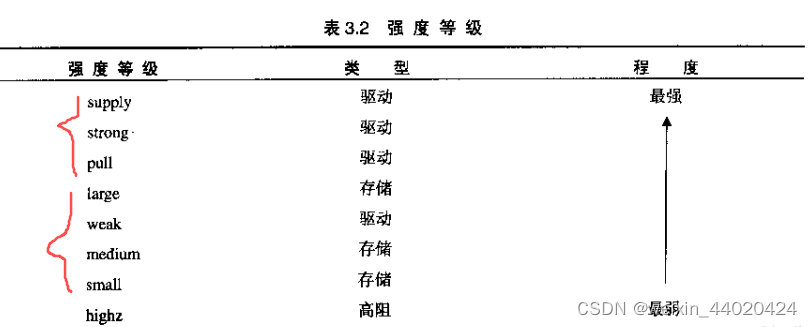

Verilog使用四值逻辑和八种信号强度来对实际的硬件电路建模

当不同强度的信号驱动同一个线网,则竞争结果值为高强度信号的值。

当相同强度的信号驱动同一个线网,则竞争结果为不确定值

如果两个强度为strong1和strong0的信号之间发生竞争,则结果为x

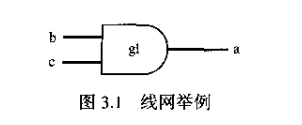

3.2.2 线网

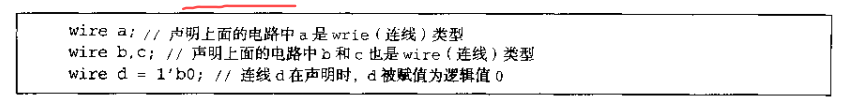

线网表示硬件单元之间的连接。

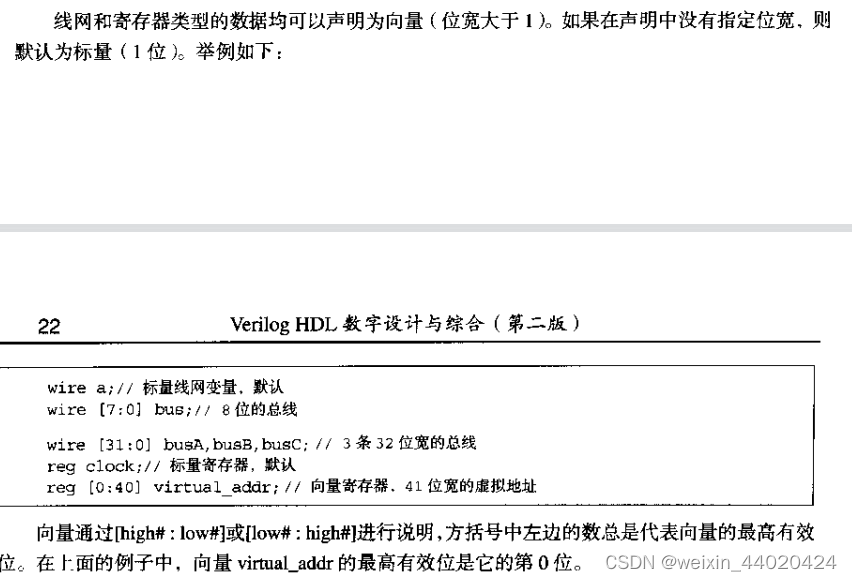

线网一般使用关键字wire进行声明,如果没有显示说明为向量,则默认线网的位宽为1,wire这个术语和net经常互换使用,线网的默认值为z,线网的值由其驱动源确定。

如果没有驱动源,则线网的值为z。

net代表一组关键词,包括wire,wand,wor,tri,triand,trior。

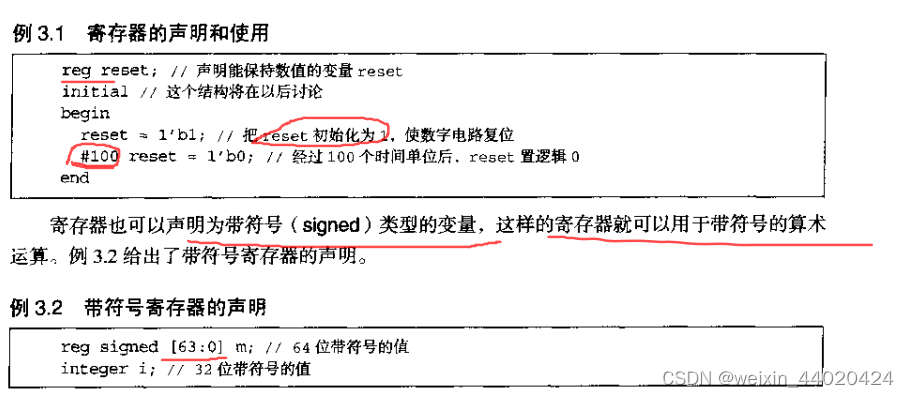

3.2.3寄存器

寄存器用来表示储存元件,它保持原有的数值,直到被改写。在verilog中register仅仅意味着一个保存数值的变量。寄存器不需要驱动源,也不需要时钟信号,任何时刻都可以通过赋值来改变。

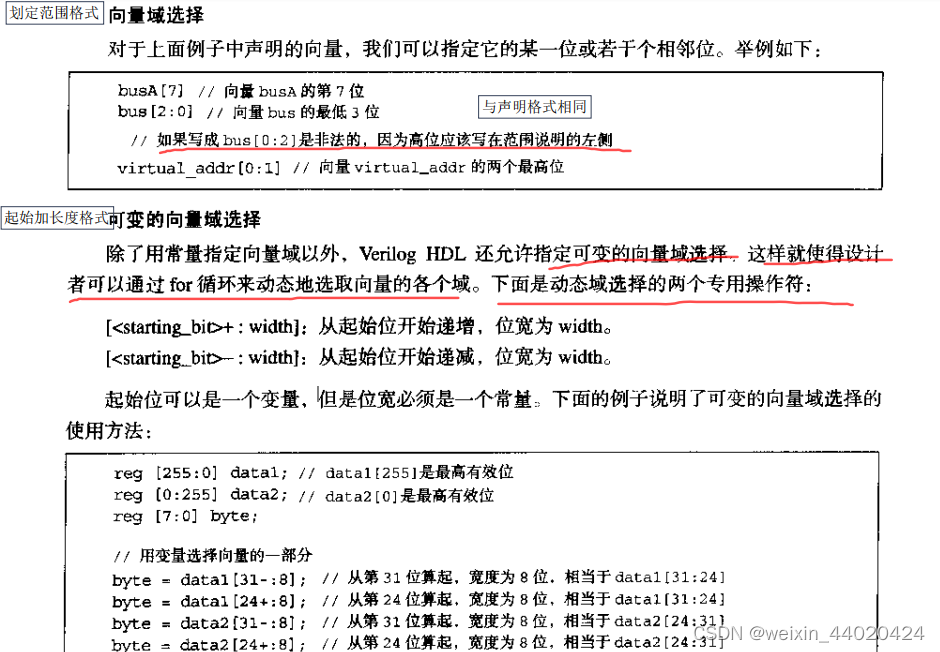

3.2.4向量

3.2.5其他数据类型

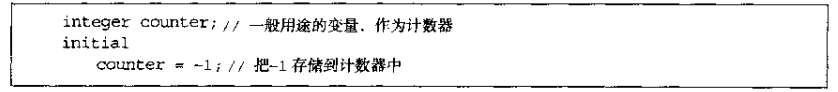

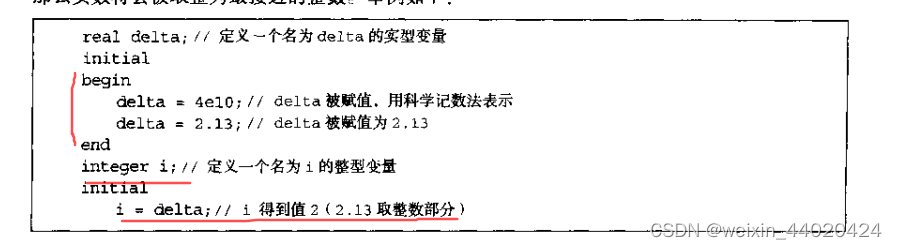

整数声明方法integer声明,默认宽度为宿主机的位数,与具体实现有关,但最小应为32位、为有符号数。

实数,实常量和实数寄存器数据类型使用关键字real来声明,可以用十进制或科学记数法来标识。实数声明不能带有范围,其默认值为0。如果将一个实数赋给一个整数,那么这个整数将会被取整为最接近的整数。

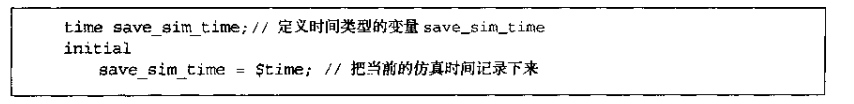

时间寄存器,verilog使用一个特殊的时间寄存器数据类型来保存仿真时间,时间变量通过使用关键字time来定义,其宽度与具体实现有关,最小为64位。通过调用系统函数¥time可以得到当前仿真时间。

以秒为单位。

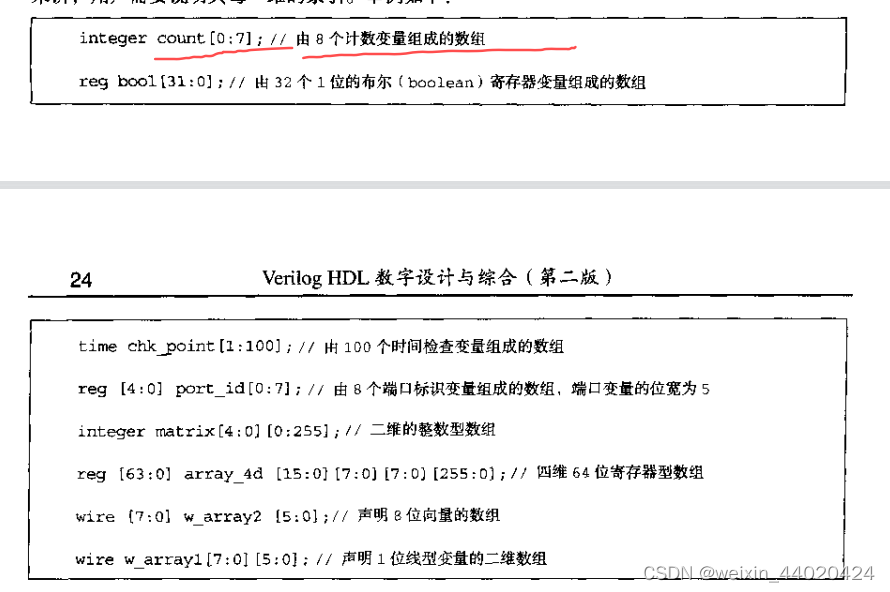

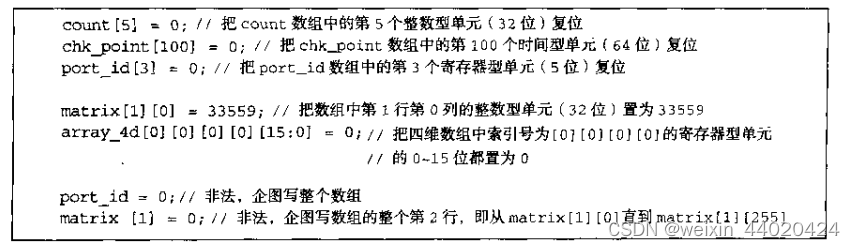

3.2.6 数组

在Verilog中允许声明reg,integer,time,real,realtime及其向量类型的数组,对数组的维数没有限制,即可以声明任意维数的数组。线网数组也可用于连接实例的端口,数组中每个元素都可以作为一个标量或者向量。

数组和位宽的区别为,位宽声明在类型后,数组声明在变量名后。

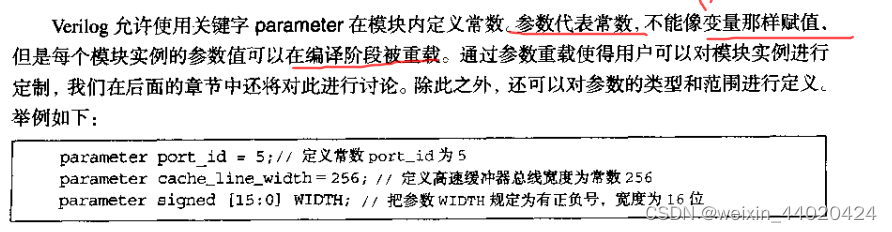

3.2.8参数

3.3系统任务和编译指令

3.3.1 系统任务

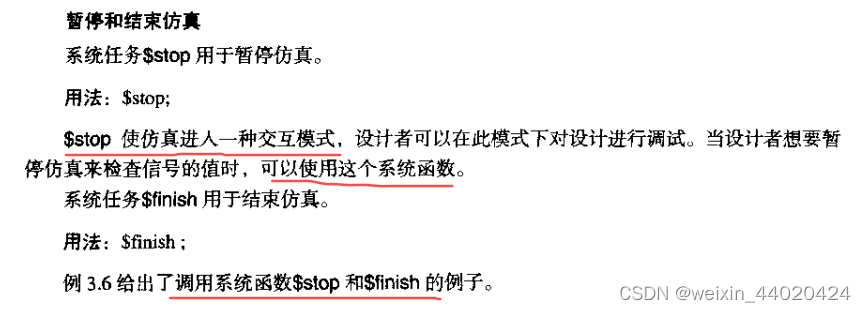

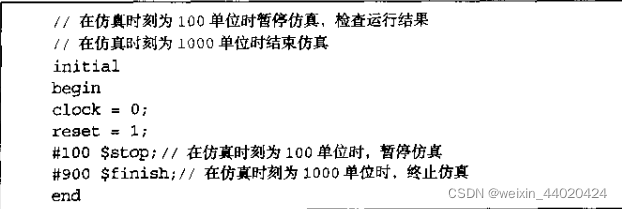

为某些常用操作提供了标准的系统任务

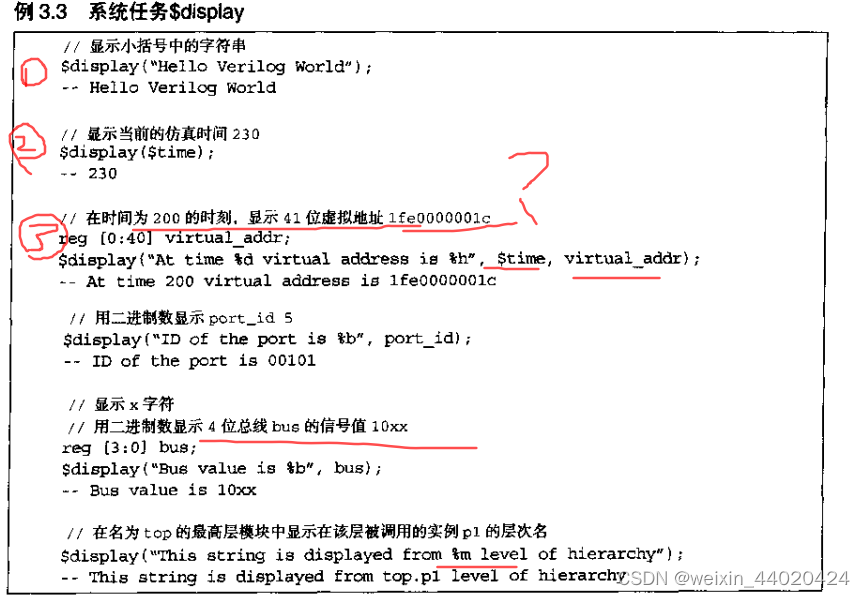

1、显示信息

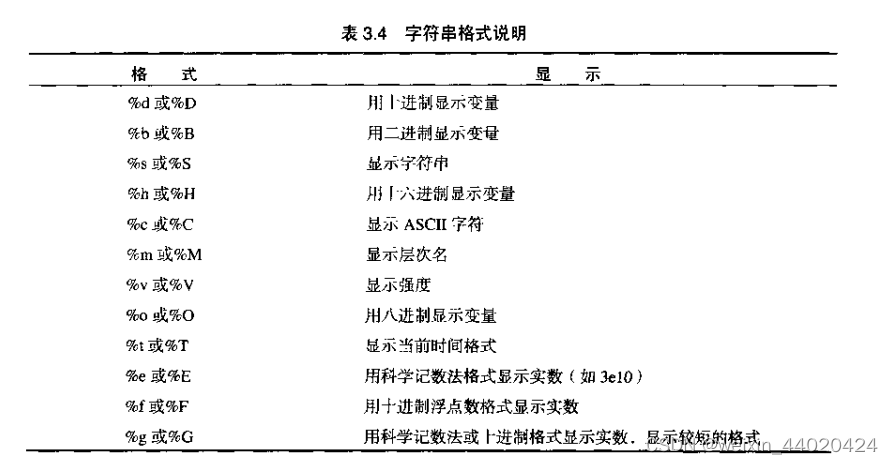

¥display是用于显示变量,字符串或表达式的主要系统任务。会自动在末尾后插入换行符

2、监视信息

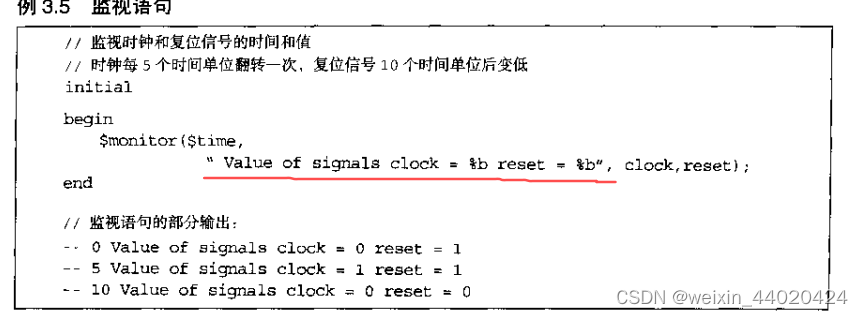

¥monitor为用户提供对信号值变化进行动态监控的手段。

¥monitor(p1,p2,p3,…,pn)

参数p1,p2,p3…,pn可以是变量,信号量或双引号括起来的字符串。对参数列表的变量值或者信号值进行不间断监视,当其中任何一个发生变化是,显示所有参数的数组。

只需调用一次即可在所有仿真过程中生效。任何时刻只有一个监视列表有效,如果用户在源描述中调用了多个监视信息只有最后一次调用生效。前面调用被覆盖。

¥monitoron:允许监视,默认状态是允许监视

¥monitoroff:暂停监视,

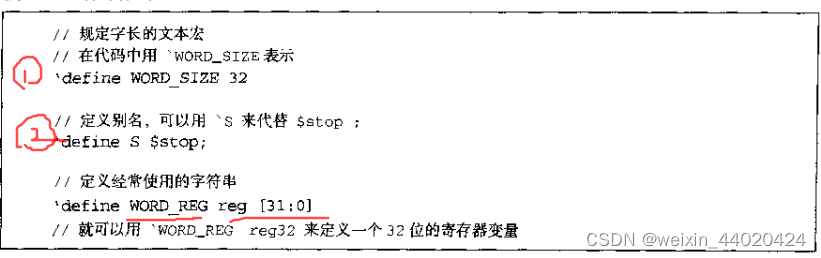

`define用于定义Verilog中的文本宏,使用预定义的文本宏替换宏名。

include可以在编译期间将一个Verilog源文件包含在另一个Verilog文件中,作用类似于c语言中的#include结构。通常将内含全局或公用定义的头文件包含在设计文件中。

模块和端口

中间部分可以随意组合可有可无

4.2端口

端口是模块与外界环境交互的接口,例如IC芯片的输入、输出引脚就是他的端口。对于外部环境来说,模块内部是不可见的。

端口是可选的,如果一个模块不需要任何交换信号,可以没有端口列表。

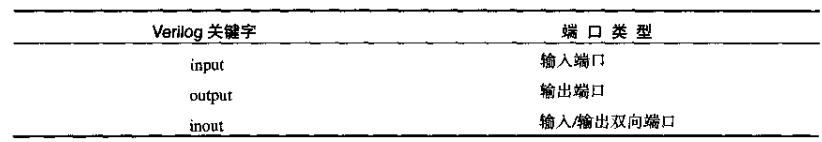

端口声明,端口列表中的端口必须在模块中进行声明,Verilog中的端口具有以下三种类型:

4.2.3端口连接规则

输入端口必须为线网数据类型,输入端口可以连接到线网或reg数据类型的变量。

输出端口可以是线网或reg数据类型;从模块外部看输出必须连接到线网数据类型的变量。

输入/输出端口,从模块内部来讲,输入/输出必须为线网数据类型;从模块外部来看也必须连接到线网类型的变量。

位宽匹配,Verilog允许端口的内外两个部分具有不同的位宽。

未连接端口,Verilog允许模块实例的端口保存未连接的状态。

非法端口,例如使用reg变量连接输入端口。

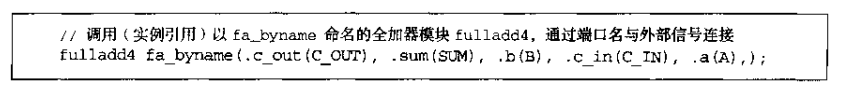

4.2.4 端口与外部信号的连接

顺序端口连接:安装端口顺序连接

命名端口连接:安装端口名字连接

只要端口名字不变,即使端口顺序改变也无需调整。

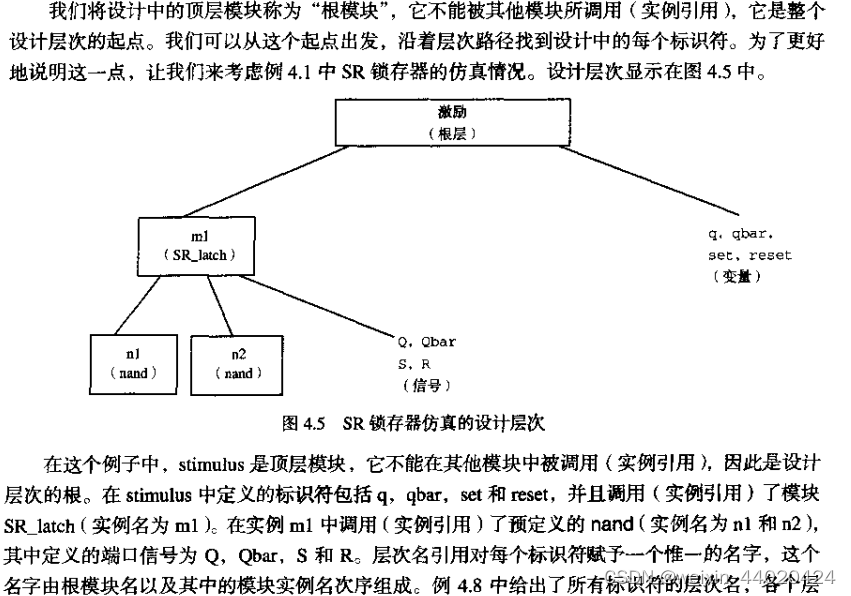

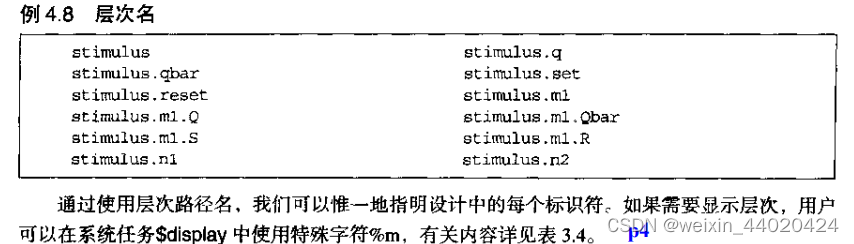

4.3层次命名

如果使用Verilog进行层次化设计。每一个模块实例、信号或变量都使用一个唯一的标识符进行定义;层次名使用“.”分割的标识符组成,每个标识符代表一个层次,这样设计者就可以在设计中的任何地方通过指定完整的层次名对每个标识符进行访问。

2691

2691

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?