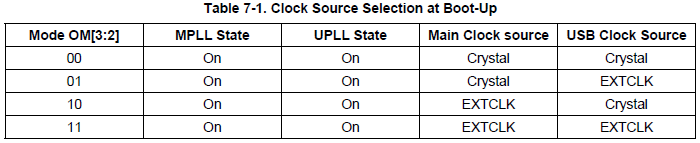

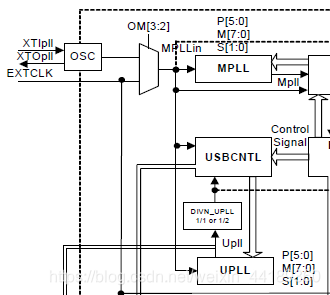

S3C2440的时钟控制逻辑既可以外接晶振,然后通过内部电路产生时钟源;也可以直接使用外部提供的时钟源,它们通过引脚(OM[3:2])的设置来选择。如下图:

时钟源选择在启动

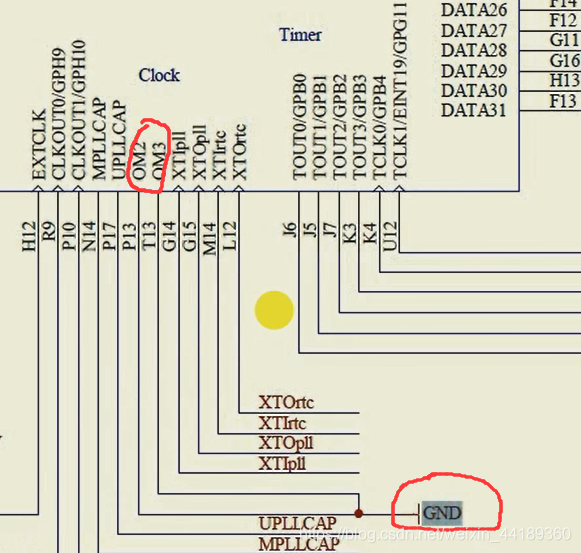

下左图中右上角的OSC为晶振,EXTCLK为外部时钟源。即通过引脚(OM[3:2])的设置来选择S3C2440的时钟控制逻辑。

由上面右边的原理图可知,OM2、OM3接GND置0。所以为表7-1中的第一种情况,MPLL和UPLL均设置为使用晶振。

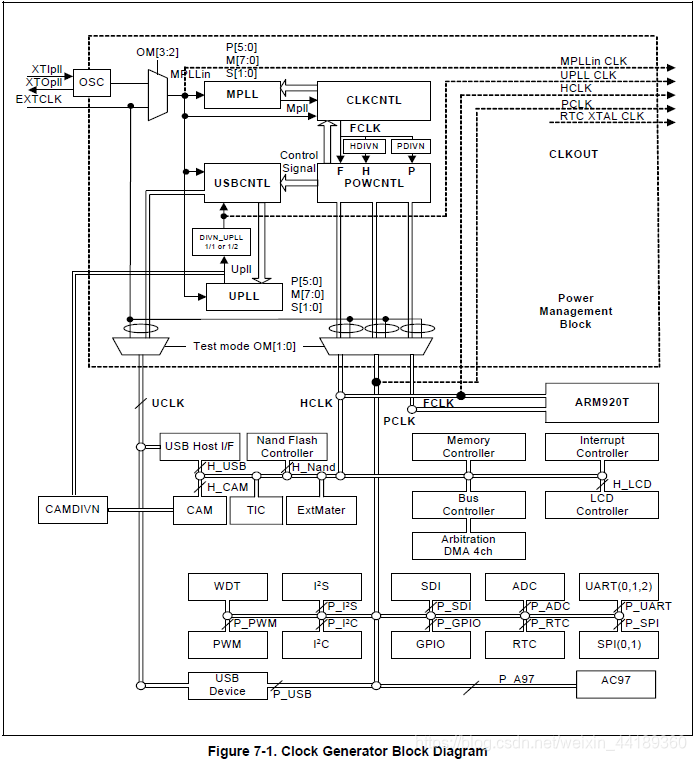

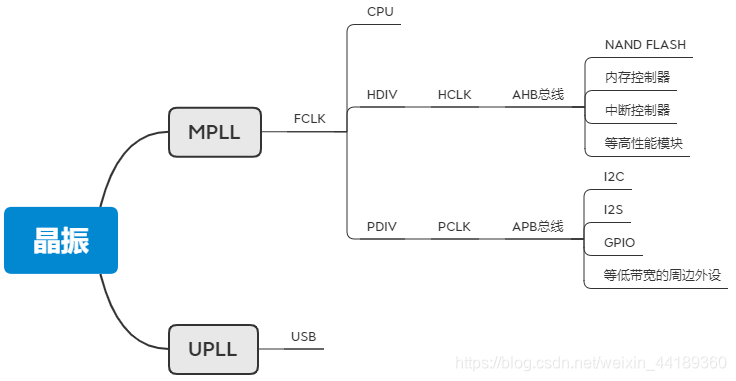

时钟发生器方框图

由上面的时钟发生器方框图可以总结出如下框图

所以时钟控制逻辑给整个芯片提供3种时钟:

- FCLK用丁CPU核;

- HCLK用于AHB总线上设各,比如CPU核、存储器控制器、中断控制器、LCD控制器、DMA和USB主机模块等:

- PCLK用于APB总线上的设备,比如WATCHDOG、IIS、I2C、PWM定时器、MMC接口、ADC、UART,GPIO、RTC和SPI。

AHB(AdvancedHighperformanceBus)总线主要用了高性能模块(如CPU、DMA和DSP等)之间的连接;

APB(AdvancedPeripheralBus)总线主要用于低带宽的周边外设之间的连接,例如UART、I2C等.

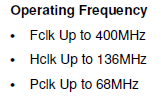

我使用的这块板子外界12MHz的晶振,通过硬件设备:PLL锁相环将时钟频率提高。

我使用的这块板子外界12MHz的晶振,通过硬件设备:PLL锁相环将时钟频率提高。

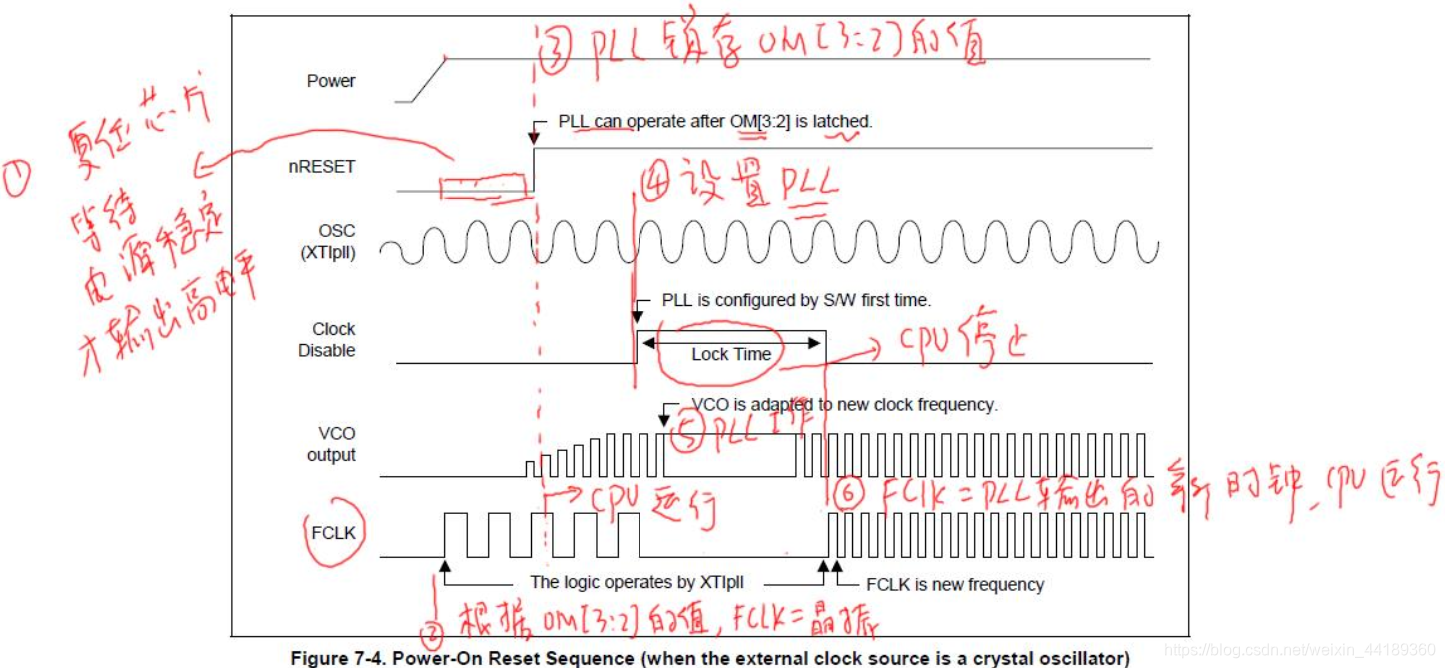

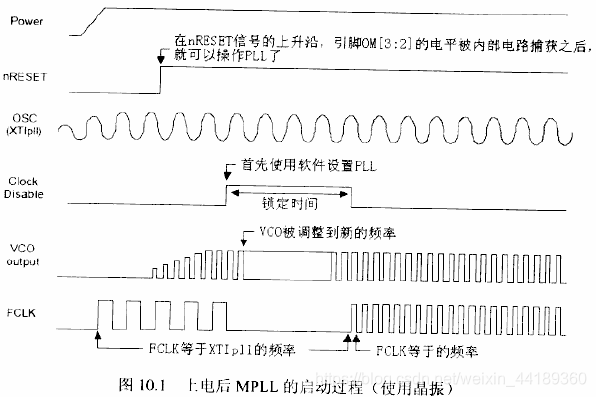

开机复位时序图:

S3C2440有两个PLL:MPLL和UPLL。UPLL专用于USB设备,MPLL用于设置FCLK、HCLK、PLCK。它们的设置办法相似,以MPLL为例;

上电时,PLL没被启动,FCLK即等于外部输入的时钟,称为Fin。若要提高系统时钟,需要软件来启用PLL,下面上面的图来介绍PLL的设置过程。

- 上电几毫秒后,晶振(图中的OSC)输出稳定,FCLK=Fin(品振频率),nRESET信号恢复高电平后,CPU开始执行指令。

- 可以在程序开头启动MPLL,设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(称为LockTime)内,FCLK停振,CPU停止工作。LockTime的长短由寄存器LOCKTIME设定。

- Lock Time之后,MPLL输出正常,CPU工作在的FCLK下。

FCLK、HCLK和PCLK的比例是可以改变的,设置它们三者的比例,启动MPLL只需要设置3个寄存器(对于S3C2440的一些时钟比例,还需要额外设置一个寄存器)。

如何写程序控制MPLL、HDIV、PDIV?

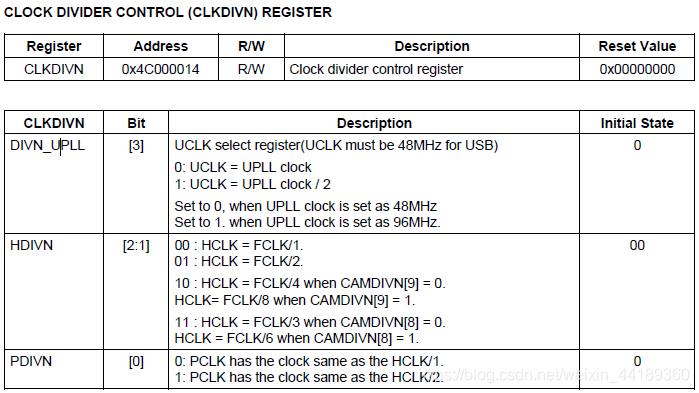

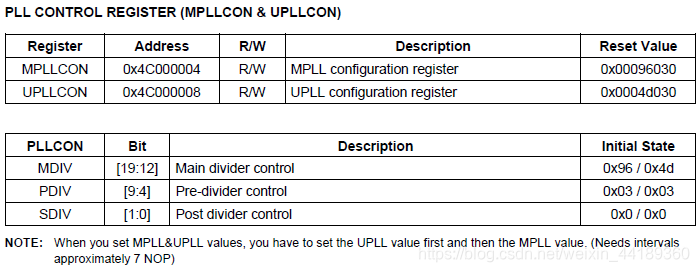

通过以下两个寄存器:

- 时钟分频控制(CLKDIVN)寄存器

- PLL控制寄存器(MPLLCON和UPLLCON)

详情参考:《S3C2440A_UserManual_Rev13》《嵌入式Linux应用完全开发手册》

339

339

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?