X86 CPU架构

内核版本

linux-6.1.5

boot

路径:linux-6.1.5/arch/x86/boot/

| . +--- .gitignore +--- a20.c +--- apm.c +--- bioscall.S +--- bitops.h +--- boot.h +--- cmdline.c +--- compressed | +--- .gitignore | +--- acpi.c | +--- cmdline.c | +--- cpuflags.c | +--- early_serial_console.c | +--- efi.c | +--- efi.h | +--- efi_thunk_64.S | +--- error.c | +--- error.h | +--- head_32.S | +--- head_64.S | +--- ident_map_64.c | +--- idt_64.c | +--- idt_handlers_64.S | +--- kaslr.c | +--- kernel_info.S | +--- Makefile | +--- mem_encrypt.S | +--- misc.c | +--- misc.h | +--- mkpiggy.c | +--- pgtable.h | +--- pgtable_64.c | +--- sev.c | +--- string.c | +--- tdcall.S | +--- tdx.c | +--- tdx.h | +--- vmlinux.lds.S +--- copy.S +--- cpu.c +--- cpucheck.c +--- cpuflags.c +--- cpuflags.h +--- ctype.h +--- early_serial_console.c +--- edd.c +--- genimage.sh +--- header.S +--- install.sh +--- io.h +--- main.c +--- Makefile +--- memory.c +--- mkcpustr.c +--- msr.h +--- mtools.conf.in +--- pm.c +--- pmjump.S +--- printf.c +--- regs.c +--- setup.ld +--- string.c +--- string.h +--- tools | +--- .gitignore | +--- build.c +--- tty.c +--- version.c +--- vesa.h +--- video-bios.c +--- video-mode.c +--- video-vesa.c +--- video-vga.c +--- video.c +--- video.h |

A20

A20使能(包括等待上线)和测试相关代码。

A20 gate是用于处理Intel 80286和更高版本CPU的内存管理的一个功能。在8086处理器中,由于地址总线只有20根线,所以最大可寻址的内存空间为1MB。但是,在80286和更高版本CPU中,地址总线具有32根线,可以寻址4GB的内存空间。A20 gate的主要作用是在实模式下通过开启或关闭A20地址线的访问,以便支持对超过1MB的内存进行访问。

在X86架构中,A20 gate是通过向8042键盘控制器发送命令来控制的。开启A20 gate时,允许CPU访问超过1MB的内存空间;关闭时,限制CPU仅能访问1MB内存。这种控制方式通常用于兼容早期的软件和硬件设计,并在一些特定的应用中发挥作用。

KBC

KBC通常指的是"Keyboard Controller",即键盘控制器。在计算机系统中,键盘控制器是一种用于管理和控制键盘输入的硬件设备或芯片。键盘控制器通常负责接收键盘输入信号、将其转换为计算机可识别的数据格式,并将数据发送到计算机的中央处理器(CPU)或其他相关硬件。键盘控制器还可能负责处理特殊按键,如功能键、组合键等。

在早期PC系统中,键盘控制器通常是通过PS/2或其他接口与主板连接的。它在计算机启动时负责初始化键盘并在操作系统运行时响应键盘输入。随着技术的发展,一些现代计算机系统可能使用集成在主板芯片组中的键盘控制器或者采用更先进的接口标准。

APM

读取APM BIOS信息。

APM BIOS (Advanced Power Management BIOS) 是计算机系统中用于管理电源和能源的一种标准。它提供了一系列的功能和接口,用于控制电源的管理、节能功能以及相关的系统行为。APM BIOS通常是嵌入在计算机的基本输入/输出系统(BIOS)中,用于与操作系统和硬件进行交互,以实现对电源管理的控制。

通过APM BIOS,操作系统可以向计算机硬件发送命令,实现诸如睡眠模式、待机模式、自动关闭等节能功能。同时,APM BIOS还可以向操作系统报告有关电源状态、电池信息和节能策略的数据。这使得计算机系统可以更加智能地管理电源,从而延长电池寿命,降低能源消耗,并改善能源利用效率。

需要注意的是,随着技术的发展,一些新的系统可能已经采用了更为先进的能源管理标准,如ACPI(Advanced Configuration and Power Interface),来取代APM BIOS。不过,对于一些旧版操作系统或兼容性需求,APM BIOS仍然可能会发挥作用。

bioscall

汇编封装intcall,用于读取BIOS信息。

bitops

指定地址进行位域写操作。

real-mode

X86 real mode是指Intel x86处理器的一种工作模式,它是处理器最早期的工作模式之一。在real mode下,处理器以8086兼容的方式工作,可以访问1MB的内存空间,并且使用16位的寄存器和地址总线。

在real mode下,处理器不具备保护内存的能力,意味着任何程序都可以访问内存中的任何位置,这可能会导致内存冲突和安全性问题。此外,实模式下无法直接访问大于64KB的内存,需要通过段寄存器进行分段访问。

虽然real mode已经过时并且在现代操作系统中很少被使用,但它对于理解计算机启动过程、底层编程和操作系统设计仍然非常重要。在引导加载程序(bootloader)和一些嵌入式系统中,仍会用到real mode。

在X86 real mode下,处理器以8086兼容的方式工作,可以访问1MB的内存空间。这1MB内存被划分成20位地址空间(2的20次方等于1MB),寻址范围从0x00000到0xFFFFF。

在实模式下,程序可以使用段寄存器和偏移地址来访问内存中的任何位置。段寄存器和偏移地址会合并成一个物理地址,然后用于访问内存。实模式通过将16位的段寄存器值左移4位,再加上16位的偏移地址,来计算出物理内存地址。

需要注意的是,尽管实模式下可以访问1MB的内存空间,但由于地址总线只有20根线,因此无法直接访问超过1MB的内存。若要访问更多内存,则需要使用一些特殊的技术,比如分页机制或者转换到保护模式下才能实现。

虽然1MB的内存对于当今计算机系统来说已经远远不够,但了解实模式下对内存的访问仍然有助于我们理解计算机系统的底层工作原理和历史发展。

real mode下处理器使用物理地址而不是虚拟地址。在real mode中,程序可以直接访问物理内存的地址,而不需要通过虚拟地址或分页机制进行转换。

在 real mode 下,处理器使用 20 位地址总线来访问物理内存。这意味着处理器可以直接寻址的物理地址范围是从 0x00000 到 0xFFFFF,共计 1MB 的物理内存空间。这些 20 位地址能够覆盖整个可用的物理内存地址空间,因此 real mode 下程序的直接物理内存访问范围限制在这个 1MB 内。

cmdline

cmdline.c 包括用于解析和处理引导加载程序(bootloader)传递给内核的命令行参数的代码,主要是参数长度和参数位置解析。

解析和处理引导加载程序(bootloader)传递给内核的命令行参数,指grub中配置kernel启动参数,可以通过/proc/cmdline读取到的参数。

cpu/cpucheck/cpuflags

CPU名称、标志、厂商信息识别。

X86体系厂商有AMD、intel、hygon(海光)、centaur(半人马/威盛x86)、transmeta(全美达)。AMD和intel是双雄,还有一些夹缝求存的公司。

early_serial_console

简单的串口设备ttyS0初始化。

edd

获取磁盘信息,包括读取mbr。

EDD(Enhanced Disk Drive Services)是BIOS(基本输入/输出系统)的一组扩展,用于支持超出原始INT 13h BIOS功能限制的磁盘访问。EDD旨在解决随着存储技术的发展而产生的更高级磁盘访问需求。

EDD的一些关键特性包括支持更大的磁盘容量、增强的错误处理和改进的数据传输模式。这些特性使操作系统和软件应用能够充分利用现代硬件提供的更先进的磁盘功能。

总体而言,EDD在实现有效的磁盘访问方面发挥着重要作用,尤其是在传统BIOS功能不足的环境中。然而,随着技术的不断进步,需要注意的是在现代计算系统中,可能会有更新的标准和接口已经取代了EDD。

header

X86 实模式64K段地址操作,实模式0-1M范围,如果要在X86上写一个裸机程序,这段代码想必要研究一下。

BIG FAT NOTE: 我们正在使用64k段的实模式。 因此,必须将段地址乘以16以获得它们各自的线性地址。 为了避免混淆,线性地址使用前导十六进制表示,而段地址则写成段:偏移。

X86架构的CPU在启动时会将IP(指令指针)寄存器中的初始地址设置为0xFFFFFFF0,这是因为在实模式下,CS:IP被设置为0xFFFF:0xFFF0,即物理地址0xFFFF0,这是BIOS固件存储的起始位置。

install

"make install" script for i386 architecture

main

实模式主入口,覆盖键盘初始化,BIOS模式设置,堆初始化,boot代码将被编译为一个独立程序。

构建目标:vmlinux.bin setup.bin setup.elf bzImage fdimage fdimage144 fdimage288 image.iso hdimage

memory

内存e820、e801、88,是X86内存与CPU的标准连接通道。在这段代码中检出内存。

| void detect_memory(void) { detect_memory_e820(); detect_memory_e801(); detect_memory_88(); } |

内存e820

E820是一种用于在x86架构计算机中报告系统内存布局信息的标准方法。它通过BIOS提供了关于物理内存地址范围、内存类型(比如RAM、ROM、ACPI等)、保留区域和设备映射等方面的信息。操作系统可以使用这些信息来有效管理系统内存,避免冲突和重叠,确保各个程序和设备能够正确地访问内存资源。

内存e801

E801是一个ACPI(高级配置与电源管理接口)命令,用于获取系统的内存地图信息。这个命令返回了有关可访问的物理内存范围和其他相关信息,使操作系统能够更好地了解系统的内存布局和可用内存资源。

内存88

在实模式下,0x88是一个中断向量,用于获取扩展内存信息。当调用这个中断时,系统会返回有关扩展内存的信息,包括大小和位置等。这对于早期的操作系统和软件来说非常重要,因为它们需要了解系统中可用的所有内存资源以便正确地进行内存管理和分配。

pm

Prepare the machine for transition to protected mode.

为机器转换到保护模式做好准备。

从实模式切换到保护模式。

x86保护模式是x86架构处理器的一种工作模式,用于提供更高级的内存管理和操作系统支持。以下是保护模式的一些关键特点:

- **内存保护**:在保护模式下,x86处理器可以通过使用段描述符和页表来实现内存保护,这样不同的程序和操作系统可以被隔离开来,防止彼此之间相互干扰或者越界访问内存。

- **多任务支持**:保护模式允许操作系统同时运行多个程序,并为每个程序分配独立的内存空间和系统资源。这使得操作系统能够更好地管理多个任务之间的切换和资源共享。

- **特权级别**:保护模式引入了四个特权级别(0到3),通常称为Ring 0到Ring 3。Ring 0是最高特权级别,用于操作系统内核,而Ring 3是用户态应用程序所在的最低特权级别。

- **硬件支持**:保护模式提供了一系列新的指令集和机制,包括对虚拟内存、分页机制、特权级别转换等方面的硬件支持。

printf

基于内核C库,封装的printf接口,用于调试。

printk经常解析格式有限。

setup.ld

链接脚本,控制i386镜像段。

string

基础字符串功能。

符号:puts

tty

串口基本输出功能,通过BIOS或串口。

version

内核版本号。

符号:kernel_version

VESA

VESA(Video Electronics Standards Association)是一个制定计算机图形标准的组织。x86 VESA通常指的是在x86架构的计算机上使用的VESA标准,用于控制显示器的视频模式和图形输出。它提供了一种统一的方式来访问各种图形模式,包括高分辨率和真彩色模式,以及直接内存访问(DMA)功能。通过使用VESA BIOS Extensions(VBE),开发人员可以编写与硬件无关的图形应用程序,而不用考虑特定图形适配器的细节。这使得图形应用程序更具可移植性和兼容性。

VGA

VGA是Video Graphics Array的缩写,是一种显示标准,最初由IBM于1987年推出。它最初以640x480像素分辨率和16色的调色板为特征,后来发展出了支持更高分辨率和更多颜色的版本。VGA使用模拟信号传输图像数据,因此受到分辨率、刷新率和线数的限制。

VGA接口通常通过15针的D-sub连接器与计算机主机连接,虽然现代设备已经普遍采用了数字接口(如HDMI和DisplayPort),但VGA仍然被广泛应用于老式计算机、监视器和投影仪等设备上。

尽管VGA已逐渐被更先进的数字接口所取代,但它作为计算机图形输出的标准在相当长的时间内仍然具有重要意义。

video

VGA和VESA显示基础驱动,以及基础功能使用。

VGA是一种显示标准,最初由IBM推出,用于控制显示器的视频模式和图形输出。它使用模拟信号传输图像数据,具有特定的分辨率、色彩深度和刷新率限制。

VESA是一个制定计算机图形标准的组织,提供了一种统一的方式来访问各种图形模式,包括高分辨率和真彩色模式,以及直接内存访问(DMA)功能。VESA通过制定标准来使得图形应用程序更具可移植性和兼容性。

compressed

`arch/x86/boot/compressed/`目录下存放的是用于引导Linux内核的压缩代码。这些代码在启动过程中被用来解压缩并加载Linux内核,以便系统可以启动。

Linux压缩内核是启动时由内核自解压,怎么能做到自解压。一,启动时先加载外部工具,二,镜像引导部分数据不压缩。

acpi

ACPI操作,可以获取到ACPI的地址。

ACPI(Advanced Configuration and Power Interface)是一种标准,旨在提供操作系统与计算机硬件之间的统一接口,以管理系统配置信息、电源管理和热管理。ACPI旨在取代早期的BIOS能量管理和休眠模式,为现代计算机系统带来更强大和灵活的能量管理功能。

ACPI标准定义了一组数据结构、方法和命名空间,用于描述和控制系统资源、能量状态和事件。这些信息可被操作系统用来动态地配置硬件、实现系统休眠/唤醒功能、管理电源和热管理等。

通过ACPI,操作系统可以与计算机硬件进行全面的交互,包括对CPU、内存、外围设备和总线的控制,以及对系统能源的管理。因此,ACPI在实际应用中发挥着重要作用,尤其是在笔记本电脑和服务器等需要积极进行电源管理的场景下。

efi

获取efi参数、配置。

EFI(Extensible Firmware Interface)是一种基于标准化的固件接口,用于操作系统和计算机硬件之间的交互。它代替了传统的BIOS(Basic Input/Output System),提供了更现代化、灵活和可扩展的固件解决方案。

EFI引入了一种新的启动机制,称为UEFI(Unified Extensible Firmware Interface)。与传统的BIOS相比,UEFI提供了更多功能和优势,包括:

1. 支持更大的硬盘驱动器和分区容量。

2. 提供了图形用户界面,使得固件设置和诊断更加直观和易用。

3. 支持网络协议栈,可以在网络上启动操作系统安装或维护工具。

4. 允许操作系统和应用程序通过UEFI接口与固件进行交互。

总体来说,EFI/UEFI作为一种现代化的固件接口,为计算机系统提供了更强大、更灵活和更可扩展的启动和管理功能。它已经成为了当前PC和服务器设备上常见的固件标准。

idt

grub引导stage1、stage2阶段中断配置。

mem_encrypt

AMD内存加密功能,海光也有。

总结

X86在boot阶段,加载的设备:CPU、内存、串口、显示器(显卡和显示接口)。

封装功能:提供打印接口printf/puts,内存拷贝,字符串接口等。

编译输出:vmlinux.bin、bzImage等。

coco tdx

"CoCo TDX" 是英特尔推出的一项技术,它是一个新型的硬件安全技术,用于提高系统的可信度和安全性。

具体来说,CoCo TDX(Control-Flow Enforcement Technology for Secure Translated Dynamic Execution)是一种基于硬件的安全特性,旨在防止恶意软件或攻击者利用代码执行的漏洞来进行攻击。它通过对动态执行的控制流进行保护,确保程序只能按照预期的正确路径进行执行,从而防止恶意修改或劫持程序的控制流。

CoCo TDX结合了虚拟化和硬件保护技术,可以提供更高级别的系统隔离和安全性。它利用硬件支持来监视和验证指令的执行,并在发现异常时采取相应的安全保护措施,例如中断执行或终止恶意代码的执行。

这项技术对于云计算、边缘计算和虚拟化等场景非常有用,可以提供更强大的安全保护,防止恶意软件跨越虚拟机或容器边界,进一步提高系统的可信度和安全性。

crypto

X86 加密技术。

aegis128

Aegis128 是一种基于 x86 架构的加密算法。

Aegis128 是一个认证加密算法,采用 128 位密码长度。它结合了 AEAD(Authenticated Encryption with Associated Data)和 SIV(Synthetic Initialization Vector)模式,提供了数据的机密性、完整性和认证性。

在 x86 架构中,可以使用硬件指令集扩展来优化 Aegis128 算法的执行效率。例如,Intel 的 AES-NI 指令集可以加速算法中的 AES 加密操作,提高整体性能。

Aegis128 算法通常用于保护数据传输过程中的安全性,包括网络通信、存储介质加密等场景。它可以对数据进行加密,并生成认证标签以验证数据的完整性和真实性。

需要注意的是,Aegis128 只是一种特定的加密算法名称,在实际应用中可能还需要考虑密钥管理、随机数生成、安全协议等其他方面的内容来确保系统的整体安全性。

总之,x86 Crypto 中的 Aegis128 是一种基于 x86 架构的加密算法,通过硬件支持和相关指令集扩展,提供数据的加密、认证和完整性保护。

aes

AES (Advanced Encryption Standard): 这是一种对称加密算法,也被称为 Rijndael。它使用 128、192 或 256 位密钥来加密和解密数据,广泛用于保护敏感信息的机密性。

aria

ARIA: ARIA 是韩国政府采用的一种对称加密算法,具有高度的安全性和性能。它支持 128、192 和 256 位密钥,并且适用于各种加密应用。

blake2s

Blake2s: Blake2s 是一种快速的哈希函数,用于计算数据的摘要或校验和。它提供了高度的安全性和强大的抗碰撞能力,适用于数据完整性验证等场景。

blowfish

Blowfish: Blowfish 是一种对称加密算法,可用于加密和解密数据。它支持可变长度的密钥,适用于各种加密需求。

camellia

Camellia: Camellia 是一种对称加密算法,由日本提出并与欧洲共同开发。它支持 128、192 和 256 位密钥长度,为数据提供机密性和完整性保护。

cast5

CAST5: CAST5 是一种对称加密算法,也称为 CAST-128。它使用变长密钥并支持数据的加密和解密操作。

chacha

ChaCha: ChaCha 是一种流密码算法,用于生成伪随机数据流。它具有较高的速度和安全性,适用于数据加密和身份验证等领域。

crc32

CRC32: CRC32 是一种循环冗余校验算法,用于检测数据在传输过程中是否发生错误或被篡改。

des3

DES3 (Triple DES): 三重 DES 是一种对称加密算法,通过多次应用 DES 算法来提高安全性。

ghash

GHASH: GHASH 是一种消息认证码算法,常用于 AES-GCM 模式中,用于计算加密数据的完整性校验值。

polyyal

Poly1305: Poly1305 是一种快速且安全的消息认证码算法,常与其他加密算法结合使用。

sha1/sha256

SHA1, SHA256: 这些是哈希函数,用于计算数据的摘要或校验和。SHA1 提供 160 位的哈希值, 而 SHA256 提供 256 位的哈希值。

sm3/sm4

SM3, SM4: 这是由中国国家密码管理局发布的密码算法标准。SM3 是哈希算法,SM4 是对称加密算法。

twofish

Twofish: Twofish 是一种对称加密算法,它支持多种密钥长度,并提供高度的安全性。

entry

X86程序入口。

syscall

"syscall": 这指的是在 x86 架构下进行系统调用的入口点。当应用程序触发系统调用时,处理器会切换到特权级别较高的模式(如内核模式),然后转到相应的系统调用处理例程。具体的系统调用处理流程和实现方式因操作系统而异。

vdso

"vdso" (Virtual Dynamic Shared Object): 在 Linux 系统中,vdso 是一种特殊的共享库,它位于用户空间,提供了一些常见的系统调用函数的实现。这些实现通过修改处理器上的时间戳计数器(TSC)或利用其他硬件特性来加速系统调用的执行。vdso 的使用可以减少用户态到内核态切换的开销,提高系统调用的性能。

vsyscall

"vsyscall" (Virtual System Call): vsyscall 是一个特殊的内核映射区域,用于存放一些常见的系统调用函数的实现。在早期的 Linux 内核版本中,vsyscall 提供了对 gettimeofday()、time() 等系统调用的快速访问。但随着技术的发展,vsyscall 已经逐渐被 vdso 取代。

APIC(Advanced Programmable Interrupt Controller)

APIC(高级可编程中断控制器):

APIC 是一种硬件设备,用于管理和分发中断信号。在多处理器系统中,每个处理器都有自己的本地 APIC,同时还存在一个 I/O APIC 用于处理外部设备的中断。APIC 可以根据优先级和调度算法来分配和传递中断请求,确保它们被正确地处理。

ACPI(Advanced Configuration and Power Interface)

ACPI(高级配置和电源接口):

ACPI 是一种开放标准,旨在提供操作系统与计算机硬件之间的统一接口,以实现系统配置、电源管理和设备功耗控制等功能。ACPI 通过定义数据结构和方法,允许操作系统获取有关硬件配置信息、设备状态和电源管理策略等方面的信息。

ACPI 提供了众多的功能,包括:

- 系统配置描述表(System Description Tables):提供了关于计算机硬件配置的详细信息。

- 电源管理:定义了电源管理策略,使操作系统能够控制设备的功耗和休眠状态。

- 设备的热插拔支持:允许在计算机运行时添加或移除设备。

- 高级电源管理(APM)的扩展:提供了更高级的电源管理功能。

ACPI 是由多个硬件制造商和操作系统开发者共同制定的标准,它使得操作系统能够更好地利用计算机硬件资源,并实现更高效的系统配置和电源管理。

kprobes

kprobes 是 Linux 内核中的一个功能,它允许开发者在内核代码中插入动态的断点,以便在运行时监视和调试内核函数的执行。以下是对 kprobes 的简要介绍:

1. 动态断点插入:

kprobes 允许开发者在内核函数的任意位置插入断点(也称为探测点),而不需要修改源代码或重新编译内核。这使得开发者能够在运行时检查特定函数的参数、变量值和执行路径,从而进行调试、性能分析或其他形式的监视。

2. 监视和调试功能:

使用 kprobes,开发者可以监视内核函数的执行情况,包括进入函数、离开函数和在函数内部的特定位置。通过在这些位置设置断点,可以捕获函数的执行时机,并观察寄存器状态、变量值以及其他与函数执行相关的信息。

3. 非侵入性:

kprobes 在设计上是非侵入性的,即不会对内核本身的行为产生显著影响。它通过合理利用 CPU 的调试功能,实现了在内核执行期间的动态调试和监视。因此,使用 kprobes 进行调试不会对系统的稳定性和性能产生重大影响。

4. 灵活性和扩展性:

kprobes 提供了丰富的 API 和工具,使开发者能够利用这一机制进行更复杂的调试和监视操作。它支持条件断点、动态追踪、事件触发等功能,并可以与其他内核功能(如 tracepoints、perf)结合使用,从而实现更全面的内核分析和优化。

需要注意的是,kprobes 是一个高级的内核功能,对于普通用户和应用程序开发者来说,可能并不直接使用。它主要为内核开发人员、系统管理员和性能分析师提供了一种强大的工具,用于理解和优化 Linux 内核的行为。

总结:kprobes 是 Linux 内核中的一个功能,它允许在运行时插入动态断点,以便监视和调试内核函数的执行。通过 kprobes,开发者可以非侵入性地观察和分析内核的行为,从而更好地理解和优化系统。

示例

要添加断点、监视和调试,在使用 kprobes 进行内核调试时,可以按照以下步骤进行操作:

1. 导入必要的头文件:

| #include <linux/kprobes.h> |

2. 定义 kprobe 结构体:

| static struct kprobe my_kprobe = { .symbol_name = "function_to_probe", }; |

其中,"function_to_probe" 是要插入断点的目标函数名。

3. 定义 pre_handler 函数:

| static int pre_handler(struct kprobe *p, struct pt_regs *regs) { // 在这里执行预处理逻辑,如打印寄存器状态、变量值等信息 return 0; } |

pre_handler 函数将在目标函数被调用之前执行。

4. 定义 post_handler 函数:

| static void post_handler(struct kprobe *p, struct pt_regs *regs, unsigned long flags) { // 在这里执行后处理逻辑,如打印返回值、修改寄存器值等操作 } |

post_handler 函数将在目标函数返回后执行。

5. 注册 kprobe:

| static int __init my_init(void) { int ret; my_kprobe.pre_handler = pre_handler; my_kprobe.post_handler = post_handler; ret = register_kprobe(&my_kprobe); if (ret < 0) { pr_err("Failed to register kprobe: %d\n", ret); return ret; } pr_info("Kprobe registered successfully!\n"); return 0; } |

在模块初始化函数中注册 kprobe。

6. 反注册 kprobe:

| static void __exit my_exit(void) { unregister_kprobe(&my_kprobe); pr_info("Kprobe unregistered\n"); } |

在模块退出函数中反注册 kprobe。

这是一个基本的示例,用于在目标函数执行前后插入断点、监视和调试。你可以根据实际需求,在 `pre_handler` 和 `post_handler` 函数中添加更具体的调试逻辑。同时,还可以使用 printk 或其他调试工具来输出相关信息。

X86 南北桥

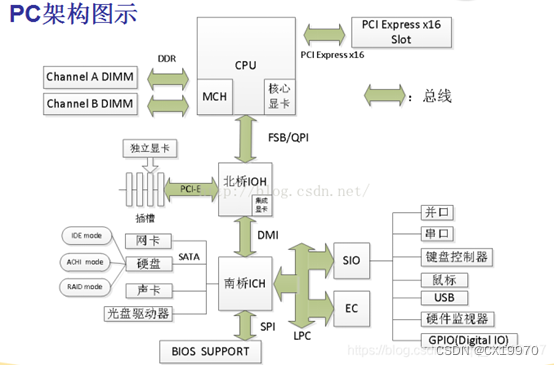

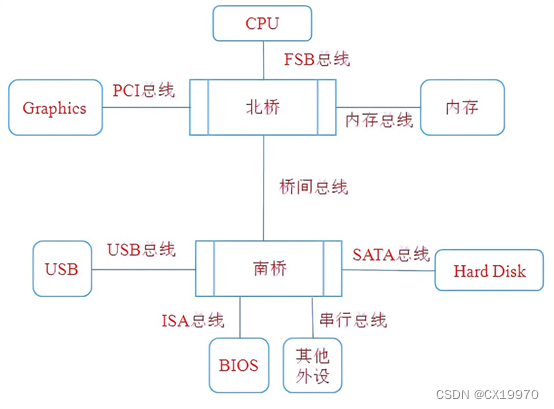

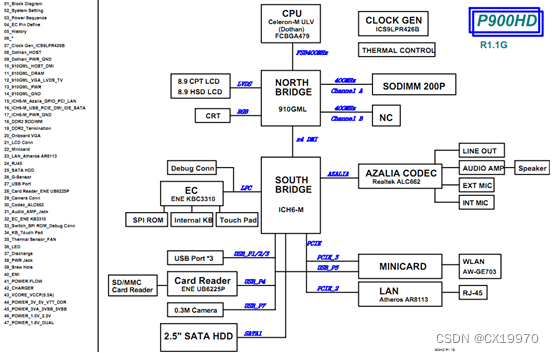

南北桥结构

x86是一种处理器架构,广泛应用于个人电脑和服务器领域。它最初由英特尔公司开发,并成为PC市场的主导架构。

南北桥是指位于主板上的两个芯片组:南桥和北桥。它们分别负责处理不同的任务。

- 北桥(Northbridge)被称为系统控制器或内存控制器,它连接着中央处理器(CPU)、系统内存、高速图形接口(例如PCI Express)以及其他重要组件。北桥还负责管理数据传输和协调各个组件之间的通信。

- 南桥(Southbridge)则负责处理次要外设的控制和管理,例如硬盘驱动器、USB接口、音频接口、网卡、串行端口等。南桥通常比北桥功能更多,但速度较慢。

在网上找到另一张南北桥架构图,注意到其中细节有所不同,如:PCI设备。事实上南北桥在现代intel技术中已经失势,USB、SATA、显卡是集成在PCI总线,南桥已经是发展很久的技术了。

随着时间的推移,x86架构以及南北桥技术都经历了多个迭代和演进。下面是一些常见的x86南北桥技术迭代:

1. 初期的x86架构:最初的x86处理器和南北桥芯片组设计相对简单,南桥负责管理外围设备,而北桥则处理系统总线和内存控制。

2. Intel 800系列芯片组:这些芯片组引入了双通道内存控制器和高速前端总线(FSB),提供更快的数据传输速度和更好的性能。

3. Intel 900系列芯片组:这一代芯片组引入了PCI Express接口,并支持新一代处理器架构,如Core 2 Duo和Core 2 Quad。

4. Intel 4/5/6/7系列芯片组:这些芯片组在性能和功能上进行了改进,引入了更高带宽的内存控制器、增强的图形性能以及更多的外围接口。

5. Intel 8/9系列芯片组:这些芯片组继续提升性能和功能,支持USB 3.0、SATA 6Gbps等新技术,并引入了更高级的图形接口,如DisplayPort和HDMI。

需要注意的是,随着技术的进步,传统的南北桥架构已经逐渐被集成到处理器中,例如Intel的Sandy Bridge、Ivy Bridge和后续的处理器都将内存控制器和图形核心集成在CPU芯片上,减少了对外部芯片组的依赖。因此,在现代主板设计中,南北桥的角色已经不再像过去那样突出。

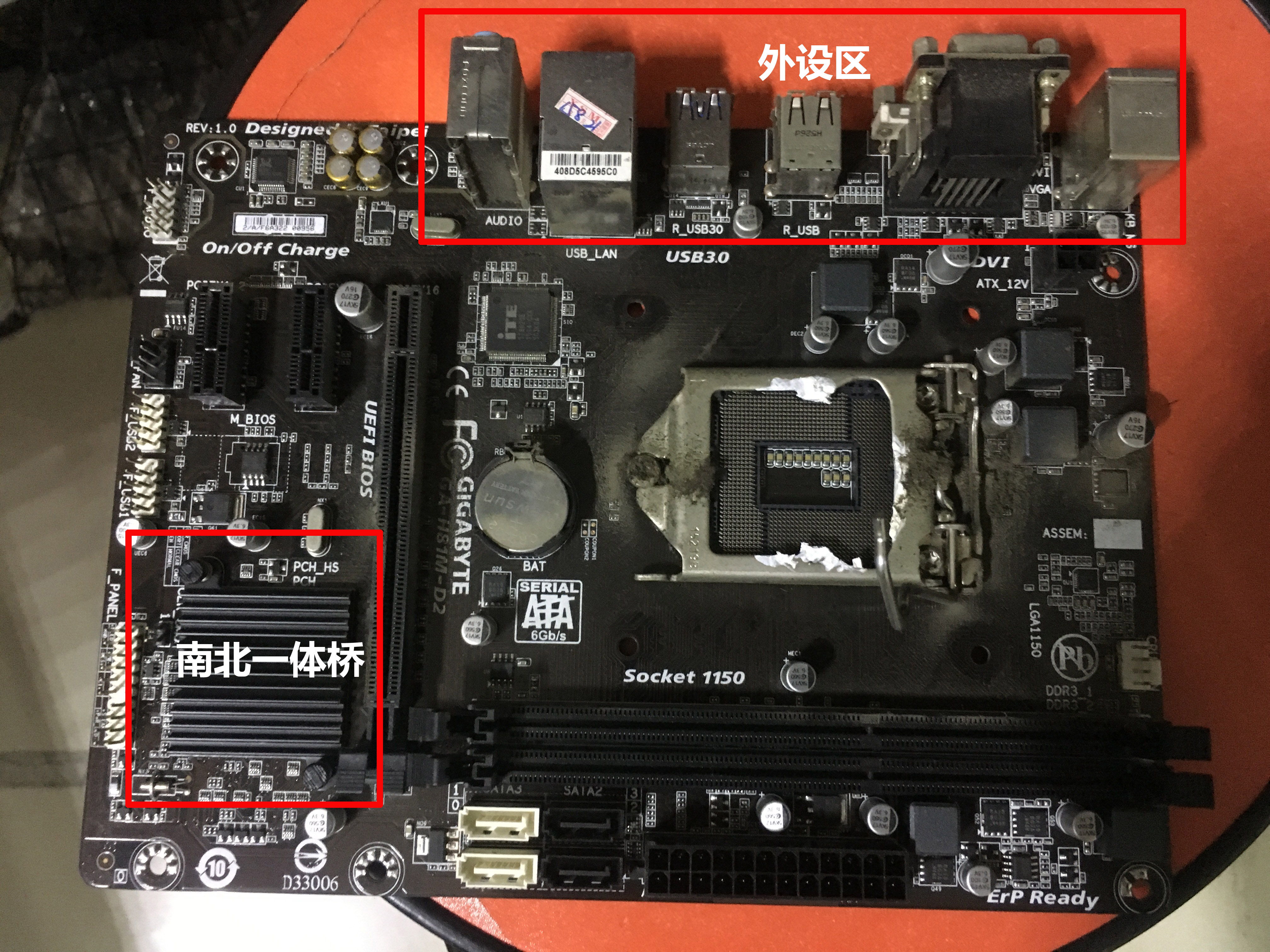

实物

旧技术:南北桥分离。

新技术:南北桥合并。

值得注意的是南北桥不在CPU内部。CPU通过FSB/QPI总线与南北桥通信。

总结

南北桥是X86世界观一项发展很长久的技术,在现代设备上可见性比较少,已经逐渐被新技术取代,在一些老机器上能看到。

需要知道的是北桥负责高速设备,南桥负责低速设备。

架构演进

以下是Intel x86 CPU架构的主要演进,按时间顺序列出了一些关键的架构名称、特性和覆盖时间范围:

1. 8086/8088(上市时间:1978年):

- 特点:基于16位架构,运行速度较慢。

- 经典产品:Intel 8086和8088。

2. 80286(上市时间:1982年):

- 特点:引入了保护模式、虚拟内存和内核模式等新功能。

- 经典产品:Intel 80286。

3. 80386(上市时间:1985年):

- 特点:首次引入32位处理能力,增强了处理器性能。

- 经典产品:Intel 80386。

4. 80486(上市时间:1989年):

- 特点:引入了高速缓存和浮点数处理单元(FPU),进一步提升了性能。

- 经典产品:Intel 80486。

5. Pentium系列(上市时间:1993年至今):

- 特点:引入了超标量架构、多级缓存、MMX指令集和动态执行技术等。

- 经典产品:Intel Pentium、Pentium Pro、Pentium II、Pentium III、Pentium 4。

6. Core系列(上市时间:2006年至今):

- 特点:基于NetBurst架构的Pentium 4之后,Intel推出了全新的Core架构,提供更高性能和能效比。

- 经典产品:Intel Core 2 Duo、Core i3、Core i5、Core i7。

7. Nehalem系列(上市时间:2008年至2010年):

- 特点:引入了集成内存控制器、快速路径互连和超线程技术等。

- 经典产品:Intel Core i7-900系列。

8. Sandy Bridge系列(上市时间:2011年至2012年):

- 特点:进一步提升了性能,并引入了英特尔高级矢量扩展(AVX)指令集。

- 经典产品:Intel Core i3/i5/i7第二代。

9. Ivy Bridge系列(上市时间:2012年至2013年):

- 特点:沿用Sandy Bridge架构,并进行了微小改进以提高能效和图形性能。

- 经典产品:Intel Core i3/i5/i7第三代。

10. Haswell系列(上市时间:2013年至2014年):

- 特点:引入了高级电源管理和具有集成显卡的Haswell架构。

- 经典产品:Intel Core i3/i5/i7第四代。

11. Broadwell系列(上市时间:2014年至2015年):

- 特点:采用14纳米制程工艺,提供更高的能效和图形性能。

- 经典产品:Intel Core i3/i5/i7第五代。

12. Skylake系列(上市时间:2015年至2018年):

- 特点:引入了6代英特尔处理器架构,提供更高的性能和能效。

- 经典产品:Intel Core i3/i5/i7第六代。

13. Kaby Lake系列(上市时间:2016年至2017年):

- 特点:微小改进的Skylake架构,并加强了视频播放和电源管理功能。

- 经典产品:Intel Core i3/i5/i7第七代。

14. Coffee Lake系列(上市时间:2017年至2018年):

- 特点:对Kaby Lake进行了修正和升级,提供更多的核心数量和更高的时钟速度。

- 经典产品:Intel Core i3/i5/i7第八代。

15. Coffee Lake Refresh(上市时间:2018年):

- 特点:第9代Coffee Lake Refresh架构是对第8代Coffee Lake架构的升级和改进。

- 经典产品:Intel Core i3/i5/i7第九代。

16. Coffee Lake Refresh Refresh(上市时间:2019年):

- 特点:第9代Coffee Lake Refresh Refresh是对第9代Coffee Lake Refresh架构的微小改进和修正。

- 经典产品:Intel Core i3/i5/i7第九代。

17. Comet Lake系列(上市时间:2019年至今):

- 特点:进一步提升了性能,增加了更多的核心数量和更高的时钟速度。

- 经典产品:Intel Core i3/i5/i7第十代。

18. Tiger Lake系列(上市时间:2020年至今):

- 特点:采用10纳米制程工艺,提供更高的性能和能效,并引入了Xe图形架构。

- 经典产品:Intel Core i3/i5/i7第十一代。

19. Alder Lake系列(预计上市时间:2021年):

- 特点:将首次采用混合架构,结合高性能核心和高效能核心,以优化性能和功耗之间的平衡。

这只是一些关键的Intel x86 CPU架构演进,涵盖了一个较长的时间范围。每个架构都带来了新的特性、改进的性能和能效,以满足不断增长的计算需求和技术发展的要求。

架构特性

8086到80486构成经典的8086系列,影响大且远。此后从Pentium到Skylake一直在稳步前行,功能迭代有层次感,相应的产品延续到Intel Core 6th。在此之后连续推出4代架构Kaby Lake、Coffee Lake、Coffee Lake Refresh、Comet Lake,基本在吃Skylake的老本,技术迭代上没有太大层次跃迁,相应的产品从Intel Core 7th延续到Intel Core 10th。Tiger Lake架构再次带来活力。

Intel Core 7th到Intel Core 10th,注意避开。

芯片架构

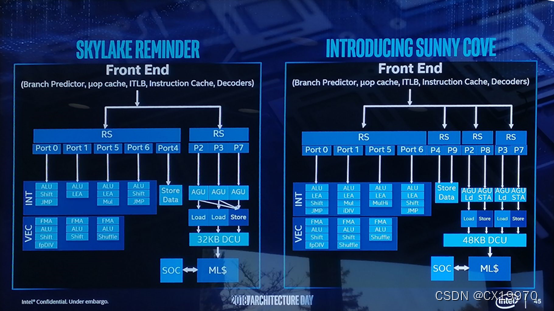

Skylake VS Sunny Cove

Sunny Cove是英特尔(Intel)架构家族中的一种微架构,它被用于第10代Intel Core处理器,代号为Ice Lake。

Ice Lake和Comet Lake是英特尔第10代酷睿处理器系列中的两个不同架构,它们适用于不同的应用领域。Ice Lake适用于轻型移动设备和需要较低功耗的场景,提供良好的续航时间和图形性能;而Comet Lake则适用于主流笔记本电脑、游戏设备以及需要更高计算性能的工作站和桌面应用。

本文围绕X86 CPU架构展开,介绍了内核版本、boot相关组件,如A20、KBC等,还阐述了crypto、entry等内容。提及Kprobes用于内核调试,分析了X86南北桥结构及技术迭代,最后梳理了Intel x86 CPU架构的演进历程和架构特性。

本文围绕X86 CPU架构展开,介绍了内核版本、boot相关组件,如A20、KBC等,还阐述了crypto、entry等内容。提及Kprobes用于内核调试,分析了X86南北桥结构及技术迭代,最后梳理了Intel x86 CPU架构的演进历程和架构特性。

344

344

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?