视频十四:综合分析PS和PL部分对OLED驱动进行加速

0,从C语言的软硬交界面开始分析,确定要加速的部分。

1,首先分析时序,写加速器。

2,仿真加速器。

3,将代码PORT到AXI_LITE接口,并注意处理READY信号。

4,更新SDK的代码,下板子运行。

总结:

给大家展示了软件硬件协调设计的加速方法的分析和实现。软件PS部分和PL部分合理分工。

分离较高频度执行的部分,分离硬件可以加速的部分。

注意总线的延迟。AWREADY .WREADY. RREADY .

存在问题:

总线挂起导致处理器等待,耽误了处理器的运行,可以通过FIFO来实现协调。

1.仿真调试(看时序)

→把视频十三的vivao的文件拷贝过来用;

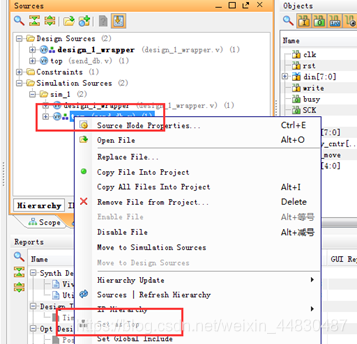

→add source →add or creat contraints →add file 把文件send_db增加进去;

→在simulation source 进行设置顶层(因为我设置了,所以灰色)

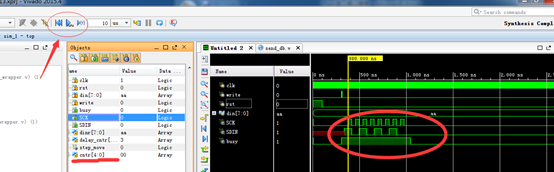

→点击run systhesis →点击run simulation →选择第一个

→点击run(下图;;要把仿真时序图调出来)

→cntr拖过去 →点击run;(因为run会很久所以run一段时间之后点取消就可以了看到cntr的一段波形)

2.配置ip核:

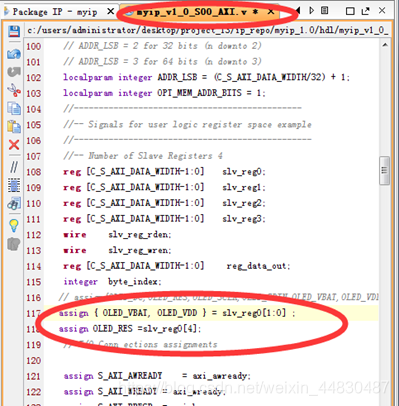

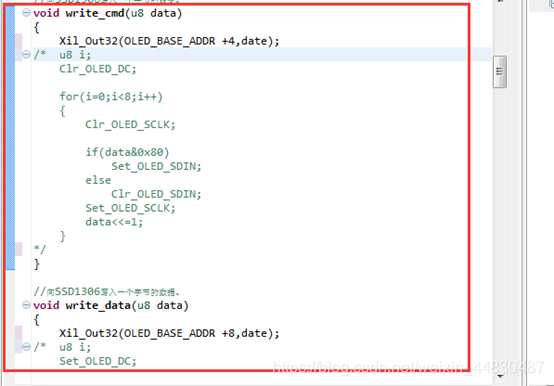

→对这三个进行加速控制OLED_DC, OLED_RES, OLED_SCLK, OLED_SDIN:

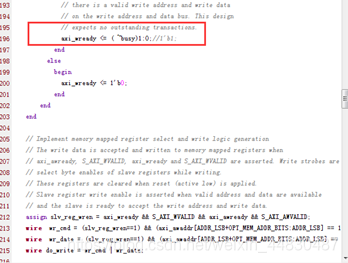

修改myoled ip 里的axi:

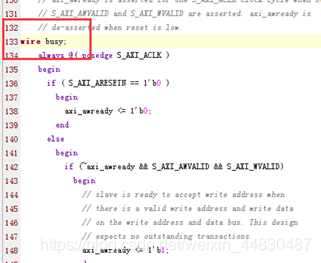

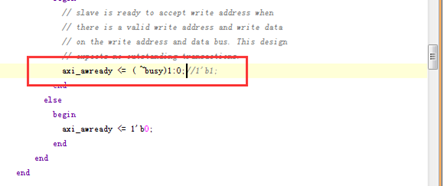

busy必须在他之前定义;

(里面主要是对这七根线就行了配置)

(红色的为修改部分)

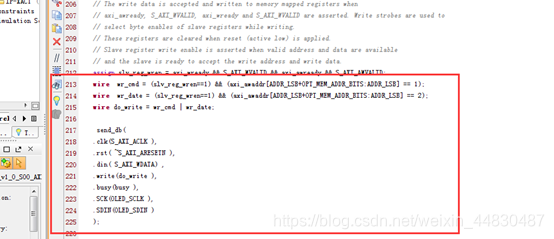

并在两出busy修改:如下

修改完成之后我出现以下错误:[Synth 8-439] module ‘send_db’ not found [“c:/users/administrator/desktop/project_13/ip_repo/myip_1.0/hdl/myip_v1_0_S00_AXI.v”:223];

解决办法:在修改ip核的那个vivado重新添加那个send_db文件;

3.→打包Ip;

→sdk里面修改底层驱动:(加速部分)

→3.下载bit;

→launch

→实验结果和上一个一样;

总结 :前14个视频为基础操作以及一些基础知识;熟练掌握vivado,sdk,和uboot制作固化包的操作;

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?