ICT 数字测试原理 24 - -使用VCL进行高级测试2 时序

文章目录

撰写时序部分

在时序部分中,您可以建立参考时钟和向量驱动和接收时间。在Mux系统中,您还可以定义控制格式化驱动器和接收器的定时设置。

请参见系统时钟和定时设置(Mux系统)。

撰写向量定义部分

如果您的测试只使用PCF向量,则不需要向量定义部分。

在Mux系统上,使用定时设置语句为每个需要的向量定义添加对定时设置的引用。

撰写向量执行部分

向量执行部分基于前面部分中定义的资源、向量和定时设置以及本节中的任何PCF向量,控制测试的流程。在该部分,您的任务是安排语句以正确的顺序执行向量,并在需要时纳入PCF向量。

要完成此部分,您需要了解定时设置和向量的关系、向量在管道中对归位循环的影响以及如何将PCF向量纳入测试中。请参见PCF(模式捕获格式)向量和管道。

VCL语句

表3-1简要描述了高级测试语句。有关更多信息,请参考所示的主题。

VCL语句描述

| 语句 | 测试部分 | 描述/主题 |

|---|---|---|

| data | 向量定义 | 开始一个数据块;定义由向量执行语句依次应用于一组引脚的可变引脚状态。 数据块 |

| dut clock period | 时序 | 为被测板建立一个时钟驱动器并指定时钟周期(参见输入格式化时钟)。 DUT时钟 |

| dynamic | 声明 | 在使用变量和数据块的测试中,指示MPA在需要的地方分配动态资源,以加速运行时的数据下载。 动态引脚分配 |

| end data | 向量定义 | 标记数据块的结束。 数据块 |

| end pcf | 向量执行 | 标记PCF向量块的结束。 将PCF向量集成到测试中 |

| end segment | 向量执行 | 标记一块分段向量的结束。 程序段 |

| file | 向量定义 | 将文件中的数据读入数据块。 数据块 |

| generate static test | 声明 | 在使用数据块的可执行测试中,指示编译器预编译文件中的动态数据(如果文件目前可用)。 从文件中预编译数据 |

| next | 向量执行 | 递增数据块中的数据计数器。 数据块 |

| outputs reference clock | 声明 | 声明用于同步参考时钟的输出(接收器)引脚,该时钟决定测试时序。 外部同步参考时钟(pll) |

| pcf | 向量执行 | 标记PCF向量块的开始。 将PCF向量集成到测试中 |

| pcf order is | 声明 | 指定PCF向量应用的引脚组。 将PCF向量集成到测试中 |

| piped | 向量执行 | 用于归位循环中的向量执行语句的次要关键词;在从循环中退出时,它标识将在管道中的向量。 管道 |

| rewind | 向量执行 | 将数据计数器重置为数据块中的第一个元素。 |

| segment | 向量执行 | 对具有大量可变向量的测试进行分段;防止溢出向量RAM。 程序段 |

| test time | 声明 | 指定VCL测试运行的估计正常时间。 测试时间 |

| values | 向量定义 | 为数据块分配数值。 数据块 |

| variables to groups | 声明 | 将可变引脚状态分配给一组引脚。 向量执行的变量 |

| use pcf order | 向量执行 | 将一组PCF向量与一组特定的PCF引脚关联。 |

| when | 声明 | 在电路库测试中,指定哪些引脚组可以有条件地影响其他引脚组的状态。 |

测试时间

测试时间语句在测试的声明部分使用;它指定了预期VCL测试运行的正常时间。

该语句作为输入由SAFEGUARD安全分析例程使用,以确定测试的超时时间。有关更多信息,请参见安全保护。该语句在测试运行时包含时间不确定性元素时是必要的——即等待、暂停和无法计数的归位循环等语句,其执行时间未知(参见下一个标题)。测试时间由安全例程用来确保如果发生故障,测试不会运行过长时间——例如在归位循环期间。

在编译测试时,安全例程计算两个时间:测试正常运行的时间和测试可以运行的最大安全时间(安全意味着上游设备不会被损坏)。正常时间(加上额外的安全因素)成为测试的超时时间。然而,如果正常运行时间长于安全运行时间,则测试会被禁止运行(除非在运行时指定了无安全保护)。

如果测试包含时间不确定性语句,则安全例程在计算正常运行时间时作出以下假设:暂停和等待不会发生;无法计数的归位循环将在第一个"如果通过则退出"语句退出,并且在混合测试中,模拟测试不会运行。如果此类测试中未包含测试时间语句,则测试将被禁止运行。

当包含测试时间语句时,安全分析例程接受指定的时间作为超时值。然而,如果指定的测试时间长于上游设备超驱动的安全时间,则测试将通过正常方式被安全地禁止。

计算出的时间显示在编译器列表中,因此如果您不知道测试时间值应该是多少,可以在没有测试时间语句的情况下编译测试。然后使用列表中显示的计算值来确定适当的测试时间值,然后使用该新值重新编译测试。或者,您也可以使用适当的调试例程从已知良好的电路板中得知测试时间。

测试时间语句仅适用于使用它的VCL测试;它对其他任何测试没有影响。没有时间不确定性语句的VCL测试不需要测试时间语句。

系统时钟

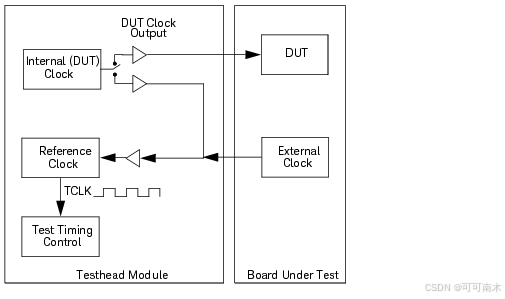

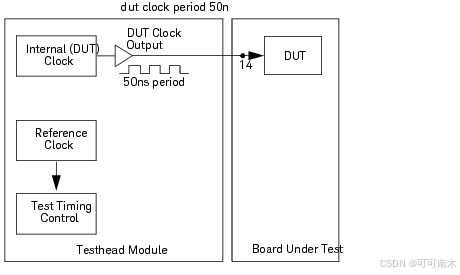

测试系统有两种类型的时钟,如图3-1所示:参考时钟,称为TCLK,以及内部时钟,也称为DUT时钟。

- 参考时钟控制测试时序,可以同步到内部时钟或外部时钟,通常位于被测板上。

- DUT时钟由内部时钟驱动,向被测板提供一个连续的方波。内部时钟可以驱动DUT时钟输出或同步参考时钟。通常,内部时钟不能同时用于这两个目的。不过,可以通过VCL程序间接地实现这一功能——请参阅测试与DUT时钟同步。

图3-1展示了测试头中一个模块的时钟方案。时钟电路位于模块插槽6中的模块控制卡上,因此每个模块具有相同的时钟电路集。然而,在任何数字测试中只能使用一个模块来控制测试时序。

图中显示了两个时钟:参考时钟和内部时钟。参考时钟生成名为TCLK的信号,决定测试时序。该时钟由锁相环生成,必须同步到内部时钟或外部时钟。如果参考时钟同步到外部时钟,内部时钟可以驱动DUT时钟输出。在一个测试头模块中,内部时钟可以驱动DUT时钟输出或同步参考时钟。在图3-1中,通过连接到内部时钟输出的开关对此进行了展示。

在DUT配置中,没有用于同步参考时钟的内容;因此,测试头中必须有另一个模块提供参考时钟以控制测试时序。然而,无论模块数量多少,任何VCL测试都不能使用超过一个的参考时钟和一个的DUT时钟。

测试头模块中的时钟方案

当不用于同步参考时钟时,内部(DUT)时钟完全独立于参考时钟,两者可以有不同的频率。如果测试头有多个模块,那么一个模块可以控制测试时序,而另一个模块为板上的设备提供独立时钟(DUT时钟)。这有时是测试微处理器和一些电信设备所必需的。

如果您使用DUT时钟和一个外部时钟来同步参考时钟,那么这两个时钟再次是独立的。然而,如果外部时钟源本身是由一个由DUT时钟驱动的电路派生而来,那么参考时钟(以及测试时序)可以间接地同步到DUT时钟。这样做的好处是为电路板和测试提供一致的时钟时序,同时让测试系统看起来好像时序是由被测板派生的(参见测试与DUT时钟同步)。

参考时钟 (TCLK)

所有数字测试都由参考时钟控制。VCL测试中的语句决定是使用内部时钟还是外部时钟来生成参考时钟。

参考时钟在整个VCL测试中无间断运行;它生成一个名为TCLK的信号,用以控制向量或定时设置的时序(在使用它们的测试中,仅适用于Mux系统)。定时设置控制格式化驱动器和接收器的时序,以及向量的时序。

参考时钟是一个可编程振荡器,带有锁相环,可以同步到两个源之一:系统的内部时钟或外部时钟(见图3-1)。不同的时钟有不同的频率范围;有关频率范围,请参阅系统的规格说明。参考时钟的锁相环包含倍频器和分频器,使其能够生成同步频率的整数倍或分数倍。两个频率之间的倍频或分频可以是2的任意幂,但生成的参考时钟的频率必须在其系统规范的范围内。

欲了解更多细节,请参阅:

- 事件和事件空间(Mux系统)

- 内部同步参考时钟

- 外部同步参考时钟(pll)

- 预期和实际的时钟周期

事件和事件空间(Mux系统)

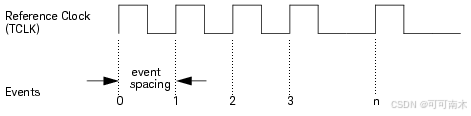

定时设置是与TCLK同步的。如图3-2所示,每个TCLK信号的开始被称为一个事件;事件与TCLK脉冲的上升沿一致。事件之间的空间(时间间隔)等于参考时钟的周期。测试中的所有活动都与事件相关。

事件用于定义定时设置,每个定时设置的长度用若干个事件来表示。因此,语句 “timing set Read_Word is 14 events” 定义了一个名为Read_Word的定时设置,它的长度为14个事件空间。如果TCLK的周期设置为100 ns,那么这个定时设置的长度为1400 ns。有关更多信息,请参阅定时设置(Mux系统)。

事件来源于参考时钟

内部同步参考时钟

在VCL测试中设置参考时钟的方法有所不同,具体取决于VCL测试是向量周期/接收延迟测试还是使用定时设置的测试。

向量周期/接收延迟测试

向量周期语句决定了哪个时钟同步参考时钟。如果语句的pll参数被省略,则选择内部时钟。例如,

vector cycle 600n

选择内部时钟。注意,时钟周期没有被指定——系统软件会自动选择一个合适的周期来匹配向量周期时间和接收延迟语句中指定的时间。如果指定了pll参数,则选择外部时钟(参见外部同步参考时钟 (pll))。

使用定时设置的测试(Mux系统)

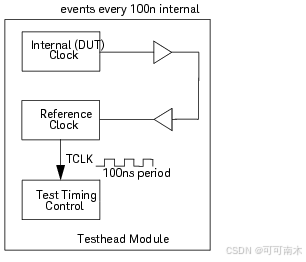

测试中的events every语句(在时序部分)选择参考时钟周期及其同步源。如图3-3所示,以下示例语句

events every 100n internal

指定内部时钟将在整个VCL测试过程中同步参考时钟;参考时钟的周期将为100 ns(10 MHz)。也就是说,TCLK和事件将如上所述每100 ns发生一次。有关您可以指定的时钟频率范围,请参阅系统的规格说明。

内部同步参考时钟

外部同步参考时钟 (pll)

如果参考时钟(TCLK)要由外部时钟同步,则需要两个步骤:建立资源和指定时序。与内部时钟一样,根据测试是否使用定时设置,建立时序的方法有所不同。资源的建立对这两种类型的测试是相同的。

建立资源

在测试的声明部分中的outputs reference clock语句指定被测板上的哪个节点或引脚是用来同步参考时钟的外部时钟的输出。对于任何一个VCL测试,只能指定一个引脚。

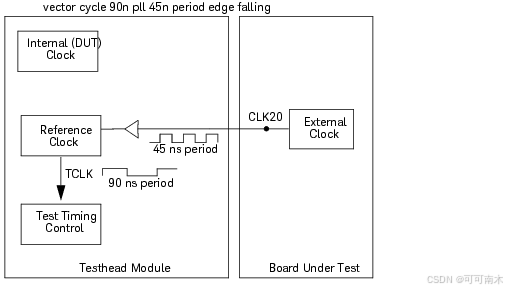

如图3-4所示,以下示例语句指定使用外部源来同步参考时钟。在这种情况下,外部时钟信号Ext_clock从被测板上的节点CLK20输出:

assign Ext_Clock to nodes "CLK20"

. . .

outputs reference clock Ext_Clock

assign语句将组名Ext_Clock分配给信号CLK20,outputs reference clock语句指定信号CLK20将同步参考时钟。

外部同步参考时钟 (pll)

每个模块的模块控制卡上有两个引脚可用作接收器来同步参考时钟。它们是引脚2和3,引脚1是参考时钟的接地。由于每个模块控制卡上有两个引脚,四模块系统上的板测试可以使用多达八个不同的外部时钟,在板测试的不同时间同步参考时钟。

向量周期/接收延迟测试

通过带有pll(锁相环)选项的向量周期语句在测试的声明部分中指定时序。例如:

vector cycle 150n pll 75n period edge falling

表示参考时钟将同步到外部时钟的下降沿,该外部时钟的周期为75 ns。向量周期时间可以是外部时钟周期的1到255倍。在此示例中,向量周期时间为150 ns,是时钟周期的两倍。

请注意,向量周期语句中指定的外部时钟周期是预期的时钟周期。这是SAFEGUARD例程在计算测试运行的安全时间时将用到的时间。当测试运行时,如果外部时钟的实际周期不同,那么测试时序将相应地改变(详见预期和实际的时钟周期)。

使用定时设置的测试(Mux系统)

测试的时序部分的events every语句指定两个时钟的周期:首先是参考时钟(TCLK),然后是同步(外部)时钟。以下是一个示例语句:

events every 300n pll 300n period edge rising

如以下讨论所述,两个时钟的周期不一定必须相同;然而,在此示例中,它们相同,均为300 ns。在此示例中,edge rising表示参考时钟(TCLK)将同步到外部时钟的上升沿。

参考时钟的周期可以与外部时钟的周期相同,也可以是其倍数或分数倍。如图3-4所示,以下示例语句将外部时钟的周期加倍:

events every 90n pll 45n period edge falling

同样,外部时钟的周期可以被划分;在此示例中,周期被除以4:

events every 75n pll 300n period edge rising

您可以使用2的任何幂来倍增或除以周期,但周期必须在系统规格指定的时钟范围内。

预期和实际的时钟周期

当指定了外部时钟时,参考时钟被预编程为期望特定的外部频率。这也是SAFEGUARD安全分析例程用来计算安全时序参数的值。

在VCL测试开始之前,外部时钟必须存在且稳定。当VCL测试开始时,根据为时钟选择的周期,参考时钟需要大约30毫秒的初始延迟来与外部时钟进行相位锁定。然而,在此期间,驱动器保持禁用状态;因此,测试不会开始,直到时钟锁定。另外,测试超时计时器在驱动器启用之前不会开始计时。

如果外部频率有细微的变化,由于锁相环的作用,参考时钟将保持稳定的频率。然而,如果外部频率发生永久性变化,则参考频率也会改变:改变的方向和幅度将取决于向量周期语句中指定的值以及外部时钟的实际频率。在极端情况下,参考时钟可能无法锁定到外部时钟。

当您编写使用外部时钟来同步参考时钟的VCL测试时,被测板上的时钟脉冲与参考时钟的脉冲之间会有一些时间延迟。这种时间延迟主要是由夹具布线引起的。对于短线夹具,时间延迟为一到三个纳秒。

DUT时钟

DUT时钟信号用于向被测板发送连续的时钟脉冲。如图3-5所示,DUT时钟是由测试头中的内部时钟派生的方波。如果您需要将DUT时钟信号发送到被测板,并且同时可以使用外部时钟同步参考时钟,那么只需在测试头中有一个模块即可,至少对于时钟用途而言。但是,如果您需要DUT时钟信号并打算将参考时钟与内部时钟同步,那么在测试头中至少需要两个模块。

DUT时钟独立于测试中的其他时序。它在VCL测试开始时启动运行,并在整个测试过程中持续运行,包括在暂停期间(暂停语句)。向被测板发送时钟可用于各种用途,例如模拟待最终安装板中系统的时钟线。

有两个语句与DUT时钟的定义相关:

- dut clock period(时序)

- inputs formatted clock(声明)

因为在向量周期/接收延迟测试中没有时序部分,dut clock period语句可以放在声明部分。

inputs formatted clock语句仅在需要DUT时钟时使用。该语句声明由DUT时钟驱动的设备或被测板上的引脚。一个VCL测试只能有一个DUT时钟。图3-5中示例指定被测设备的引脚14由DUT时钟驱动。

assign Free_Clock to pins 14

. . .

inputs formatted clock Free_Clock

dut clock period语句指定时钟的周期。一旦设定,时钟周期在整个测试期间保持不变。以下示例设置一个周期为50 ns(20 MHz)的时钟:

dut clock period 50n

使用DUT时钟

对于UnMux系统:

- 如果DUT时钟的周期指定为500 ns或更长(小于或等于2 MHz),则该时钟将自动路由到引脚卡上的一个驱动器。

- 如果指定的周期小于500 ns(大于2 MHz),则时钟被路由到ControlXTP卡上的引脚16。此引脚不能用于超电压。它具有匹配驱动100欧姆的固定TTL电平。定义驱动器和接收器引脚特性的语句(例如set ref)不影响模块控制卡上的DUT时钟引脚(16)。

对于Mux系统:

- 如果DUT时钟的周期指定为50 ns或更长(小于或等于20 MHz),则该时钟将自动路由到引脚卡上的一个驱动器。如果需要具有超电压能力的引脚,则会自动从能够超电压的引脚卡中选择(例如HybridPlus卡)。如果引脚不需要超电压,则会从当时最方便的引脚卡类型中选择引脚。

- 如果指定的周期小于50 ns(大于20 MHz),则时钟被路由到ControlXTP卡上的引脚16。此引脚不能用于超电压。它具有匹配驱动100欧姆的固定TTL电平。定义驱动器和接收器引脚特性的语句(例如set ref)不影响模块控制卡上的DUT时钟引脚(16)。

在使用外部时钟时,测试开始前会有一个延迟,以允许参考时钟时间与外部时钟锁定。在延迟之后,启用驱动器并启动测试超时计时器。但是,如果测试使用的是从引脚卡派生的DUT时钟(即,不是来自模块控制卡上的引脚16),则必须立即启用驱动器以启动DUT时钟。这意味着在参考时钟锁定到外部时钟之前,测试超时计时器就已启动。由于SAFEGUARD安全例程无法预测延迟时间,您应使用测试时间语句来设置超时;否则测试可能在完成之前超时。

同步测试至DUT时钟

您不能同时使用内部时钟作为DUT时钟并直接将其作为同步源连接到参考时钟(TCLK)。但是,您可以通过在测试中使用适当的VCL语句间接地做到这一点。目的是将DUT时钟信号驱动到板上,然后从板上接收相同的信号作为外部时钟来同步参考时钟。对于测试系统而言,内部时钟可以用作DUT时钟,因为外部时钟将用于同步参考时钟。

图3-6展示了如何在电路板和测试头之间进行连接。设备U16正在测试中,并将由DUT时钟驱动,同时也需要同步测试。由于可能存在信号退化的情况,您必须将DUT时钟驱动引脚与参考时钟接收引脚隔离,而不是直接将它们连接在一起。可以通过在DUT时钟线上放置一个缓冲器来实现,无论是在被测板上还是在夹具上。在这种情况下,缓冲器U1A位于被测板上。

DUT时钟信号被驱动到引脚9,并从引脚21接收。在此示例中,DUT时钟的周期为50 ns,向量周期为200 ns。

示例3-1中的VCL测试语句设置了图3-6所示的电路。

示例3-1

与DUT时钟同步的参考时钟的VCL代码

! 在分配部分 . . .

assign Dut_in to pins 9

assign Dut_out to pins 21

. . .

inputs formatted clock Dut_in ! 将DUT时钟驱动到电路板上

outputs reference clock Dut_out ! 从电路板接收缓冲的DUT时钟

. . .

! 参考时钟同步到外部源

vector cycle 200n pll 50n period edge rising

dut clock period 50n

. . .

从图3-6可以看出,需要编辑U16的测试以包含时钟和缓冲器。引脚9需要被指定为输入,而作为输入的引脚21需要更改为输出。您可以将U16的库源文件复制到您的自定义库中并在那里进行更改。

参考时钟与DUT时钟同步

1007

1007

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?