一、读取设计文件

首先进入工作目录,启动spyglass,本实验工作目录为lab1。

cd lab1

spyglass &

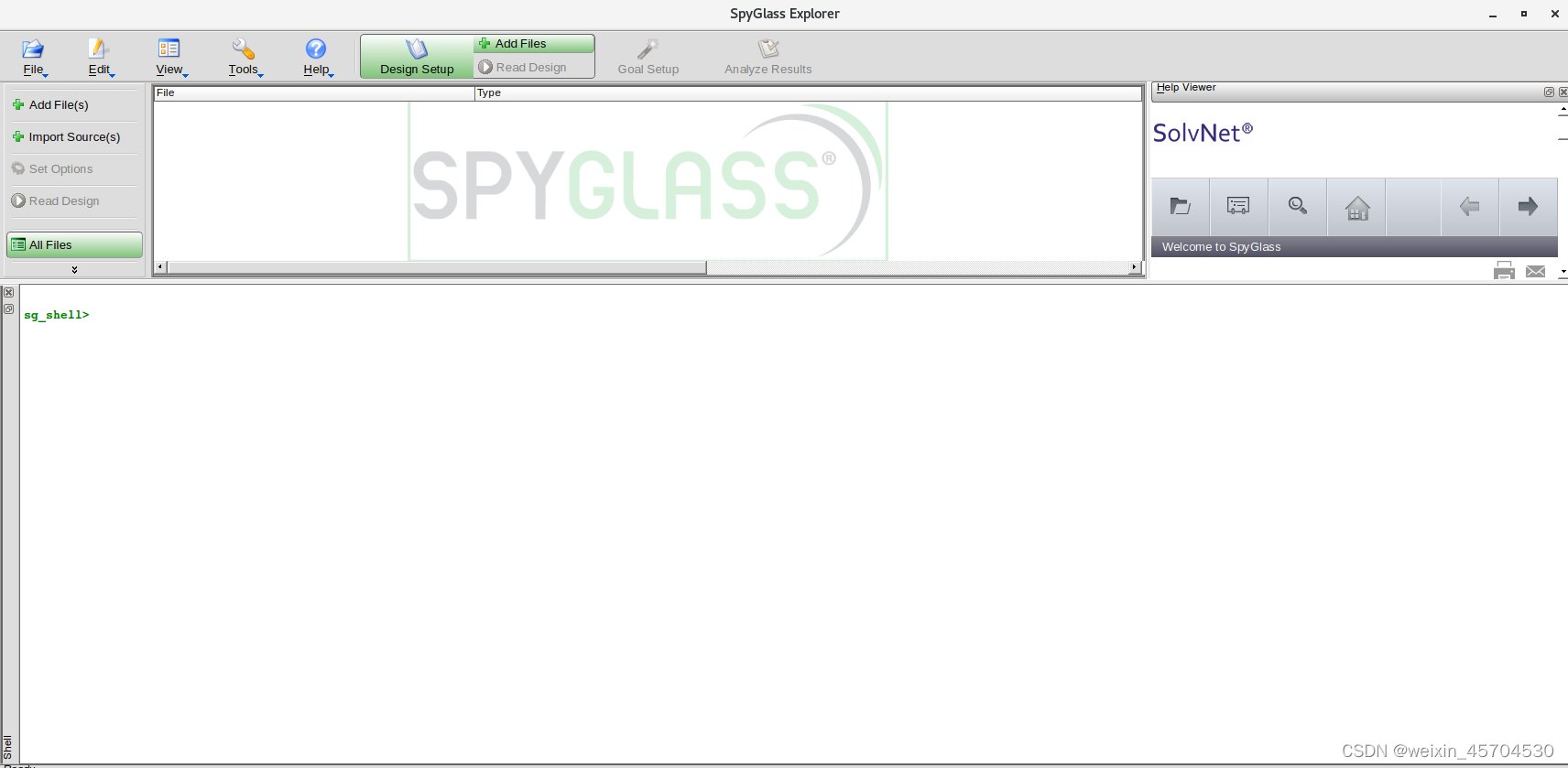

之后可以看到如下界面

然后点击“Add File(s)”, 此时会打开添加文件窗口。左侧窗口用来切换目录和选择文件,右侧显示已经选择的文件。左侧选择文件后点击中间的“Add”即可完成文件的添加,点击“OK”退出当前窗口。

本实验中需要读取的文件为:

../rtl/ahb2wb.v

../rtl/wb_subsystem.v

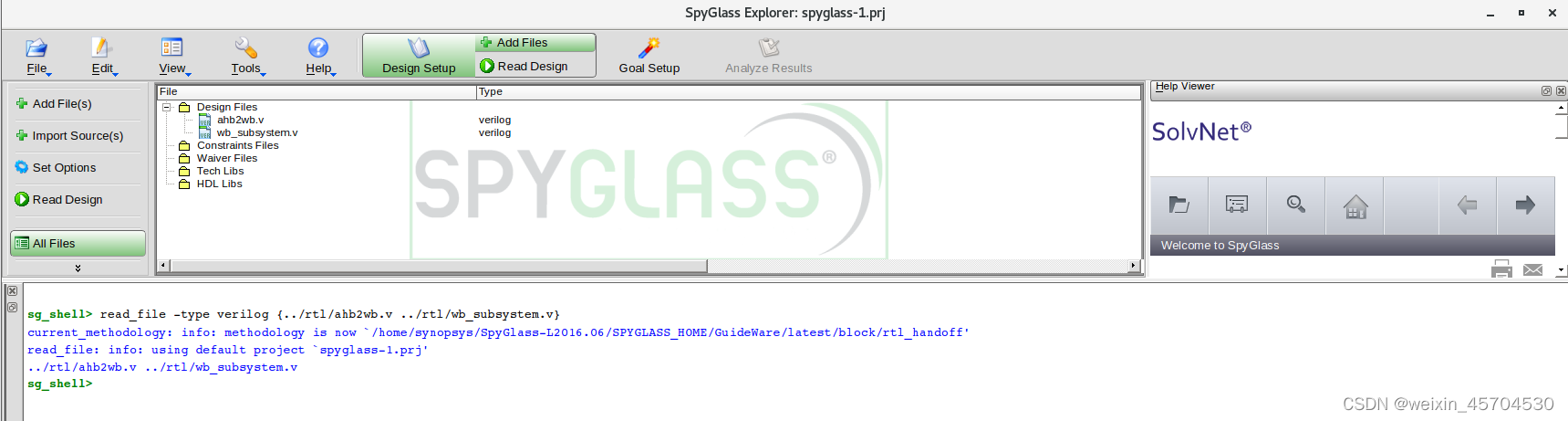

读取文件后的界面如下图

通过命令行的方式,一样可以达到添加设计文件的目的,如下

read_file -type verilog {../rtl/ahb2wb.v ../rtl/wb_subsystem.v}

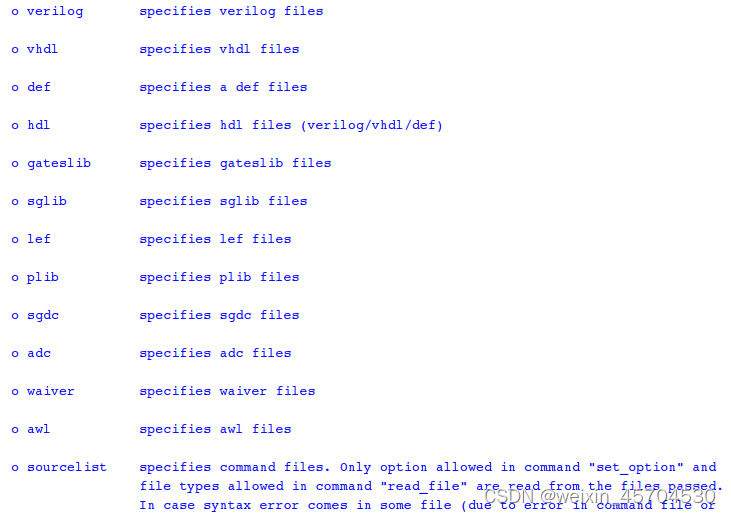

-type 有如下选项,可通过man read_file查看

二、设置顶层模块与编译设计

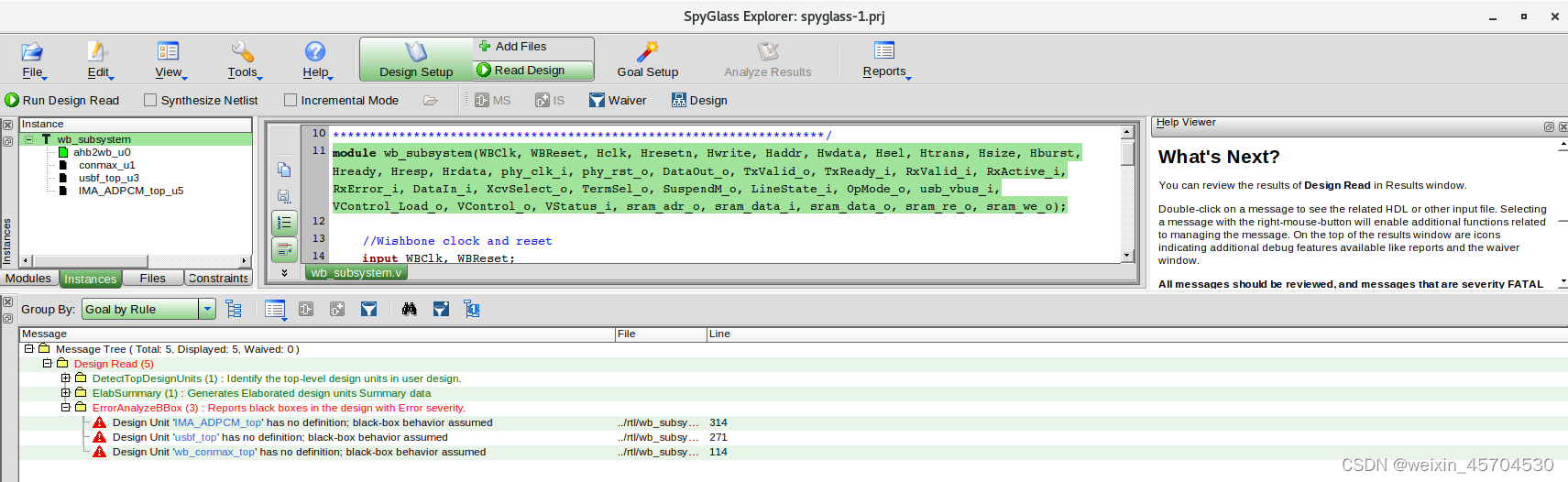

添加完文件后点击“Set Options”,然后选择列表中选择“Top Level Design Unit”,Value值为顶层模块名(此处顶层模块为wb_subsystem)。之后点击“Read Design”,再在左侧点击“Run Design Read”开始进行设计文件编译和分析,在读取完成后会在下方窗口列出问题。如下图所示:

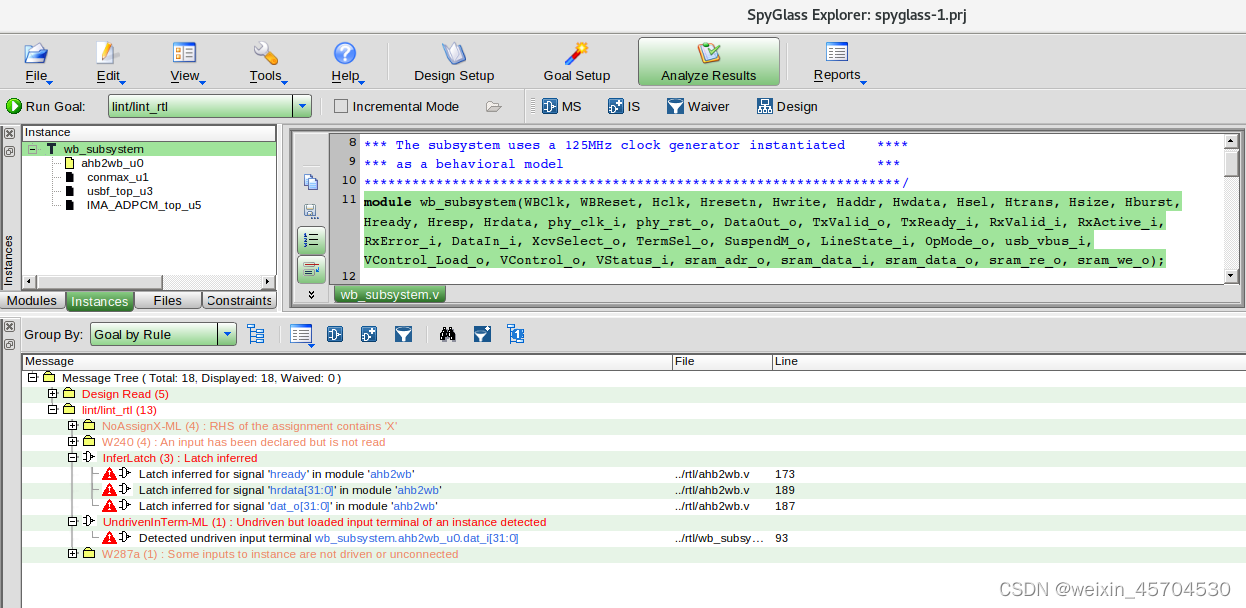

左侧instance下文件不同颜色标识意义为:绿色表示该模块可进行分析,但不可进行综合;黑色表示该模块作为黑盒子存在;白色表示该模块可综合。需要注意,只是读取设计并不会完成综合,因此也不会创建相关的原理图。因此,为了使用spyglass,首先应该解决黑盒子问题,为此需要选择复选框Synthesize Netlist然后重新运行Design Read。

三、静态分析

使用spyglass进行分析不要求完整的工程文件。

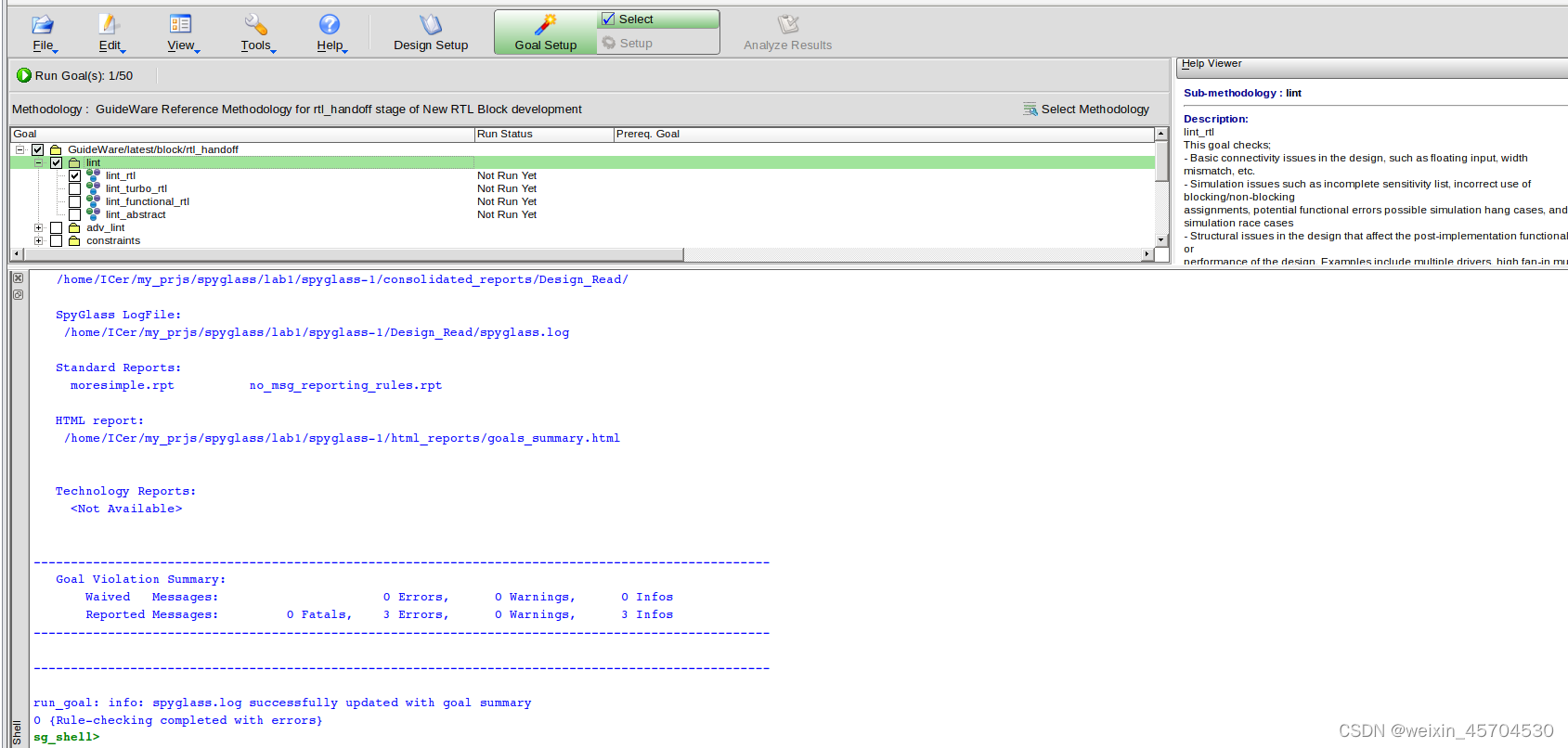

在窗口上方中间点击Goal Setup ,然后在主窗口区勾选Lint_rtl(在lint中点击+即可见),如下图。虽然可以一次选择多个目标设置,但分析过程是顺序执行的,只要前面的检查通过了才会进行后面的检查。

然后点击“Run Goal(s) ”,当运行完成,会自动弹出“Analyze Result“窗口。

得到分析结果后,首先查看Lint分析结果。首先展开lint/lint_rtl文件夹消息。错误信息以红色显示,警告以橙色显示,信息以绿色显示。选择并展开inferLatch Error文件夹。双击第一条违规消息。此时与错误相关的代码会在RTL代码窗口中显示出来,如下所示。

此时来对该问题进行分析。由消息可知,由于设计问题生成了非期待的锁存器。可以看到违规消息左侧有一个

在这里插入图片描述,这个意思是该违规消息包含一些原理图方面信息。通过点击

可以打开相关的逻辑示意图:

在本次例子中,是因为hready信号在没有else的if语句中被赋值。如果这些Latch是故意的,那通过屏蔽对该处的规则检查即可。如果需要修改代码,可以在代码窗口中点击有问题的代码行,使得光标落于该行,然后点击e即可将打开默认的编辑器进行代码编辑。编辑完后要重新运行Goal。

参考:https://blog.csdn.net/qq_30843953/article/details/109629618

7143

7143

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?