本练习建立在前一个实验的基础上。在本实验中,我们将使用–batch选项‘在批处理模式下运行SpyGlass。同样的操作也可以在GUI模式下完成。

spyglass -project wb_subsystem.prj -designread -batch

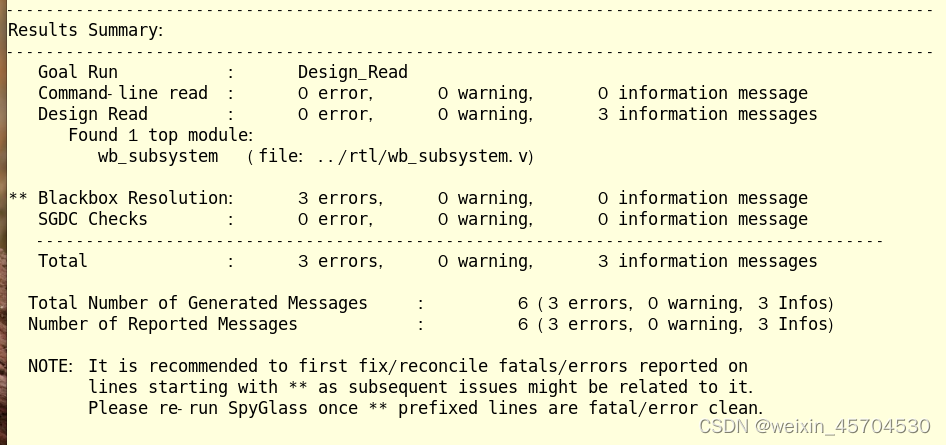

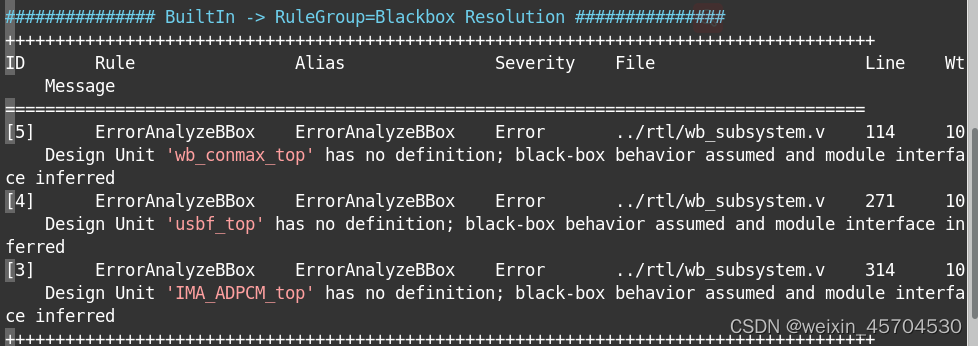

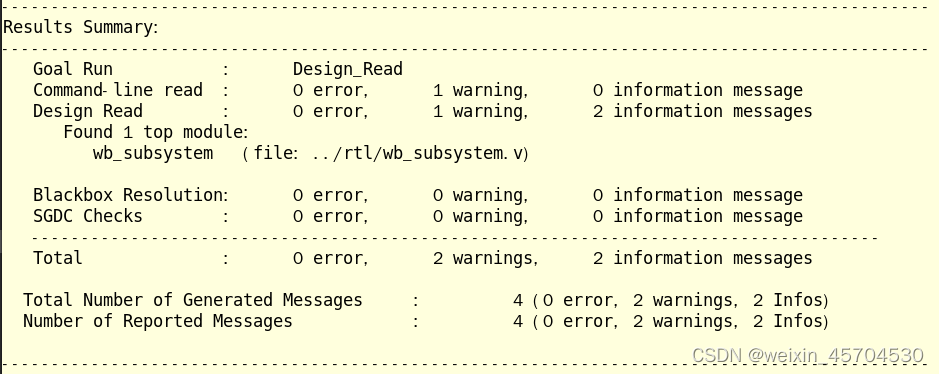

在本实验的工程中,终端显示如下:

打开wb_subsystem.prj文件,在##Data Import Section下添加如下语句:

read_file -type sourcelist …/rtl/usb/file.list

read_fiel -type sourcelist …/rtl/wb_conmax/file.list

将下面命令的选项改为yes:(在**##Common Options Section**下)

set_option designread_enable_synthesis yes

将文件保存后重新运行Design Read。

通过上面的文件添加和设置消除了之前的黑盒问题,但因为新的文件加载也引入新的黑盒问题,如下所示

它们看起来是被实例化的标准单元,但不知何故,它们的定义没有被提供。这些单元格很可能是使用-y/-v选项传递的,所以让我们浏览一下“usb”中的目录,看看是否有任何丢失的库文件。可以看到usb_lib目录存在于“usb”目录中,但是没有-y被指定为file.list的一部分。

3.通过下列的语句来读取缺失的部分:

read_file -type sourcelist ../rtl/usb/file.list

read_file -type sourcelist ../rtl/wb_conmax/file.list

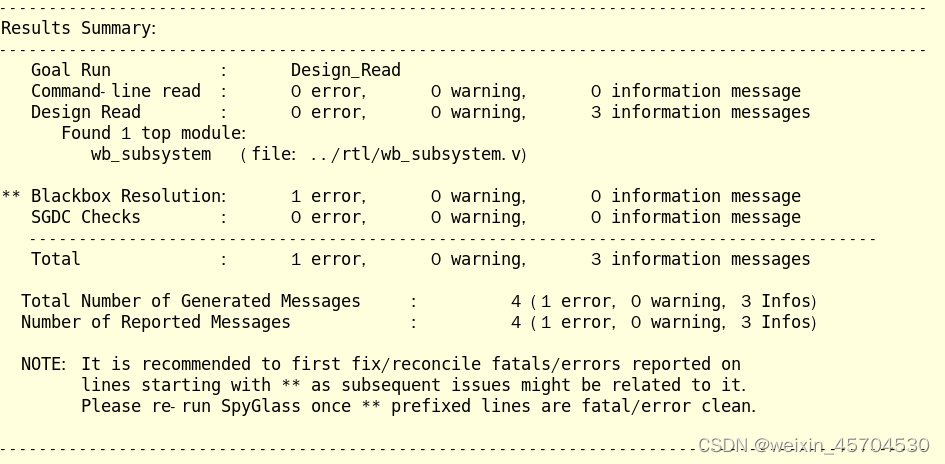

将文件保存后重新运行Design Read来检查是否解决了USB黑盒问题。结果如下:

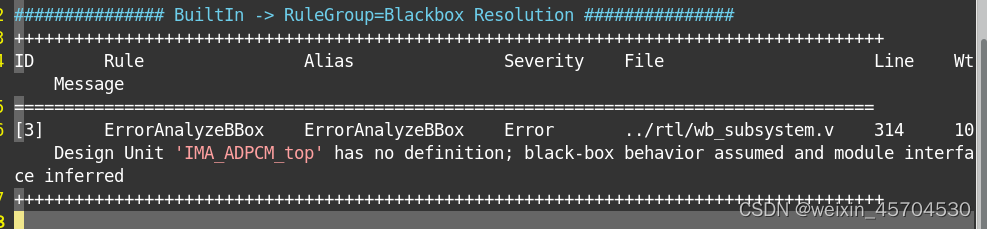

moresimple.rpt报告内容如下:

可以看到剩下的一个黑盒错误来自块“IMA_ADPCM_top”。这部分采用VHDL设计,出现黑盒问题原因是其设计文件尚未包含在.prj文件。

预编译库来解决IMA_ADPCM_top黑盒问题。

要预编译一个HDL库,您必须指定要在逻辑库中预编译的文件列表,以及逻辑库名称和物理目录之间的映射。这是使用lib_hdlfiles(定义要编译到命名库的文件)和lib(将命名库映射到物理目录)选项完成的(添加到**.prj文件的##Data Import Section**部分)

read_file -type sourcelist ../rtl/ima_adpcm/file.list

其中vhd_file.list内容为需要编译的VHDL文件的路径列表。接下来删除包含上次运行保存的网表的结果目录,然后重新运行设计验证是否解决了黑盒问题:

rm -rf wb_subsystem

spyglass -project wb_subsystem.prj -designread -batch

通过第二次的实验我们解决了全部黑盒问题。

参考:https://blog.csdn.net/qq_30843953/article/details/109629618

1264

1264

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?