目录

由b站视频第12讲 时序分析中的基本概念和术语_哔哩哔哩_bilibili中总结得出(学习笔记)

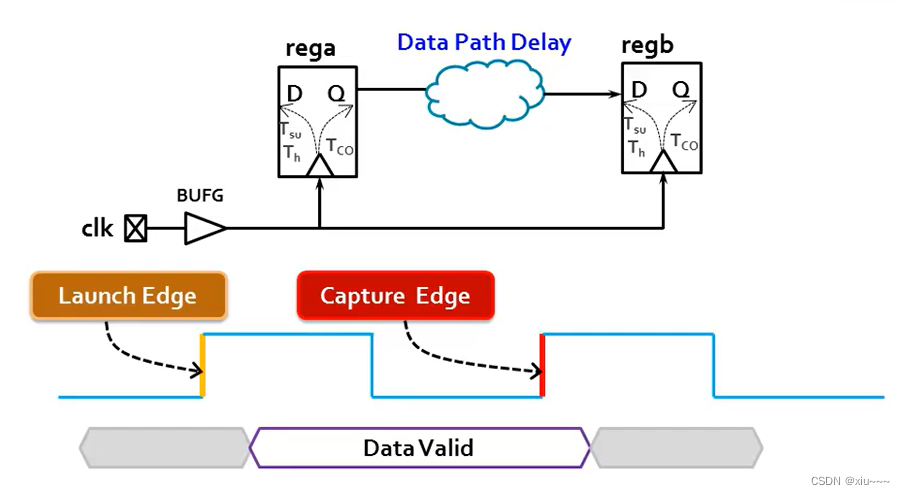

一、发起沿和捕获沿

rega为源端寄存器,regb为目的端寄存器。

发起沿(Launch Edge):源端寄存器中发送数据的时钟边沿(通常选择上升沿)。

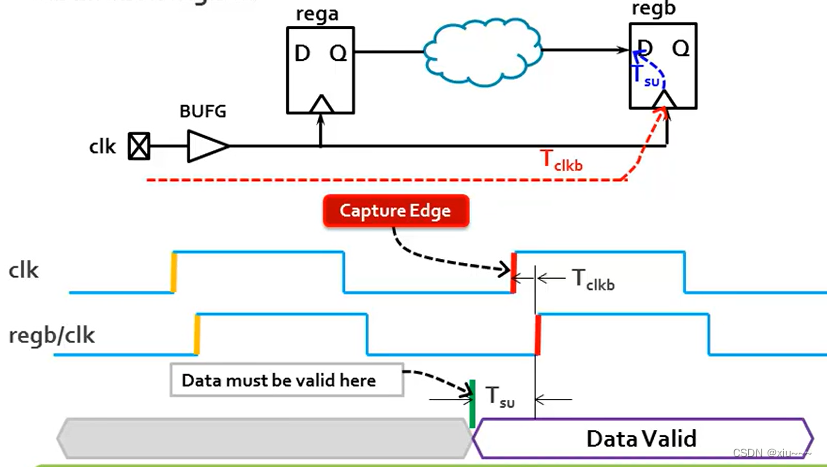

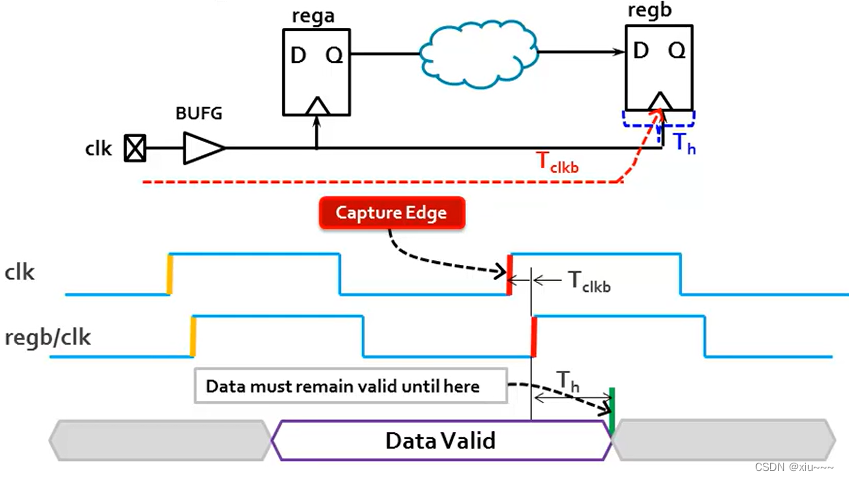

捕获沿(Capture Edge):目的端寄存器捕获数据的时钟边沿。

通常发起沿与捕获沿有一个时钟周期的区别,且捕获沿是下一个发起沿。

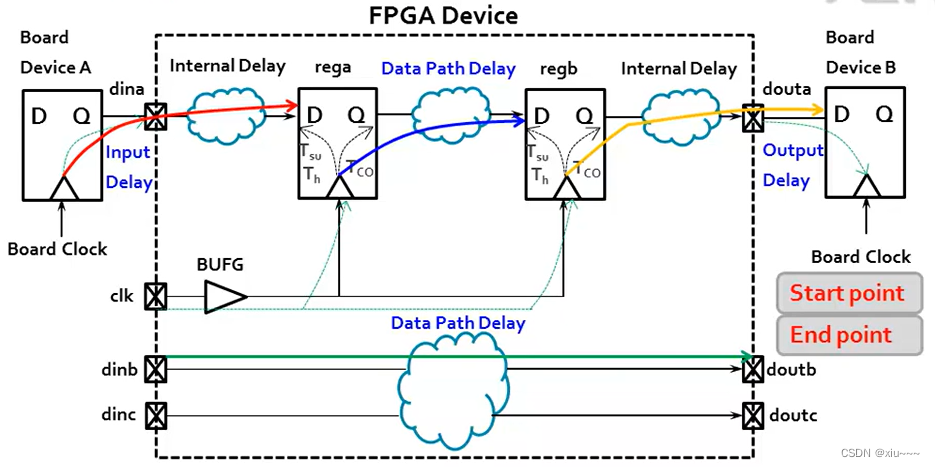

二、四种时序路径

1.Device A(外部设备)的时钟到FPGA的第一级寄存器的输入端口。

起始点:Device A最后一级寄存器的时钟

终止点:FPGA第一级寄存器的数据端口

2.两个同步寄存器之间的路径,如rega到regb。

起始点:rega的时钟端口

终止点:regb的数据端口

3.FPGA最后一级寄存器到Device B的路径。

起始点:FPGA末级寄存器的时钟端口

终止点:Device B数据端口

4.FPGA端口到端口的路径。即纯粹的组合逻辑路径

(前三个时序路径可以归为1类,都是从发送寄存器的时钟端口到接收寄存器的数据端口,区别在于寄存器是否在同一个芯片)

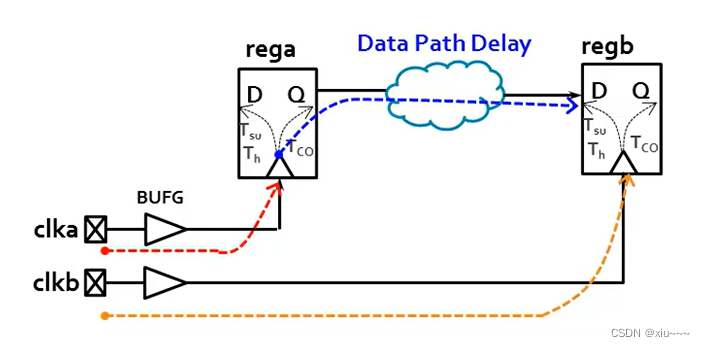

三、常规的时序路径模型

1.源端时钟路径

起点:时钟输入端口 终点:rega的时钟端口

2.数据路径

起点:发送源时钟 终点:接收寄存器的数据端口

3.目的端时钟路径:

起点:时钟输入端口 终点:目的端时钟端口

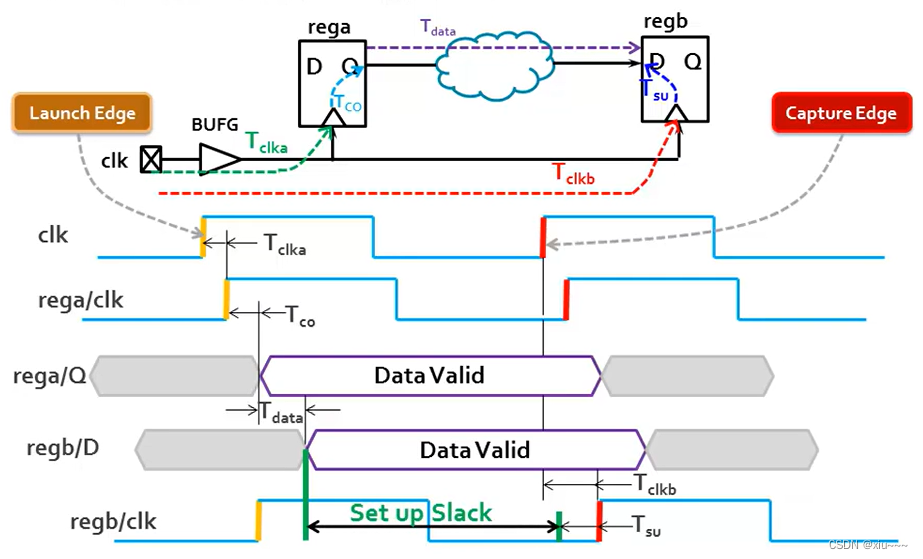

四、数据到达时间和数据需求时间

基准时间点:发送沿为0时刻基准点。

数据到达时间Data Arrical Time = Launch Edge + Tclka + Tco + Tdata

数据到达时间为时间点,是在 Launch Edge 的基础上,加上时钟到达rega的延时Tclka,数据到达Q端口的延迟Tco,以及组合逻辑延时和线延时Tdata。

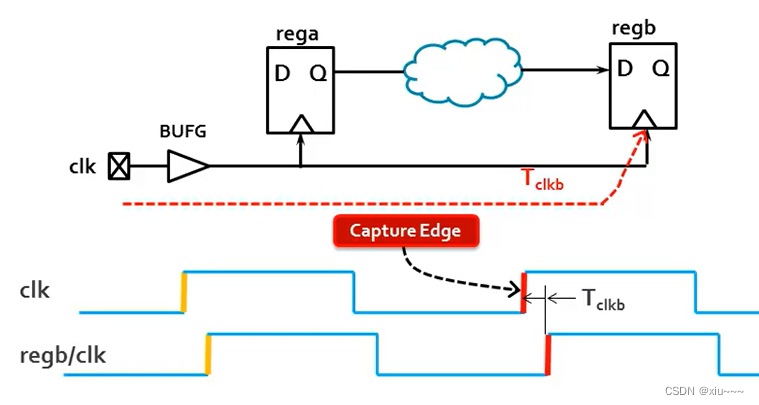

时钟到达时间Clock Arrvial Time = Capture Edge + Tclkb

(仍以发送沿为0时刻基准点,捕获沿为发送沿+1个时钟周期)

数据需求时间——建立情况(为数据被稳定捕获的最小时间)

Data Required Time = Clock Arrival Time - Tsu - Set up uncertainty

其中,为考虑时钟的抖动,加入Set up uncertainty。

数据需求时间——保持情况(捕获数据后数据还需稳定的最小时间)

Data Required Time = Clock Arrival Time + Th + Hold uncertainty

最终,由Tsu和Th可以确定数据的有效窗口。

五、建立时间裕量和保持时间裕量

满足建立时间裕量,则数据可以被目的端寄存器稳定捕获到;不满足,则说明数据没有提前Tsu到达目的端寄存器。以原始时钟为起始点,如图所示,Set up Slack为建立时间裕量。结合上面的数据需求时间,可以得到如下式子:

Setup Slack = Data Required Time(Setup ) - Data Arrical Time(Setup)

其中需要注意数据到达时间为Current Data的到达时间。

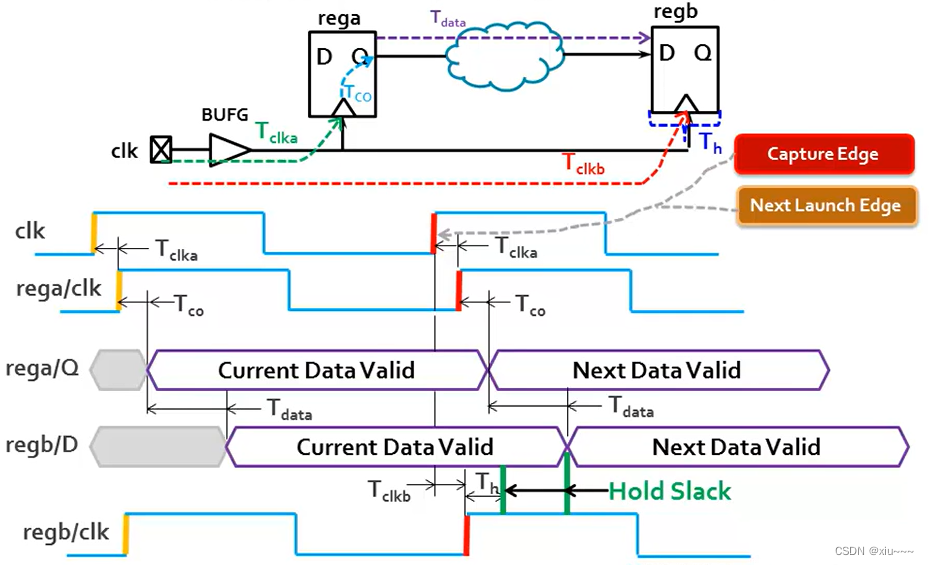

满足保持时间裕量,说明数据在到达目的端寄存器后,仍保持了大于Th的时间;不满足,说明Next Data太早到来,破坏了Current Data。

Hold Slack = Data Arrical Time(Hold) - Data Required Time(Hold)

其中需要注意数据到达时间为Next Data到达时间。

当slack为正,则满足时序需求,否则不满足。且公式均适用于FPGA内部、IO端口以及异步控制。当Setup Slack为负,说明Data Arrical Time偏大,数据到达太晚;当Hold Slack为负,说明Data Required Time偏大,regb的时钟延迟过大。(注意Tsu和Th由FPGA芯片工艺决定,用户无法改变)

系统频率Ts由以下两个公式决定:

Tdata = Tlogic + Tnet

Ts >= Tco + Tdata + Tsu

其中逻辑延时Tlogic为组合逻辑的延迟(与代码有关),走线延时Tnet为布局布线的延迟(与布局风格有关)。由于Tsu和Th用户无法改变,因此若要提高系统频率,要从Tdata入手。

本文介绍了FPGA时序分析中的基本概念,包括发起沿和捕获沿的定义,四种时序路径模型,数据到达和数据需求时间的计算,以及建立和保持时间裕量的重要性。通过理解这些概念,用户可以优化设计以确保信号时序正确性。

本文介绍了FPGA时序分析中的基本概念,包括发起沿和捕获沿的定义,四种时序路径模型,数据到达和数据需求时间的计算,以及建立和保持时间裕量的重要性。通过理解这些概念,用户可以优化设计以确保信号时序正确性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?