相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

前言

追溯到最早之前,拓扑技术(Topographical)这个概念是由Synopsys在1999年末推出Physical Compiler这个物理综合工具时引入的。那么物理综合又是什么呢?随着半导体工艺尺寸的缩小,人们已经广泛使用50nm以下的工艺进行ASIC设计与制造,但这带来了一些问题。

在之前旧的工艺中(比如200nm以上),单元延迟(Cell Delay)在设计的时序路径中占了相当大的比例,因此在人们在研究设计方法学和设计EDA工具时将重心主要集成在减小单元延迟而相对忽视互连延迟(Interconnect Delay)。但对于先进工艺而言,单元延迟降低了,可互连延迟却在提高,即使使用铜互连代替铝互联在一定程度上有所缓解,但互连延迟已经相当甚至超过单元延迟。

早期的综合工具(比如DC Expert)使用线负载模型(Wire Load Model),它根据扇出估算连线长度并得到RC参数,最终使用Elmore模型计算互连延迟,它并不考虑连线所连单元的布局,因此在先进工艺中是很不精确的。例如,对于两组完全相同的逻辑,它们未来的布局可能很不相同,但综合工具根据线负载模型却作出了互联延迟一样的假设。

但在布局布线工具(比如IC Compiler)中,互连延迟是根据具体布线结构来计算的,每层金属拥有不同RC参数,通孔(Via)也将被考虑在内,使用的模型也可能是更高级的Arnoldi模型。这会导致布局布线前/后的时序出现较大的不一致,给时序收敛带来困难。

诞生

DC Ultra继承了Physical Compiler的物理综合技术,推出了拓扑模式(它也被称为DC-T),只需要在启动Design Compiler时添加-topographical_mode选项,并在综合时使用compile_ultra命令即可。

在拓扑模式下,Design Compiler在综合时会对标准单元进行粗布局(Coarse Placement),粗布局指的是标准单元的摆放并不会严格按照Site Row对齐,且标准单元之间可能会有重叠,因为这对于提取互连RC而言已经足够了。

在拓扑模式下,Design Compiler使用虚拟布线(Virtual Routing)技术,通过标准单元引脚间的曼哈顿距离计算连线长度,并配合工艺文件(.tf)或TLUPlus文件中的RC模型得到RC参数,最终使用Elmore模型计算互连延迟并进行反标。

进化

DC Graphical在继承DC Ultra拓扑技术的同时推出了布线拥塞(Congestion)分析(它也被称为DC-G),在综合完成后使用report_congestion命令即可进行基于Zroute的全局布线(Global Routing),它与布局布线工具(比如IC Compiler)中拥塞分析工具是一样的,比虚拟布线更加精确,因为此时所有互连已经被分配到各个金属层了。

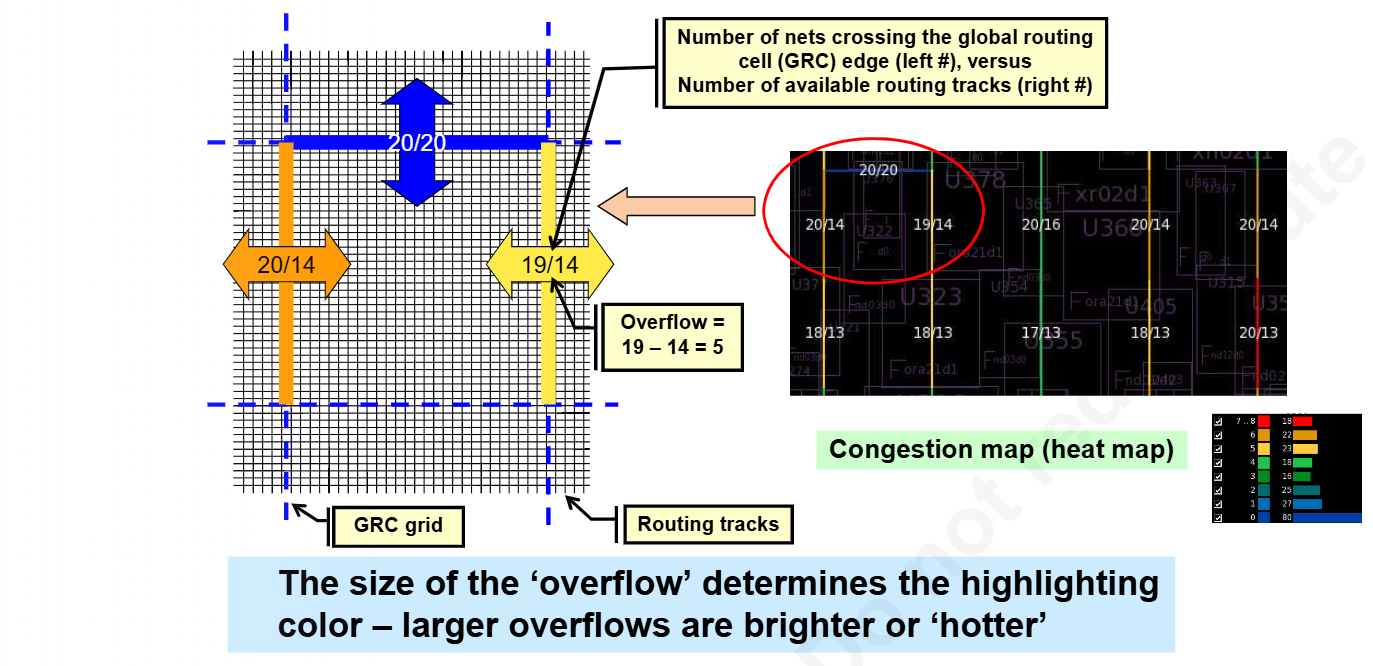

在布线拥塞分析时,核心布局区域将被分为一些网格,它们被称为全局布线单元(Global Routing Cell),全局布线单元的每条边都有可用布线轨道数,它是由工艺文件中每层的layer pitch计算出的。分析产生的拥塞热图中会显示穿过全局布线单元每条边的连线数(左)和该边的可用轨道数(右),如图1所示。

图1 GRC单元

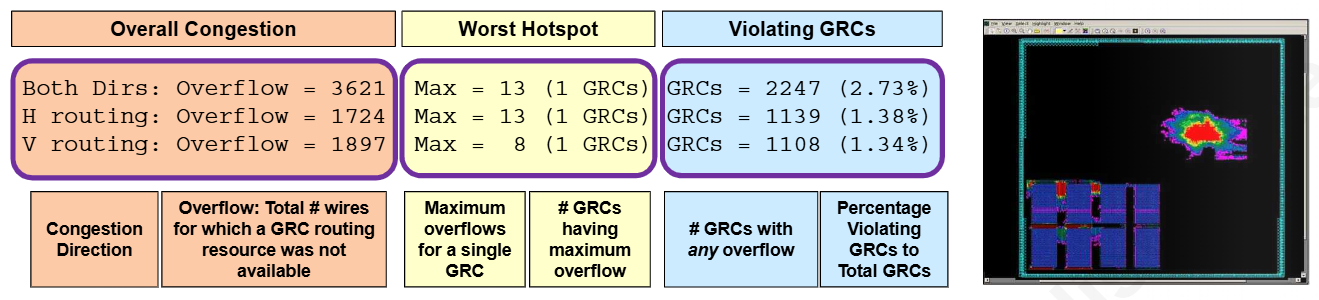

文本格式的拥塞报告会显示每个方向上溢出的边数、最多溢出的GRC单元数和有溢出的GRC单元数和比例,如图2所示。

图2 文本形式的拥塞报告

DC Graphical引入的Synopsys Physical Guidance技术,还允许在综合时就进行拥塞感知(Congestion-aware)单元布局,与在IC Compiler中的place_opt命令效果一样,只需要在综合时使用compile_ultra -spg命令即可。

对于高度拥塞的设计,还可以通过控制placer_enable_enhanced_router和placer_congestion_effort变量,使用基于基于Zroute的拥塞感知单元布局,这比默认的基于虚拟布线的拥塞估计器更加准确。

要求

如果需要使用拓扑技术,需要以下文件:

- 逻辑库(.db):这与逻辑综合时的要求一致。

- 物理库:Milkyway库或者NDM库(DC NXT引入的新格式),其中包括了标准单元和宏单元的形状图(Frame)。注意:老版的.pdb格式的物理库已经被抛弃了。

- 技术文件(.tf):每个工艺制成有专门的技术文件说明其工艺参数,其中包括了金属层的信息,比如层名、层编号、层线宽和简单的RC模型等。

- TLUPlus文件(.tluplus):该文件模拟了超深亚微米(UDSM)的影响,并提供了更先进的TLUPlus模型(比技术文件中的简单RC模型更先进)用于参数提取,它可以使用StarRC的grdgenxo命令从互连技术文件(ITF文件)编译而来(在半导体厂商没有直接提供TLUPlus文件时,需要用户进行ITF to TLUPlus的转换。该文件不是必须的,但强烈建议使用。

- 映射文件(.map):该文件用于将TLUPlus文件和技术文件之间的层名进行映射。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?