相关阅读

静态时序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

时钟共同悲观路径

时钟共同悲观路径指的是发射路径和捕获路径有一段共同的时钟路径,然而在进行时序分析时,这段路径却因为片上变化(On Chip Variation, OCV)的设置而使用了不同的延迟值。这类设置包括使用set_operating_conditions命令设置了on_chip_variation模式和使用set_timing_derate命令设置时序降额。

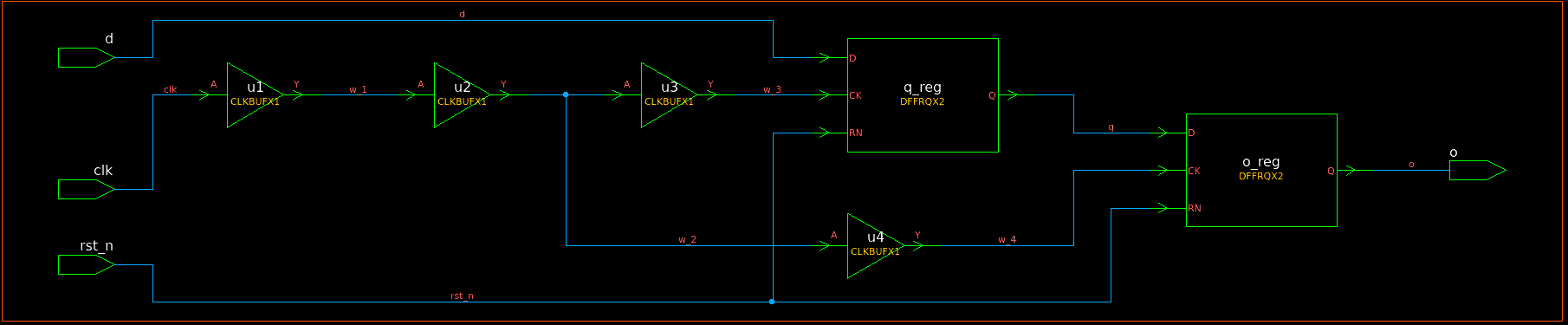

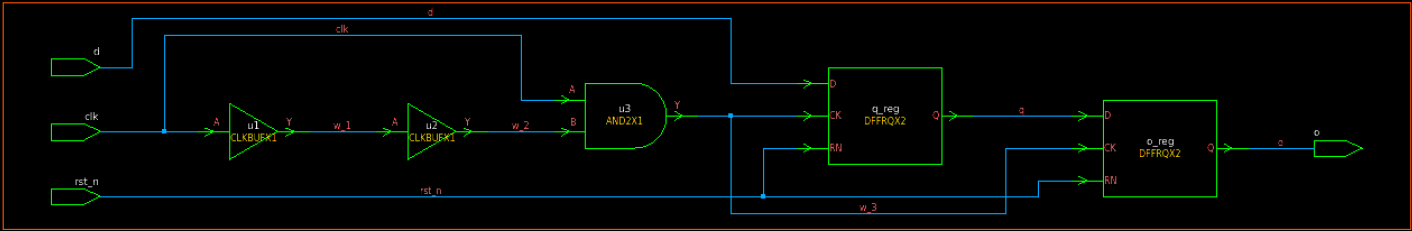

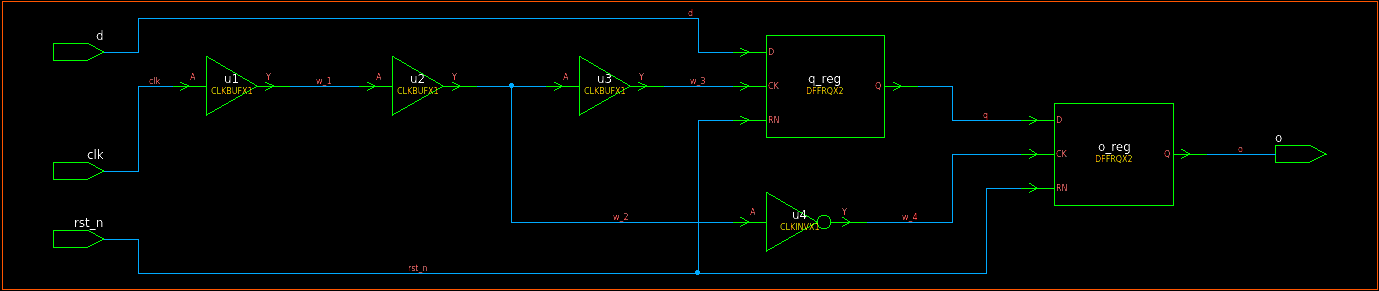

下面以图1为例进行说明时钟共同悲观路径的影响(仅展示on_chip_variation模式下的共同悲观路径)。

图1 时钟共同悲观路径

首先使用create_clock命令以clk端口为源对象创建一个周期为10的时钟。

create_clock -period 10 [get_port clk]随后将其设置为传播时钟(这很重要,因为理想时钟不会考虑共同悲观路径,这也意味着只有做完时钟树综合(Clock Tree Synthesis, CTS)后才会存在共同悲观路径)。

set_propagated_clock [get_clock clk]接着在时钟输入端口分别设置最大条件下和最小条件下的转换时间。

set_input_transition -min 0.1 [get_port clk]

set_input_transition -max 0.8 [get_port clk]最后使用set_operating_conditions命令设置分析模式为on_chip_variation,关于该命令的使用,可以看下面的博客。

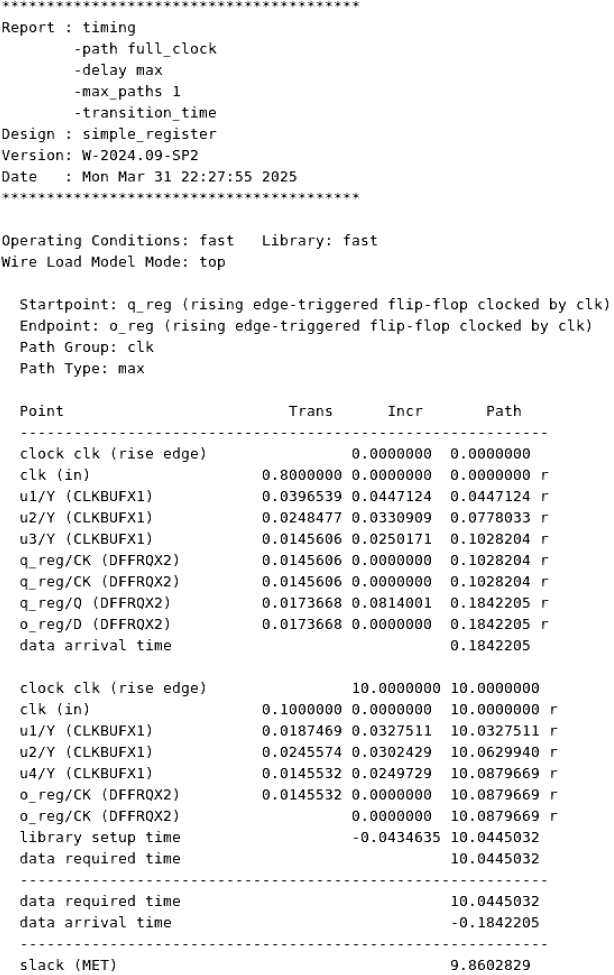

set_operating_conditions -analysis_type on_chip_variation fastSDC命令详解:使用set_operating_conditions命令进行约束(bc_wc模式和on_chip_variation模式)![]() https://blog.csdn.net/weixin_45791458/article/details/146458759?spm=1001.2014.3001.5501 此时的寄存器间时序报告如图2所示,注意使用-full_clock选项和-transition_time以报告完整的时序路径和转换时间。

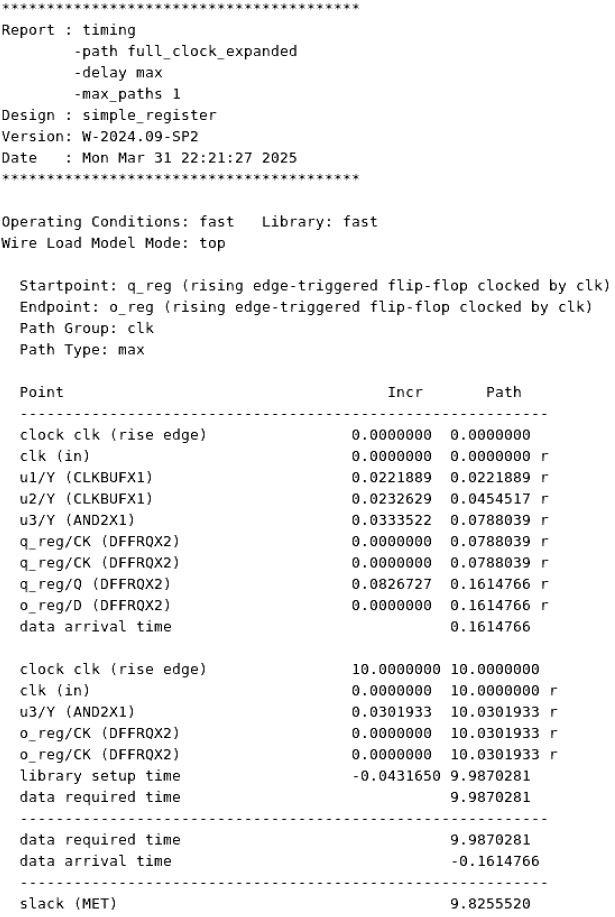

https://blog.csdn.net/weixin_45791458/article/details/146458759?spm=1001.2014.3001.5501 此时的寄存器间时序报告如图2所示,注意使用-full_clock选项和-transition_time以报告完整的时序路径和转换时间。

图2 寄存器间时序报告

可以看出,发射路径和捕获路径的起始转换时间分别是0.8和0.1,导致共同路径上的u1和u2单元的延迟不同,这是过于悲观的,如果想要移除这种悲观,可以将timing_remove_clock_reconvergence_pessimism变量设置为true(对于Design Compiler默认是false,对于PrimeTime默认是True)。

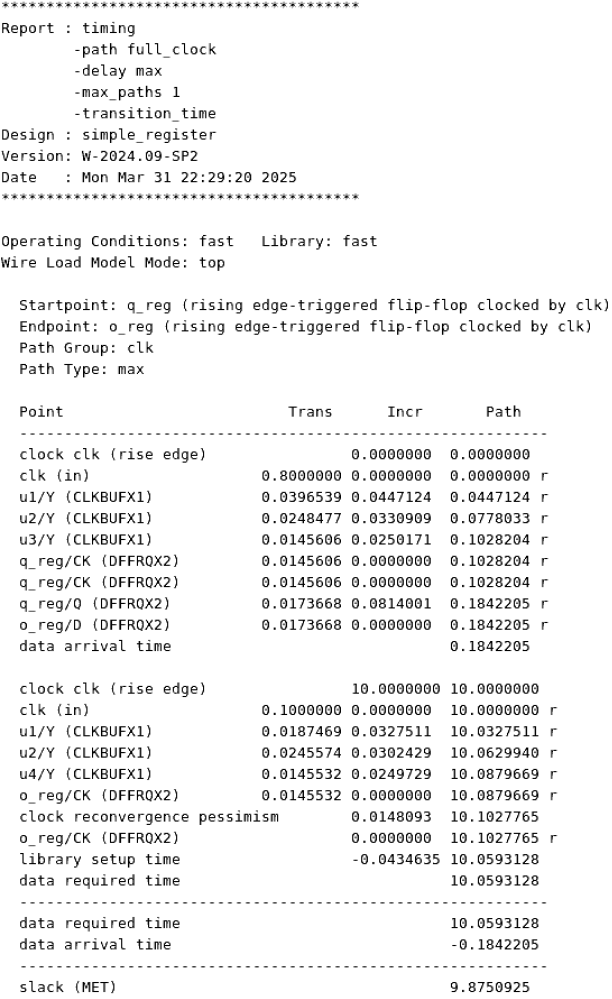

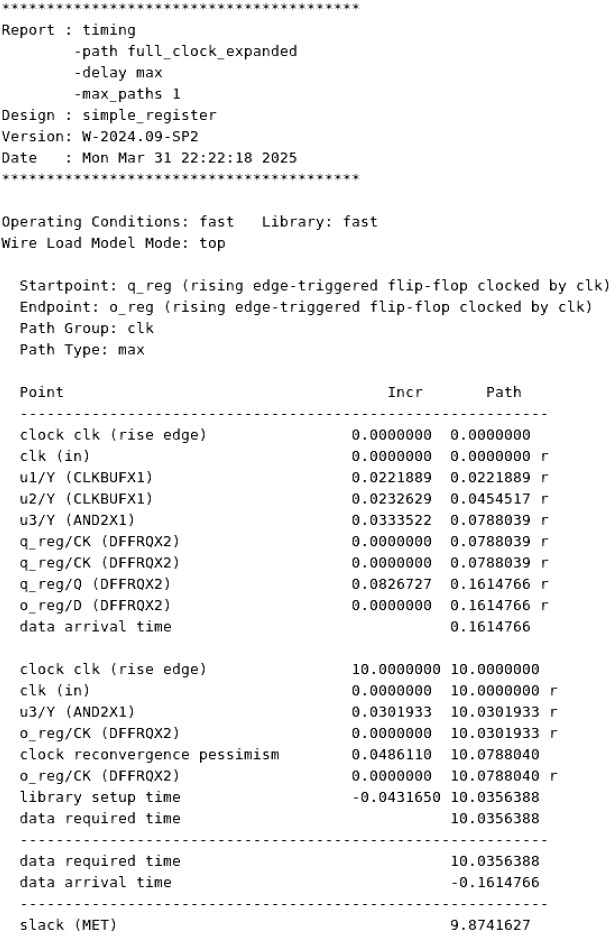

set_app_var timing_remove_clock_reconvergence_pessimism true图3是移除了悲观路径后的时序报告,可以看出此时以clock reconvergence pessimism项标出了悲观值并使最后的裕量增加了。

图3 寄存器间时序报告(移除共同悲观路径)

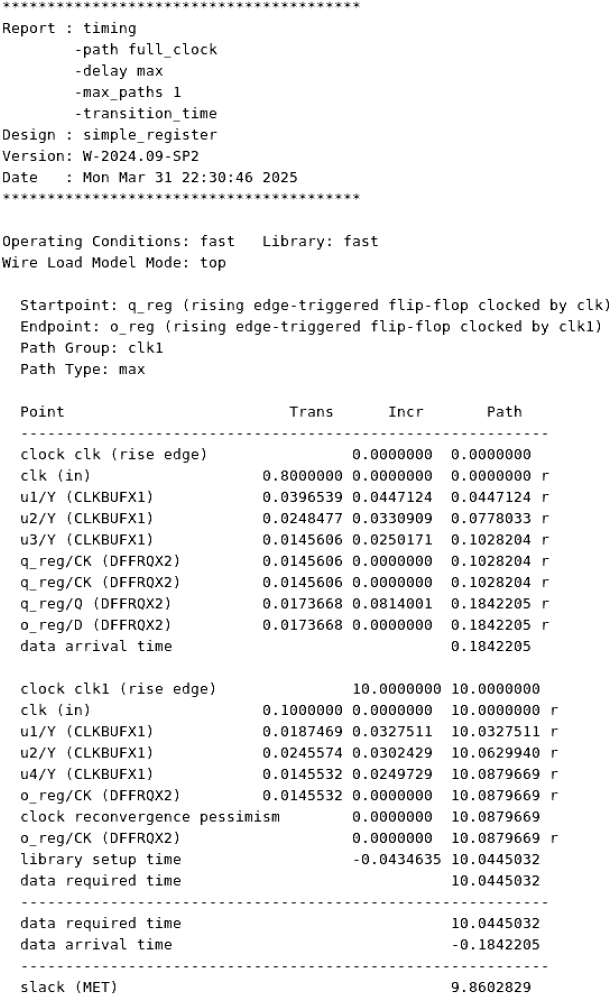

两个不同的时钟即使有一段共同的时钟路径,也不会考虑它们之间的悲观路径,如图4所示。

图4 寄存器间时序报告(不考虑共同悲观路径)

时钟重汇聚悲观路径

有些时候即使不考虑片上变化,也会出现额外的悲观值,时钟重汇聚悲观路径指的是发射路径和捕获路径有一段时钟路径出现了分离-重汇聚的过程,默认情况下会在最悲观的情况下进行分析,即对于发射路径和捕获路径选择不同的时钟传播路径(即使不开启on_chip_variation模式)。

下面以图5为例进行说明时钟共同悲观路径的影响。

图5 时钟路径上的重汇聚

首先使用create_clock命令以clk端口为源对象创建一个周期为10的时钟。

create_clock -period 10 [get_port clk]随后将其设置为传播时钟(这很重要,因为理想时钟不会考虑重汇聚悲观路径,这也意味着只有做完时钟树综合(Clock Tree Synthesis, CTS)后才会存在重汇聚悲观路径)。

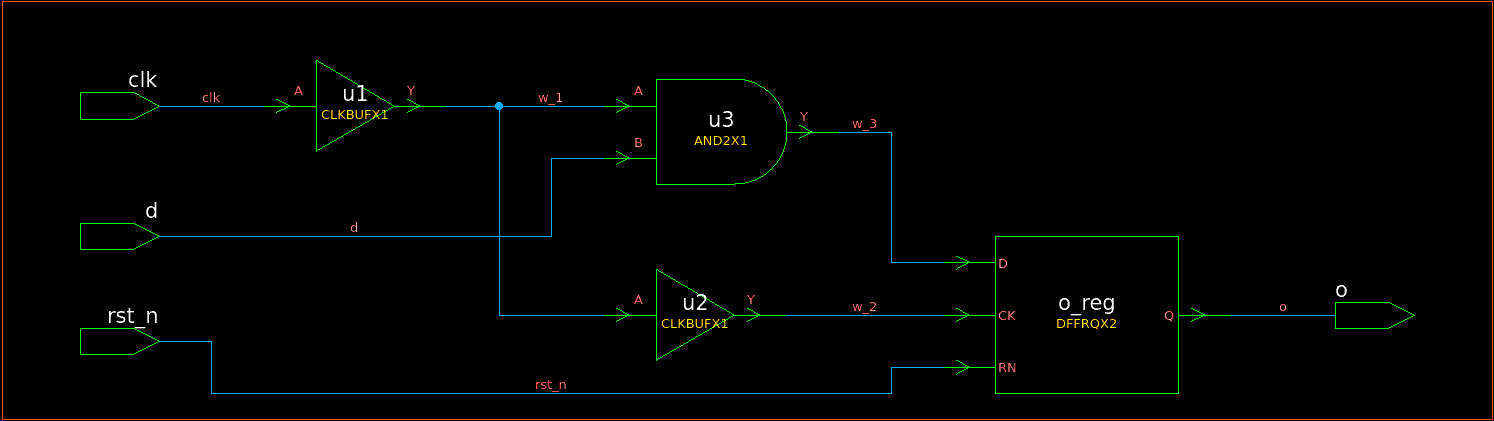

set_propagated_clock [get_clock clk]此时的寄存器间时序报告如图6所示,注意使用-full_clock选项以报告完整的时序路径。

图6 寄存器间时序报告

可以看出,发射路径的时钟路径经过了三个单元而捕获路径的时钟路径则只经过了一个单元(对于保持时间检查来说情况相反),这是过于悲观的,如果想要移除这种悲观,可以将timing_remove_clock_reconvergence_pessimism变量设置为true(对于Design Compiler默认是false,对于PrimeTime默认是True)。

set_app_var timing_remove_clock_reconvergence_pessimism true图7是移除了悲观路径后的时序报告,可以看出此时以clock reconvergence pessimism项标出了悲观值并使最后的裕量增加了。

图7 寄存器间时序报告(移除重汇聚悲观路径)

最后顺带一提,如果时钟重汇聚悲观路径和时钟共同悲观路径同时存在,则会同时考虑这两种悲观情况。

其他的控制变量

timing_crpr_threshold_ps变量

该变量指定允许悲观移除在报告中留下的悲观量,单位为ps,默认值为5ps,允许的最小值为2e-5ps。如果悲观移除未启用,则此变量没有影响,该变量的值越大,运行悲观移除时越快。

推荐的设置是时钟网络中的典型门(包括门和网)半延迟,这适用于大多数情况下的精度和运行时间之间的合理折衷。

在设计周期中,可能会使用不同的设置:设计阶段使用较大的值,签核阶段使用较小的值。

timing_crpr_remove_clock_to_data_crp变量

该变量指定是否允许悲观移除时考虑作为数据使用的时钟,如图8所示,默认值为false。

图8 作为数据使用的时钟

严格意义上说,这并不是时钟路径的悲观,因为发射路径(即通过u1和u3单元的路径)此时被认为是数据路径而不是时钟路径,捕获路径(即通过u1和u2单元的路径)与发射路径拥有共同的u1单元。

需要注意的是,由于该行为会导致单独分析每一个时钟到数据路径,因此可能在时序更新期间造成严重的性能损失。

timing_clock_reconvergence_pessimism变量

这个变量决定了如何计算时钟悲观路径去除的值,允许的值为normal(默认值)和same_transition。

当设置为normal时,即使时钟在共同时钟路径上的转换方向不同(比如时钟路径上有极性反转或者触发器的触发方式不同)也会计算悲观值,此时将对上升和下降沿分别计算悲观路径,并使用绝对值较小的结果。

当设置为same_transition时,只有当时钟在共同时钟路径上每一个引脚的的转换方向都相同时,才会计算悲观值。

图9 发射触发器和捕获触发器由时钟的不同沿触发

对于图9所示的例子,如果设置为normal,则还是会计算共同悲观路径(u1和u2单元),即使发射路径和捕获路径在这两个单元上的转换方向不同(假设触发器都是上升沿触发的);如果设置为same_transition,则不会计算共同悲观路径。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?