相关阅读

Spyglass![]() https://blog.csdn.net/weixin_45791458/category_12828934.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12828934.html?spm=1001.2014.3001.5482

本文是对Spyglass Hands-on Training中第一个实验的翻译(有删改),Lab文件可以从以下链接获取。Spyglass Hands-on Training![]() https://download.csdn.net/download/qq_43699362/85585058?ops_request_misc=%257B%2522request%255Fid%2522%253A%25225fb1922ab549e363d5c551d14bebd31a%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fdownload.%2522%257D&request_id=5fb1922ab549e363d5c551d14bebd31a&biz_id=1&utm_medium=distribute.pc_search_result.none-task-download-2~download~first_rank_ecpm_v1~rank_v31_ecpm-30-85585058-null-null.269^v2^control&utm_term=Spyglass%20Get%20Start&spm=1018.2226.3001.4451.31

https://download.csdn.net/download/qq_43699362/85585058?ops_request_misc=%257B%2522request%255Fid%2522%253A%25225fb1922ab549e363d5c551d14bebd31a%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fdownload.%2522%257D&request_id=5fb1922ab549e363d5c551d14bebd31a&biz_id=1&utm_medium=distribute.pc_search_result.none-task-download-2~download~first_rank_ecpm_v1~rank_v31_ecpm-30-85585058-null-null.269^v2^control&utm_term=Spyglass%20Get%20Start&spm=1018.2226.3001.4451.31

本教程提供了在多个设计阶段中运行SpyGlass的操作指导,旨在通过实操获得对SpyGlass设置及其结果调试/分析的深入理解,涵盖多个动手练习,每个练习之间是相互依赖的,需要按顺序完成。

实验概述

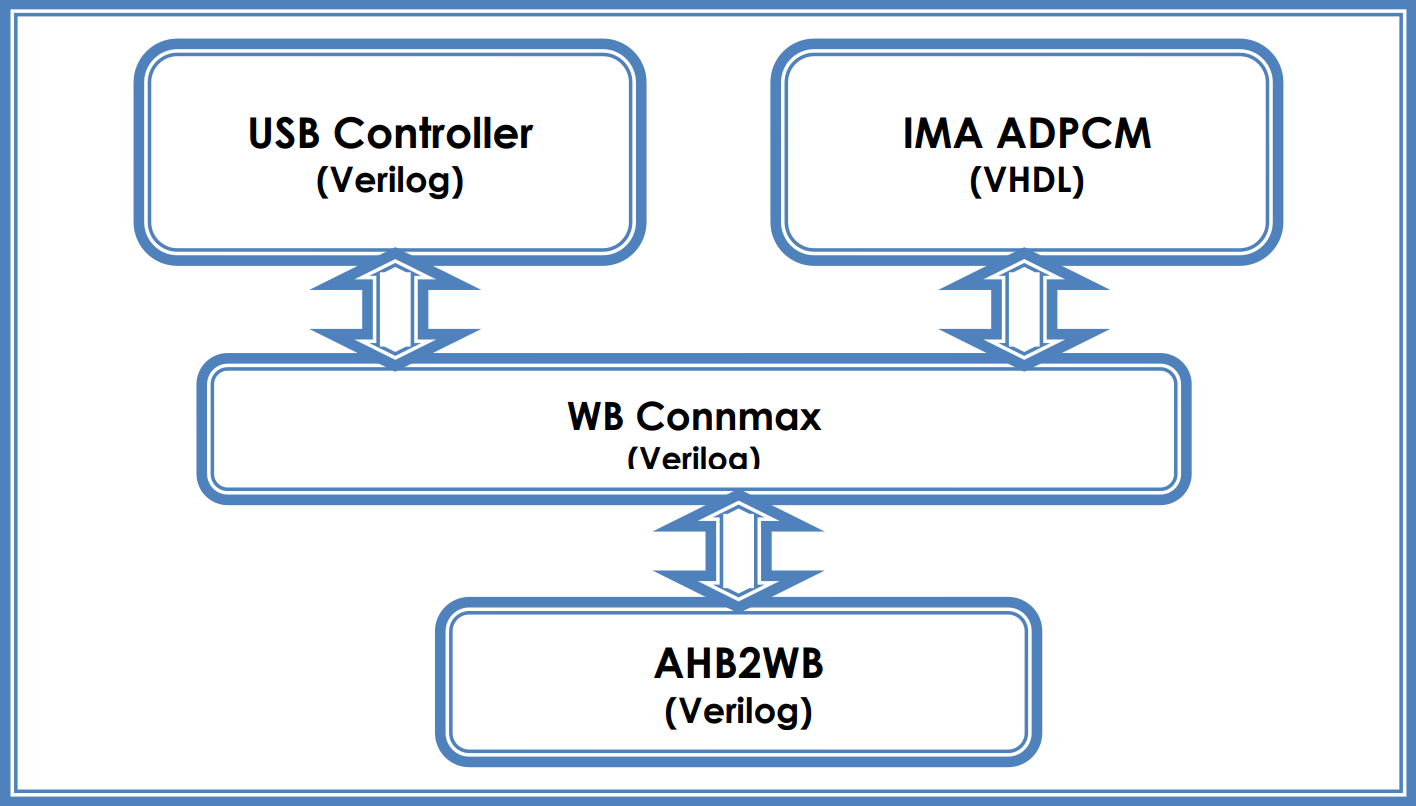

图1展示了实验使用设计的模块框图。该设计包含一个USB控制器和一个音频解码器核心(IMA_ADPCM),使用Wishbone总线协议,这些模块通过Wishbone总线矩阵(WB_Connmax)相互连接,然后再通过Wishbone-to-AHB桥接模块(wb2ahb)连接至AMBA AHB总线。顺带一提,该设计是一个混合语言RTL设计,即同时使用Verilog和VHDL。

图1 设计框图

实验目录的内容

教程目录包含以下子目录:

- rtl:与设计相关的RTL文件

- spyglass:实验的工作目录,所有SpyGlass的运行将在该目录下进行

- doc:包含实验文档(即本手册)

- tools:实验中会使用到的其他脚本

实验一、Spyglass概述

实验一的目标是快速开始使用SpyGlass,在其中运行分析并查看结果。由于该案例将用于后续的多个实验,建议将实验一创建的项目文件保存以供以后使用。

实验一中,为了简便使用图形用户界面(GUI)创建一个项目文件作为起点,之后的实验将继续使用该项目文件以批处理方式(Batch)进行操作。

将设计读入SpyGlass

1、进入名为spyglass的目录。

% cd Training_labs/spyglass2、使用以下命令启动SpyGlass图形界面(SpyGlass Explorer):

% spyglass由于Spyglass是Synopsys收购自Atrenta,最初使用的GUI是Atrenta Console,但目前已经被新的SpyGlass Explorer替代,不再进行任何更新。感兴趣的读者可以通过添加-gui=console选项启动Atrenta Console。

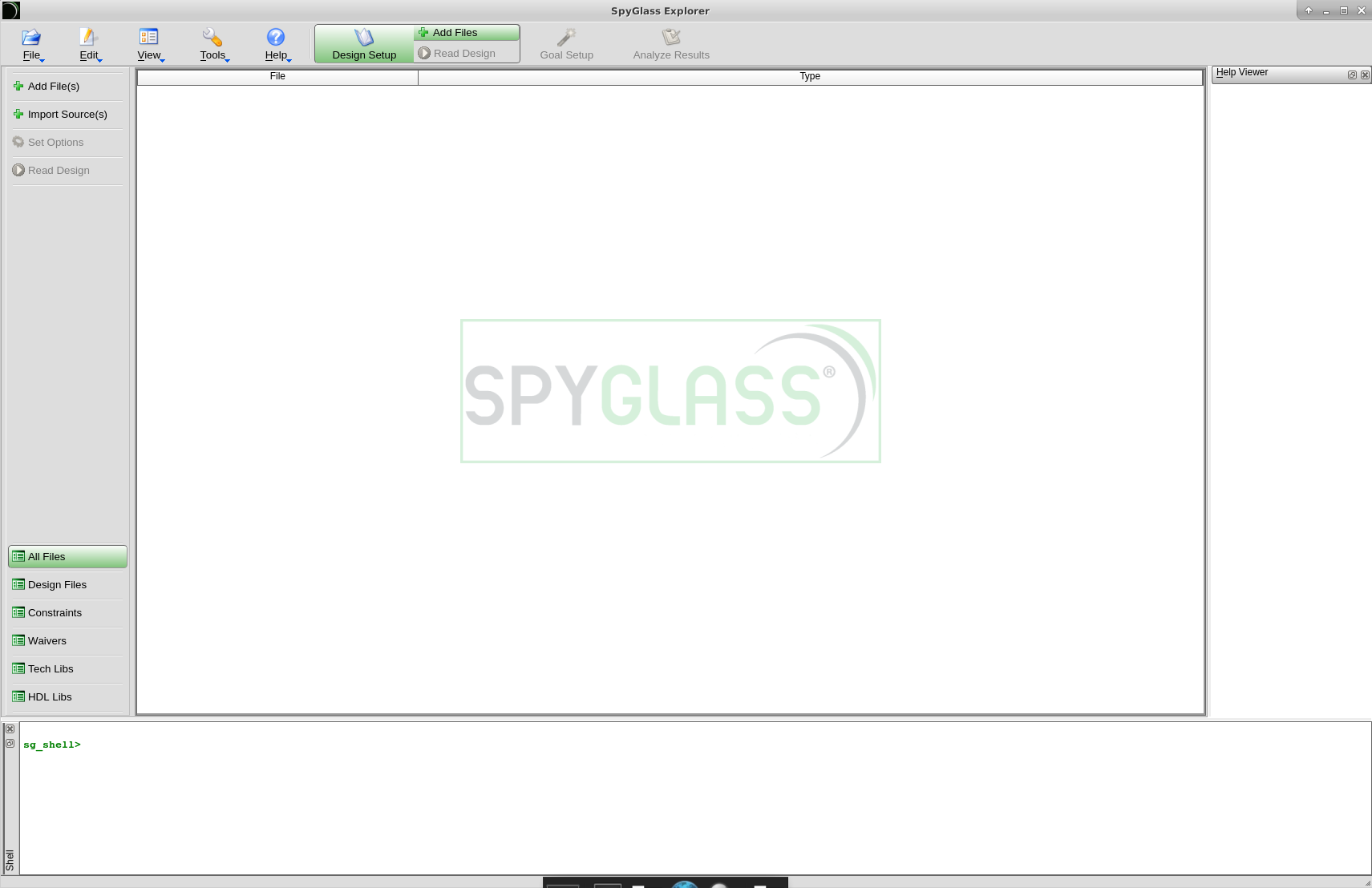

3、此时你将看到以下的主界面窗口:

图1 SpyGlass Explorer

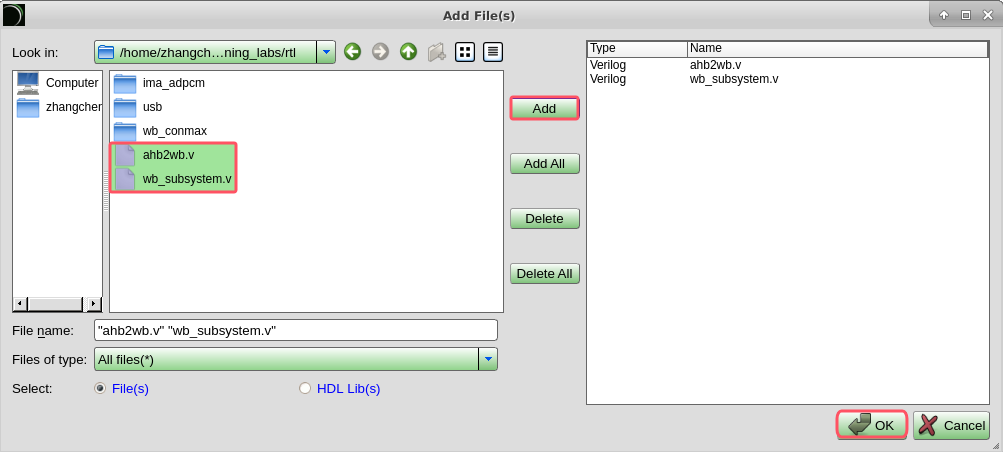

4、点击窗口左栏的Add File(s),打开名为Add File(s)的窗口,在该窗口中添加以下来自rtl目录的两个RTL文件,如图2所示。

rtl/ahb2wb.v

rtl/wb_subsystem.v

图2 Add File(s)窗口

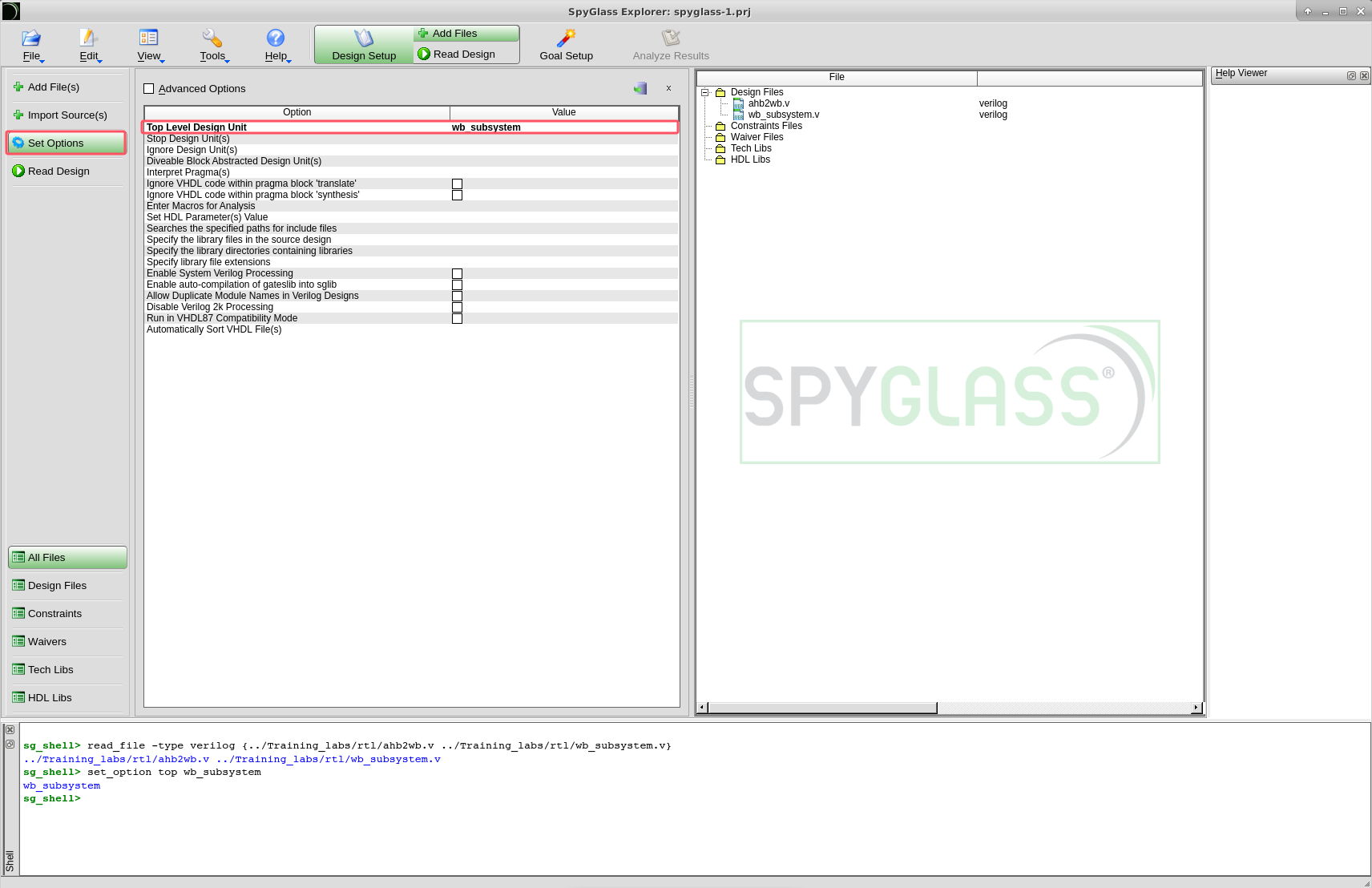

5、接着点击窗口左栏的Set Options,然后设置顶层设计模块为"wb_subsystem",如图3所示。

图3 设置顶层模块

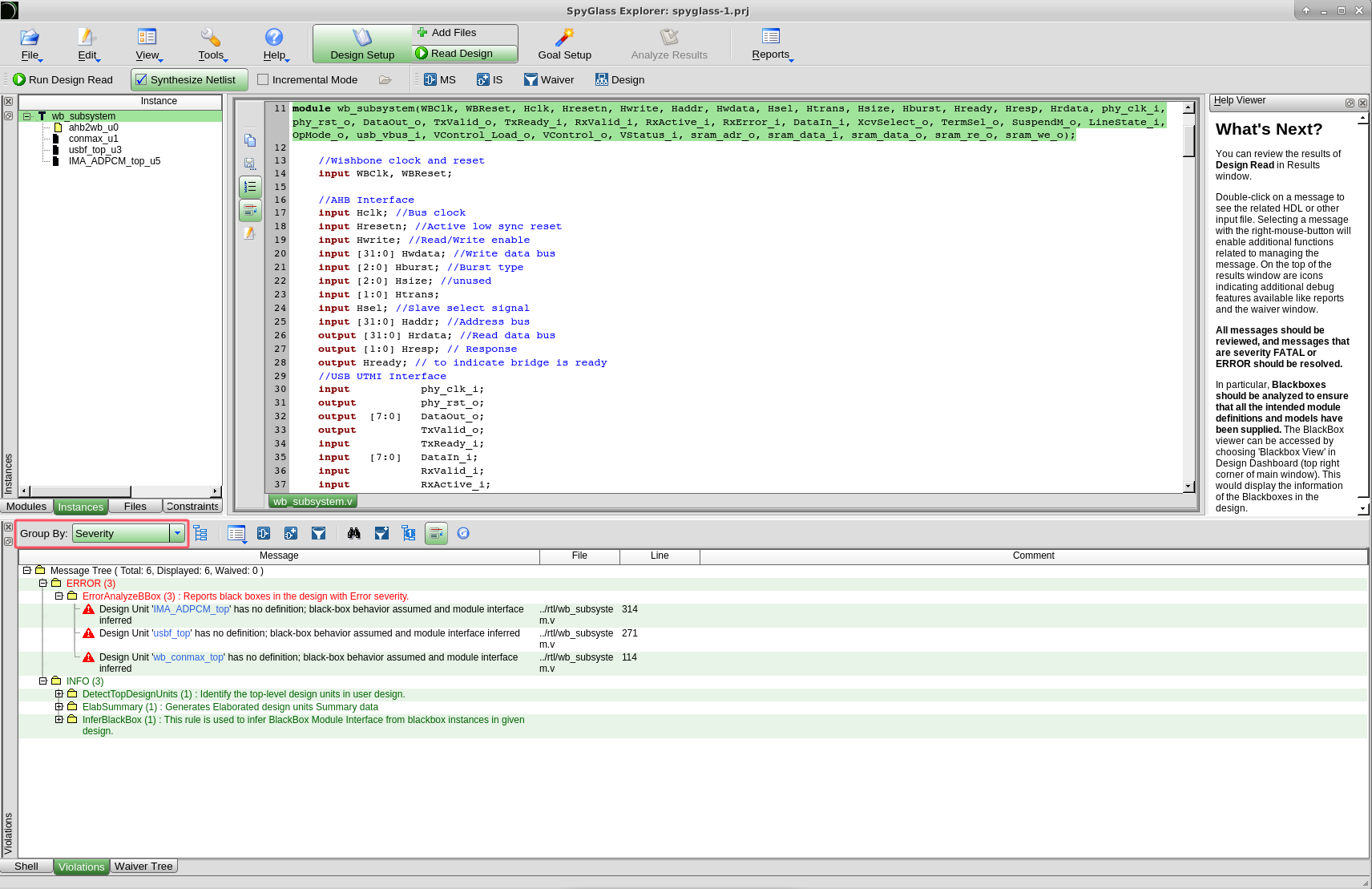

6、现在选择Design Setup阶段下的Read Design,勾选Synthesize Netlist选项框并点击Run Design Read以启动设计读取(这其实是启动了一个名为Design_Read的目标)。一旦运行完成,就可以查看SpyGlass报告的设计读取错误,如图4所示。

图4 Design_Read的结果

注意图4在Violations窗口选择Group By Severity,可以看出有三个来自ErrorAnalyzeBBox规则的错误,SpyGlass没有找到这些模块的定义,因此将其标记为黑盒(black box)。

左边的实例窗口(Instances)使用不同颜色的文件形状标记状态:

- 黄色:已综合的最底层实例。

- 黑色:黑盒实例。

- 绿色:未综合的最底层实例。

使用SpyGlass进行分析

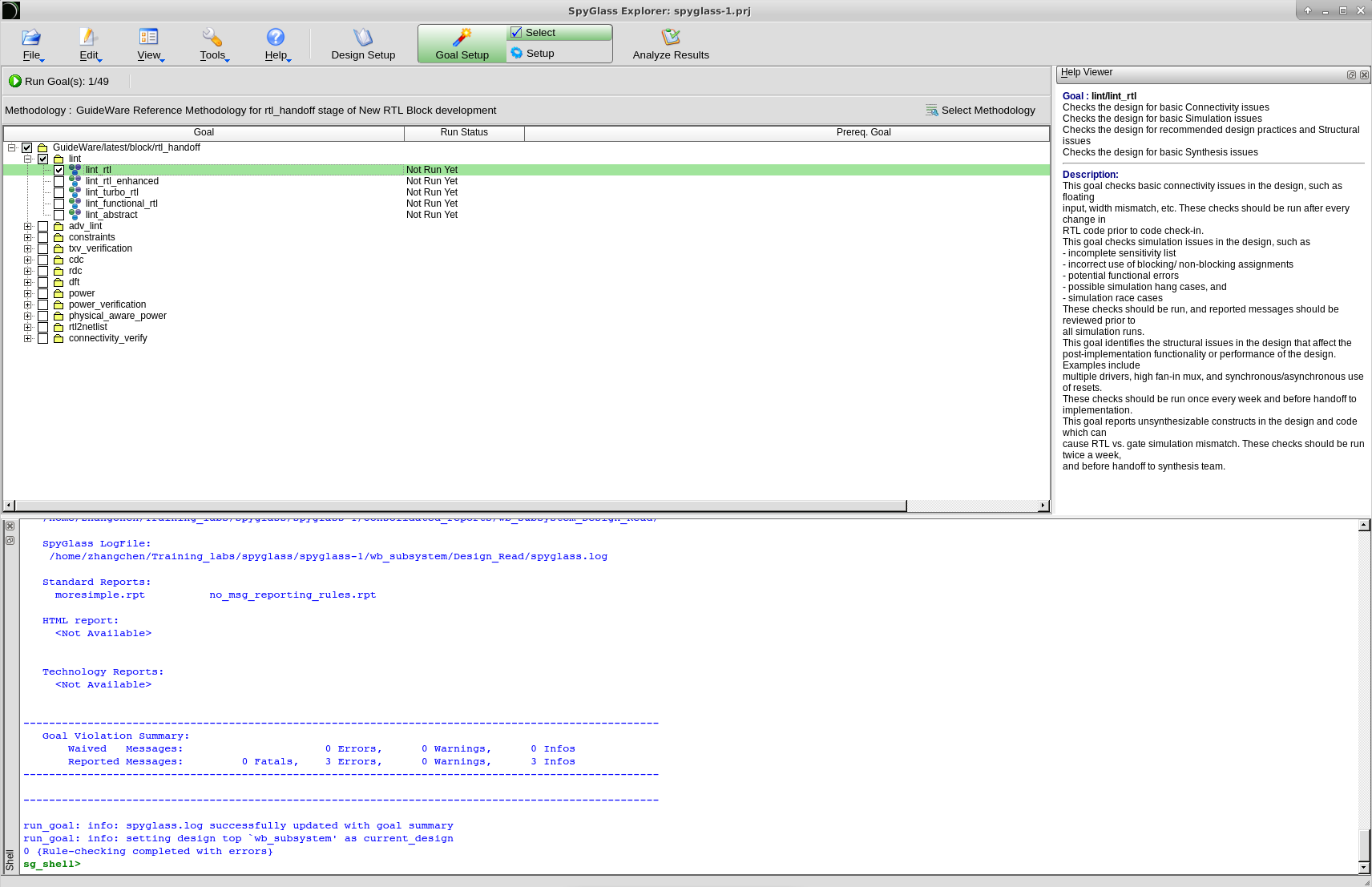

1、选择Goal Setup阶段,并点击lint_rtl目标,使其绿色高亮,所选目标的用途可以在右边的Help窗口中查看,用于检查设计中的基本连接性问题,例如输入悬空、位宽不匹配等,如图5所示。为了简便,实验一只勾选这一个目标,如果有多个目标被勾选,它们将会顺序执行(顺带一提,lint_rtl目标是来自/Guideware/latest/block/rtl_handoff方法的lint子方法,Guideware是Spyglass提供的一些预设的检查参考)。

图5 选择目标

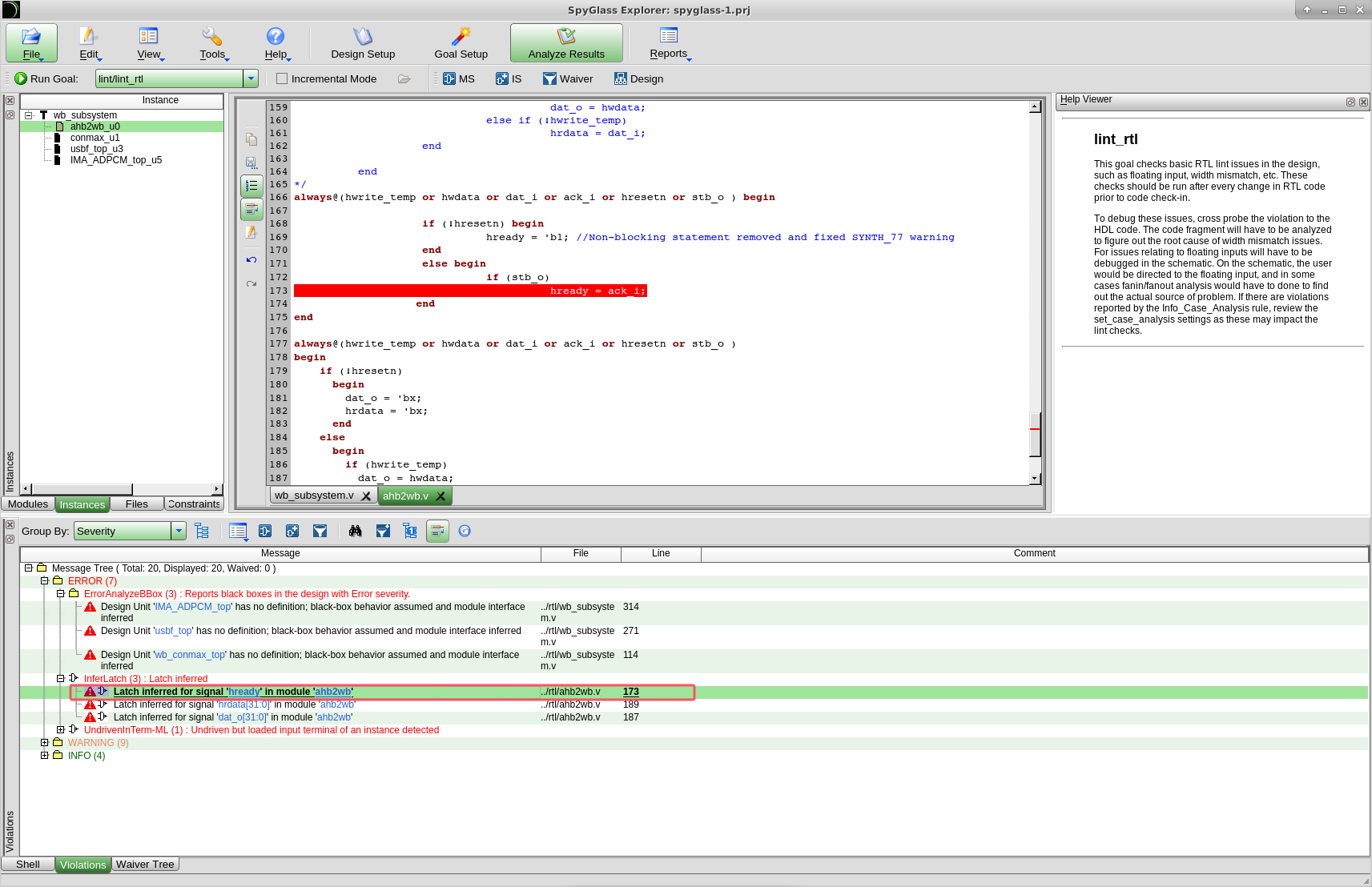

2、点击Run Goal(s),一旦运行完成,工具将自动跳转至Analyze Results阶段,还是在Violations窗口选择Group By Severity,可以看出除了之前的三个来自ErrorAnalyzeBBox规则的错误,多了三个InferLatch规则的错误,双击选中第一个规则,相关的RTL代码行将在上方的HDL查看器中被红色高亮显示,如图6所示。

图6 Lint的结果

可以看出RTL代码中包含了不完整的if语句,这确实是导致Latch产生的原因,同时注意到三个InferLatch规则的左边有NAND门符号,这代表可以查看用于调试的原理图。可以使用快捷键I或者点击Violations窗口上的![]() 符号查看原理图,如图7所示。

符号查看原理图,如图7所示。

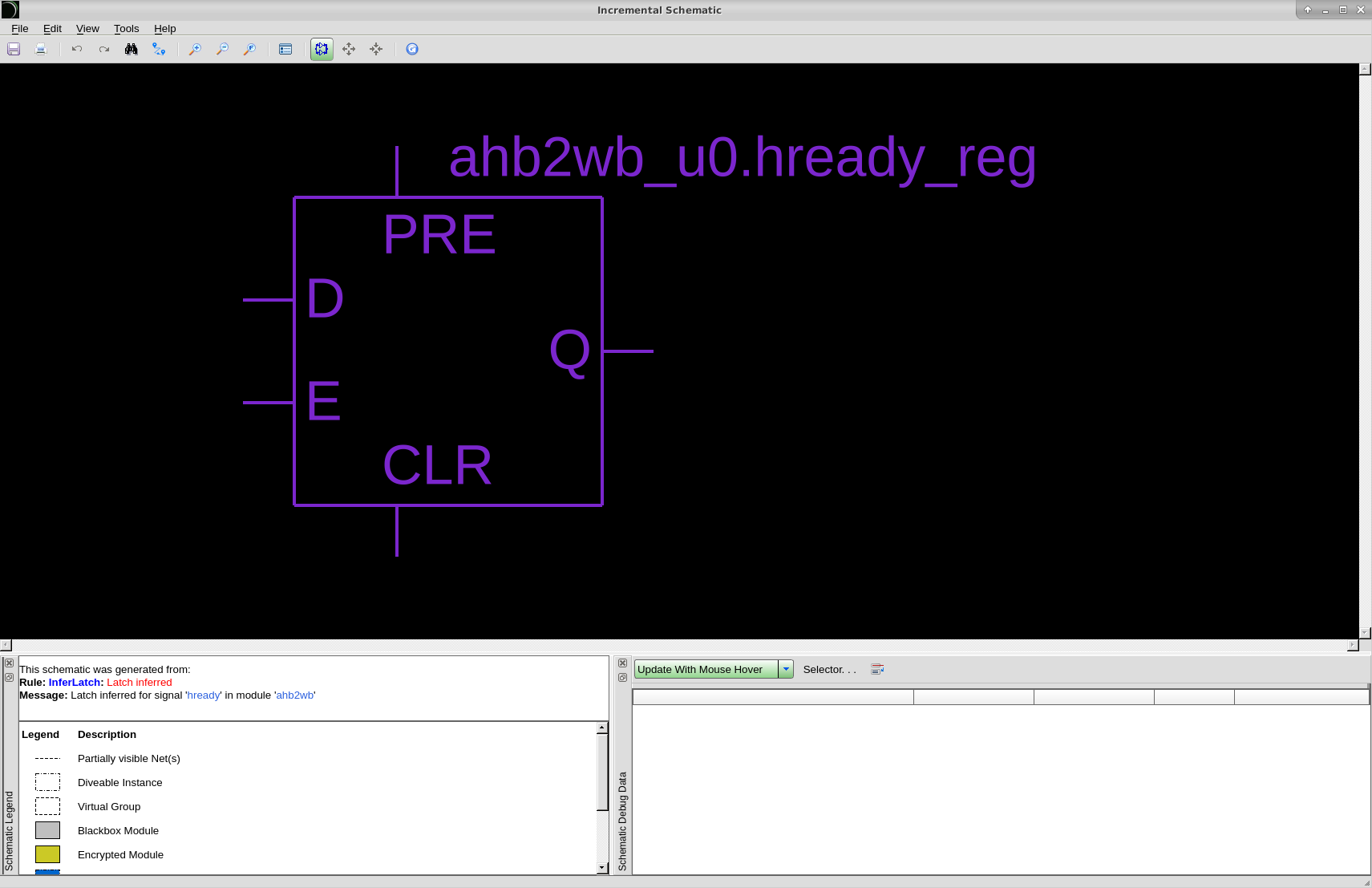

图7 原理图

可以看出hready信号综合成了一个锁存器,如果设计意图就是需要hready信号相对于选通信号stb_o被锁存,那么可以该规则进行豁免(waive);如果确实需要修复该问题,可以点击RTL代码行,并按下键盘上的快捷键e(或右键选择Open Editor选项),Spyglass会使用默认文本编辑器(Vim)打开RTL文件并将光标定位到该行,如果想更改默认文本编辑器,可以看下面的博客。

Spyglass:更改默认编辑器![]() https://chenzhang.blog.csdn.net/article/details/143947206

https://chenzhang.blog.csdn.net/article/details/143947206

3、保存项目文件,点击File选项栏下的Save Project,然后输入wb_subsystem作为文件名),并退出。

4、使用文本编辑器打开项目文件wb_subsystem.prj,如下所示。

#!SPYGLASS_PROJECT_FILE

#!VERSION 3.0

# -------------------------------------------------------------------

# This is a software generated project file. Manual edits to this file could be lost during the next save operation

# Copyright Synopsys Inc.

# Last Updated By: SpyGlass SpyGlass_vW-2024.09-SP1

# Last Updated On Wed Apr 30 17:35:59 2025

#

# -------------------------------------------------------------------

##Data Import Section

read_file -type verilog ../rtl/ahb2wb.v

#BackRefFile:/home/zhangchen/Training_labs/spyglass/wb_subsystem.prj #LineNumber:13

read_file -type verilog ../rtl/wb_subsystem.v

#BackRefFile:/home/zhangchen/Training_labs/spyglass/wb_subsystem.prj #LineNumber:15

##Common Options Section

set_option projectwdir .

set_option language_mode mixed

set_option designread_enable_synthesis yes

set_option designread_disable_flatten no

set_option top wb_subsystem

set_option active_methodology $SPYGLASS_HOME/GuideWare/latest/block/rtl_handoff

##Goal Setup Section

current_methodology $SPYGLASS_HOME/GuideWare/latest/block/rtl_handoff可以看出,其中的Data Import Section包括了一些文件读取的命令,而Common Options Section包括了工作目录、语言模式、顶层设计和方法的设置。在实验二中,需要继续向项目文件中添加额外的命令和选项。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?