目录

题目来源于众多网友对笔试的记录、回忆。

理解不到位,难免出错,解析仅为个人看法,有不同意见请留言指教,谢谢!

题型:

15个单选+5个多选+4个简答/代码题

单选:

1.如果对一幅(帧)分辨率为VGA。每像素数据位宽为8bit的图像进行直方图统计,对应像素地某个取值的统计结果最多有多少种可能?

A.307200 B.307201 C.256 D.255

解析:C

每像素数据位为8bit,每像素有0-255种可能,因此最多有256种可能。

2.netlist一般通过什么手段进行验证可以保证其与RTL的一致性?

A.形式验证 B.随机验证 C.网表验证 D.RTL验证

解析:A

形式验证是为了验证综合之后的网表文件与rtl设计文件是否一样,采用的工具是formality。

3.对于跨异步时钟域的信号,以下哪个方面一般不需要在功能仿验证时考虑?

A.信号有效是高电平还是低电平 B.信号变化的最小宽度

C.时钟频率 D.时钟的抖动

解析:D

功能仿真是前端要做的,不关心时序,而时钟抖动(clock skew)是后端加入器件库和工艺库

以及时钟树综合之后才会出现的。

4.关于复位,以下说法正确的是()?

A.复位信号的生效必须需要有时钟上升沿 B.芯片中的复位信号需要在同一周期中生效

C.芯片中所有寄存器都必须有复位控制 D.复位设计可以确保寄存器从稳定态开始工作

解析:D

异步复位跟时钟沿没关系,A错;

异步复位同步释放,不是同一周期,B错;

静态配置的寄存器不需要复位,C错;

复位可以保证寄存器从稳定态开始工作,D对。

5.降低NMOS的开启电压VT的方法,下述哪种方法是无效的?

A.增加源漏极的N型掺杂浓度 B.减少氧化层厚度

C.减少衬底的P型掺杂浓度 D.减少沟道长度

解析:C

当栅极接通正电压之后,衬底上的少数载流子聚集到栅极下面,形成导电沟槽,完成NMOS的开启。

因此,C选项应该是增大掺杂浓度,若减少掺杂浓度的话,载流子浓度降低,就需要更大的开启电压。

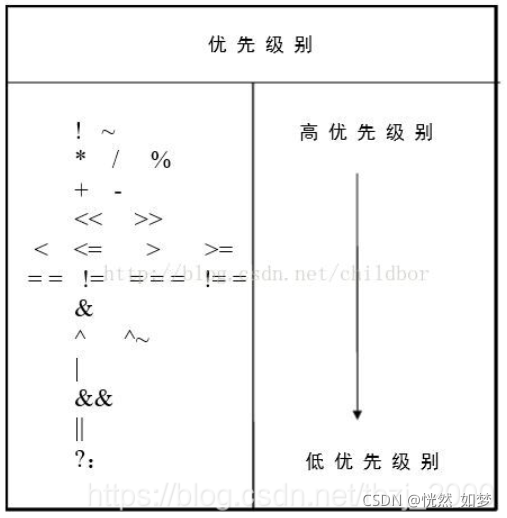

6.以下Verilog运算法优先级由高到低的排序正确的是?

A.^,!,&,|,&& B. &,|,&&,^,!

C. !,|,&,&&,^ D.!,&,^,|,&&

解析:D

运算优先级由高到低:取反 乘除取余 加减 移位 比大小 比相等 位逻辑运算 逻辑运算 三目运算符

7.在RTL设计阶段,降低功耗的常用设计方法是?

A

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?