一、MSP432系列MCU简介

1.1 MSP432系列MCU简介——MSP432特点

MSP432系列使用Cortex -M4F内核具有超低功耗、应用设计方便、扩展性好等特点:

- MSP432系列MCU具有多个低功率操作模式。

- 32位的Cortex -M4F架构,针对小封装的嵌入式应用进行了优化。

- 具有优秀的处理能力与快速中断处理能力。

- 符合IEEE754的浮点运算单元(FPU) 。

- 使用高效的处理器内核、系统和储存器。

- 对时间苛刻的应用提供可确定的、高性能的处理。

- 储存器保护单元为操作系统提供特权操作模式。

- 串行线调试和串行线跟踪减少调试和跟踪过程中需求的引脚数。

- 集成多种休眠模式,使功耗更低。

- 从ARM7处理器系列中移植过来,以获得更好的性能和更高的电源效率。

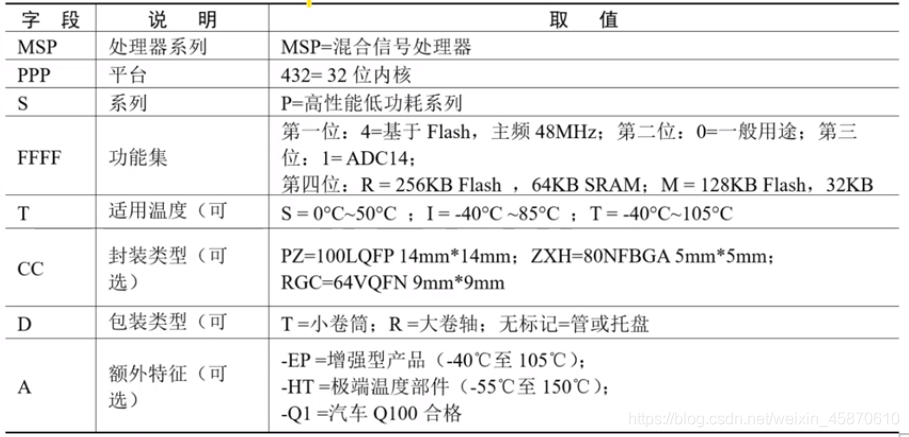

1.2 MSP432系列MCU简介——MSP432系列MCU的的型号标识

MSP432系列命名格式为:MSP PPP S FFFF (T) (CC) (D) (A)

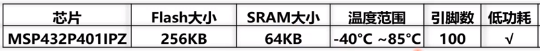

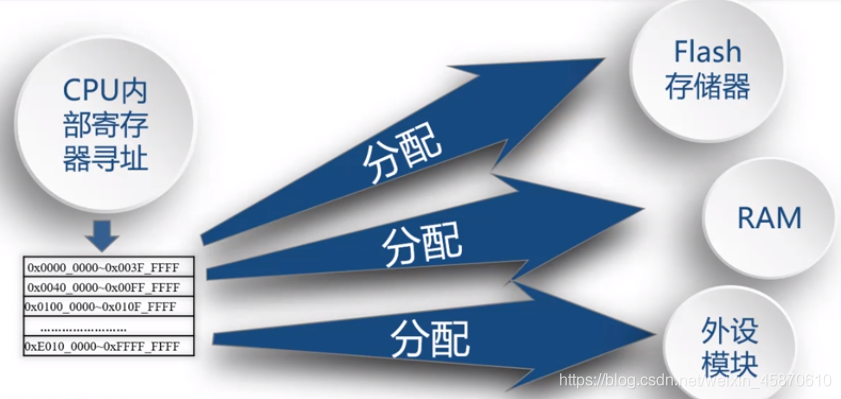

1.3 MSP432系列MCU简介——MSP432系列MCU的简明资源与共同特点

- 内核:低功耗内核(可达nA级)工作频率为48MHz

- 工作电压范围:1.62V~3.7V;

- 运行温度范围:-40C ~ 85C;

- 存储器:Flash大小128KB以上;SRAM大小32KB以上;

- ADC:14位ADC;

- 通信接口:具有UART、12C、SPI的通信接口模块

- 安全特性:具有内部看门狗等安全保护特性;

- 电机控制:具有PWM功能模块;

- 调试接口:具有JTAG和SWD程序写入调试接口等。

1.4 MSP432系列MCU内部结构框图

二、MSP432系列MCU存储映像与中断源

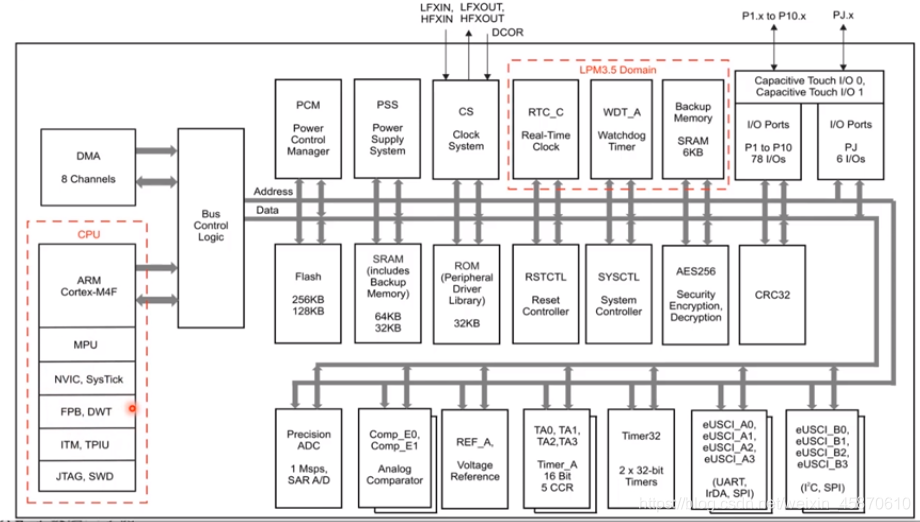

2.1 MSP432系列MCU存储映像与中断源——存储映像

所谓存储映像(Memory Mapping)在这里可以直观地理解为:

Cortex-M4F寻址的4GB地址空间(0x0000_0000~0xFFFF_FFFF)被如何使用的,都对应了些什么实际的物理介质。

MSP432存储映像空间分配如下:

(主要记住片内Flash区及片内RAM区存储映像,其他区域作用了解即可。)

2.2 MSP432系列MCU存储映像与中断源——片内Flash区存储映像

- MSP432片内Flash大小为256KB。

- 地址范围是:0x0000_0000 ~0x0003_FFFF。—般被用来存放中断向量、程序代码、常数等。

- 中断向量表从0x0000_0000地址开始向大地址方向使用。

- 还有16KB的闪存信息存储器,用于引导加载程序(BSL)、标签长度值(TLV)和闪存邮箱。

- MSP432片内RAM为静态随机存储器SRAM,大小为64KB。

- 地址范围是:0x0100_0000~0x0100_FFFF。

- 一般被用来存储全局变量、静态变量、临时变量(堆栈空间)等。

- 中断向量表从0x0000_0000地址开始向大地址方向使用。

- MSP432片内全局变量及静态变量从RAM的最小地址向大地址方向开始使用,堆栈从RAM的最高地址向小地址方向使用,可以减少重叠错误。

2.3 MSP432系列MCU存储映像与中断源——中断源

所谓中断是指:MCU在正常运行程序时,由于MCU内核异常或者MCU各模块发出请求事件,引起MCU停止正在运行的程序,而转去处理异常或执行处理外部事件的程序(又称中断服务程序)。

引起MCU中断的事件称为中断源,分两类:内核中断,非内核中断。

- 内核中断:内核中断主要是异常中断,也就是说,当出现错误的时候,这些中断会复位芯片或是做出其他处理。CPU异常模型以固定和可配置的优先级顺序处理各种异常。

- 非内核中断:非内核中断是指MCU各个模块被中断源引起的中断,MCU执行完中断服务程序后,又回到刚才正在执行的程序,从停止的位置继续执行后续的指令。非内核中断又称可屏蔽中断,这类中断可以通过编程控制,开启或关闭该中断。

2.4 MSP432系列MCU存储映像与中断源——中断向量

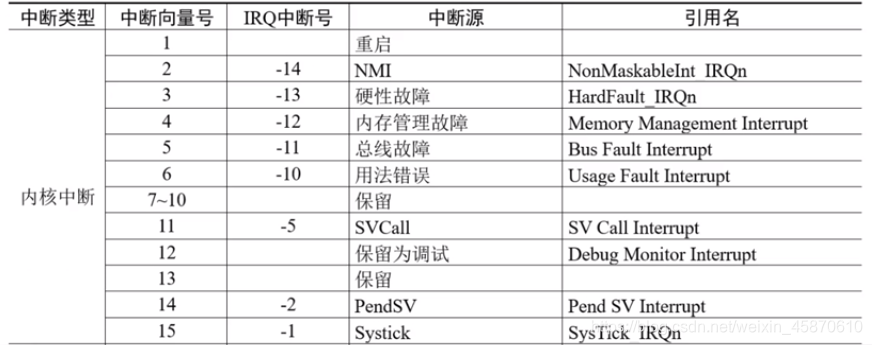

所谓中断向量序号是每一个中断源的固定编号,由芯片设计生产时决定的,编程时不能更改,它代表了中断服务程序入口地址在中断向量表的位置。如下是MSP432内核中断向量表:

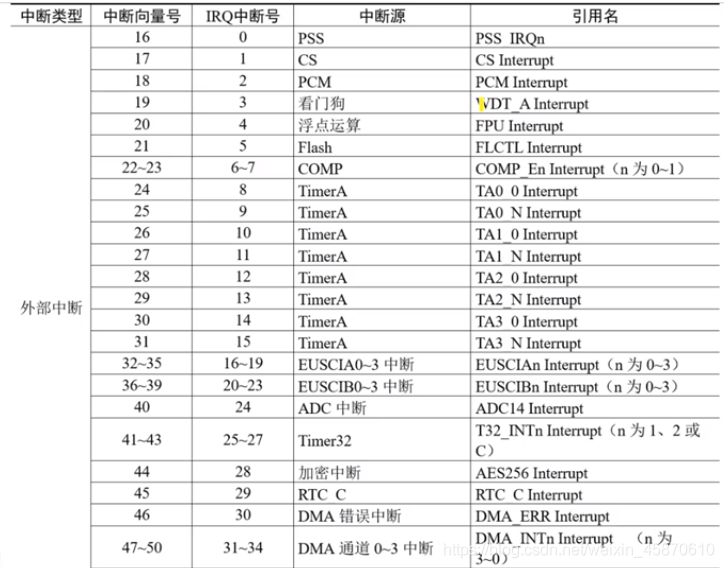

MSP432非内核中断向量表:

三、MSP432系列MCU的引脚功能

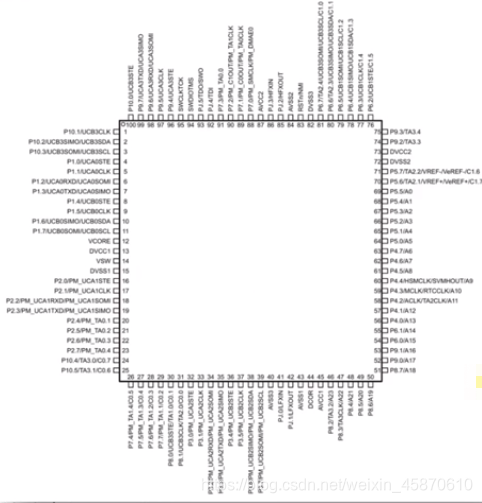

3.1MSP432系列MCU的引脚功能——引脚简介

- 每个引脚都可能有多个复用功能,有的引脚有两个复用功能,有的有四个复用功能。

- 实际嵌入式产品的硬件系统设计时必须注意只能使用其中的一个功能。

- 进行硬件最小系统设计时,一般以引脚的第一功能作为引脚名进行原理图设计,若实际使用的是其另一功能,可以用括号加以标注,这样设计的硬件最小系统就比较通用。

3.2 MSP432系列MCU的引脚功能——硬件最小系统引脚

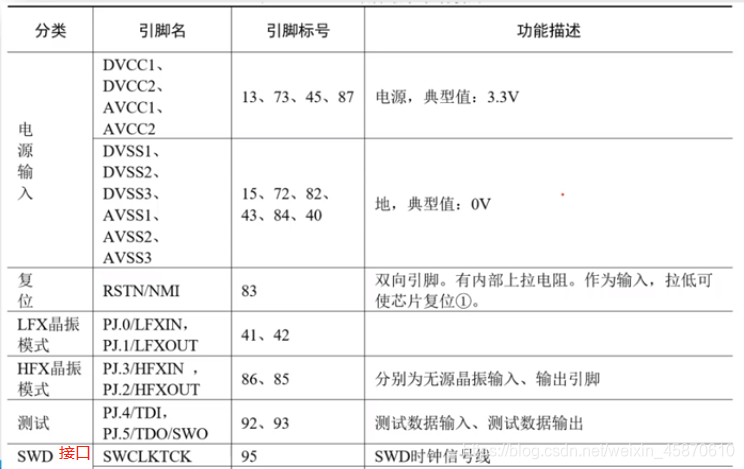

MSP432硬件最小系统引脚是:需要为芯片提供服务的引脚,包括电源类引脚、复位引脚、晶振引脚等。

MSP432硬件最小系统引脚:

3.3 MSP432系列MCU的引脚功能——对外提供服务的引脚

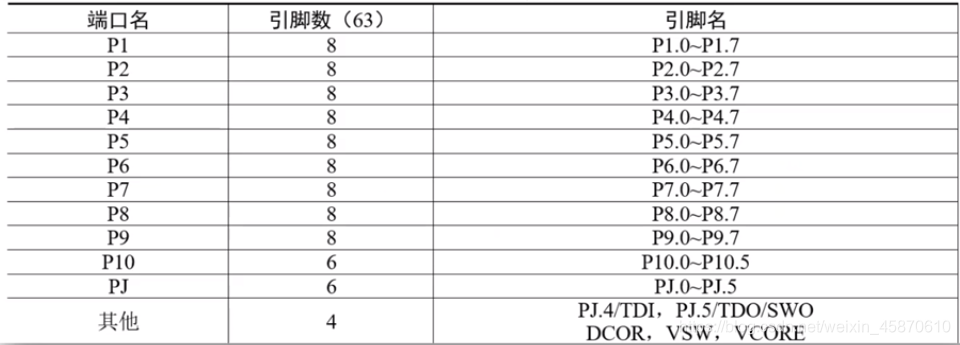

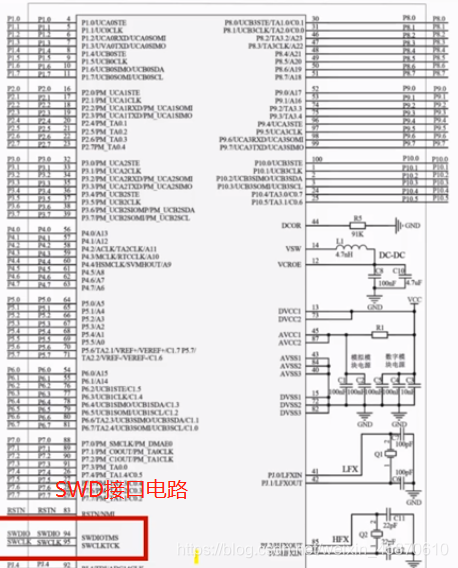

芯片的其他引脚为我们提供服务,也可称之为I/O端口资源类引脚。这些引脚一般具有多种复用功能。需重点掌握该类引脚的应用方法。I/O端口资源类引脚,如下给出了MSP432芯片引脚功能复用表

四、MSP432系列最小系统原理图

4.1MSP432系列MCU硬件最小系统原理图——简介

- MCU的硬件最小系统是指包括电源、晶振、复位、写入调试器接口等可使内部程序得以运行的、规范的、可复用的核心构件系统。

- 当MCU工作不正常时,首先就要查找最小系统中可能出错的元件。

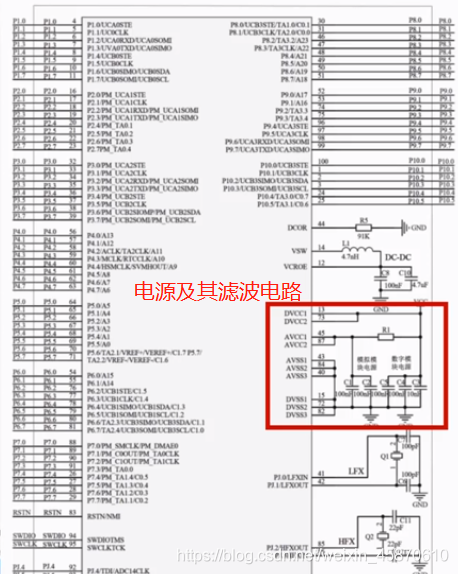

4.2 MSP432系列MCU硬件最小系统原理图——电源及其滤波电路

- 电路中需要大量的电源类引脚用来提供足够的电流容量同时保持芯片电流平衡

- 所有的电源引脚必须外接适当的滤波电容抑制高频噪音。

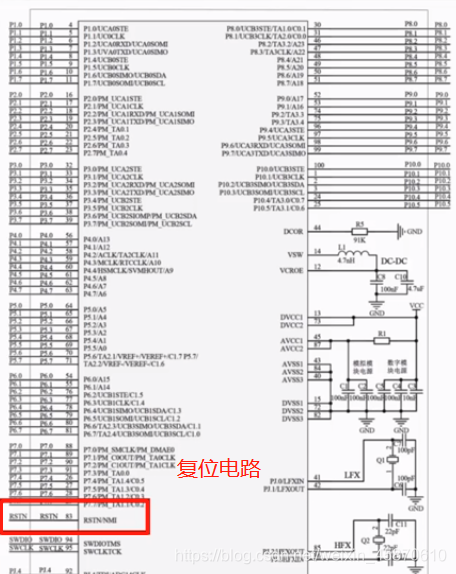

4.3 MSP432系列MCU硬件最小系统原理图——复位电路及复位功能

-

若复位引脚有效(低电平),则会引起MCU复位。

-

从引起MCU复位的内部与外部因素来区分,复位可分为外部复位和内部复位。

-

从复位时芯片是否处于上电状态来区分,复位可分为冷复位和热复位。

-

从CPU响应快慢来区分,复位还可分为异步复位与同步复位。

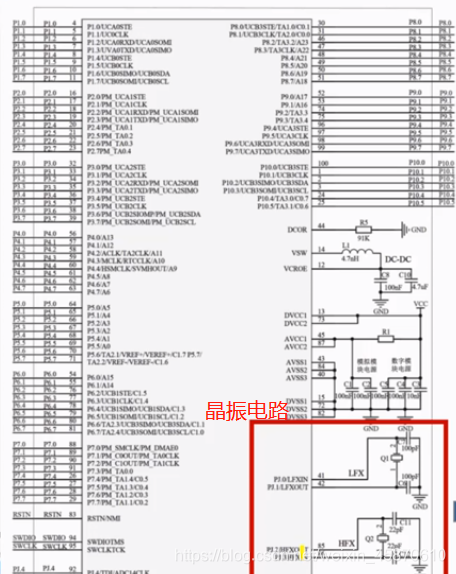

4.4 MSP432系列MCU硬件最小系统原理图——晶振电路

-

MSP432芯片可使用内部晶振或外部晶振两种方式为MCU提供工作时钟。

-

内部时钟源(IRC),频率分慢速32.768kHz和快速4MHz。通过编程,最大可产生48MHz内核时钟及24MHz总线时钟。使用内部时钟源可略去外部晶振电路。

-

若时钟源需要更低的功耗,或需要更快速的响应和快速的突发处理能力,可选用外部晶振。

4.5 MSP432系列MCU硬件最小系统原理图——SWD接口电路

-

MSP432芯片的调试接口SWD是基于CoreSight架构,该架构在限制输出引脚和其他可用资源情况下,提供了最大的灵活性。

-

通过SWD接口可以实现程序下载和调试功能。

-

SWD接口只需两根线,数据输入/输出线(DIO)和时钟线(CLK)。

1702

1702

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?