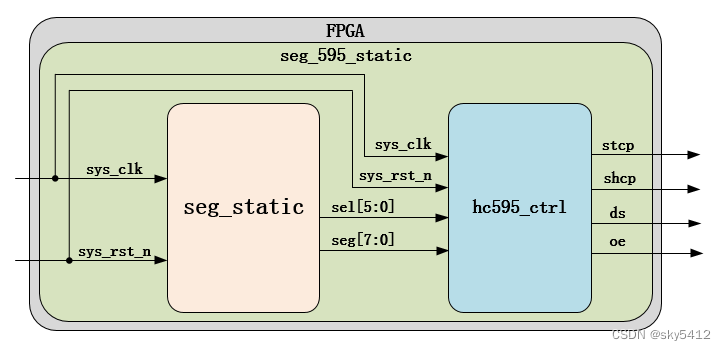

数码管的静态显示

实验目标

控制六位数码管让其以000000、111111、222222一直到FFFFFF循环显示。每个字符显示0.5s后变化。

程序设计

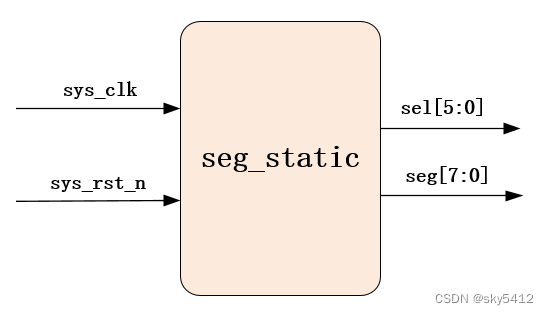

seg_static模块

静态数码管驱动模块,产生数码管位选和段选信号

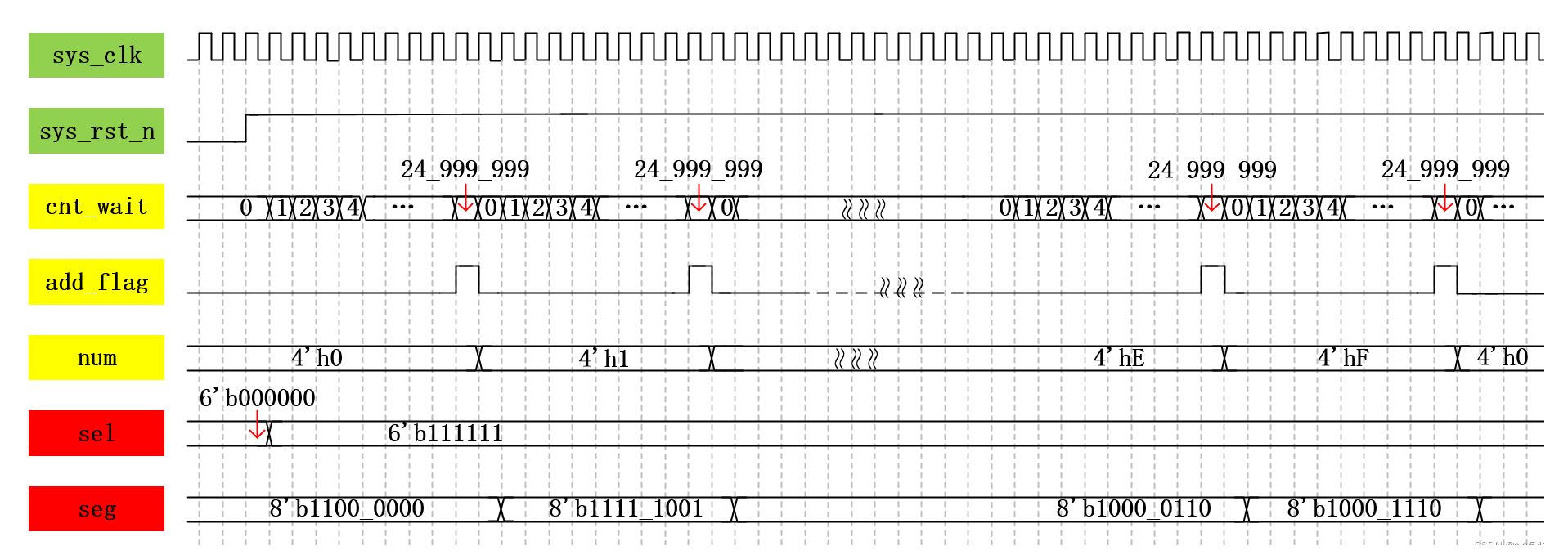

波形图绘制

cnt_wait:0.5s计数器

add_flag:当cnt_wait计数到最大值时,拉高一个电平,用来控制数码管字符的跳转。

num:每个数码管显示的字符,当检测到跳转的add_flag信号为高时,让各个数码管显示的字符加1。当加到4’hF时让其归0重新相加以此循环

sel:数码管位选信号,六个数码管都使用,所以一直为“111_111”

seg:数码管段选信号,根据num的值使用case选择即可

代码编写

module seg_static

#(

parameter CNT_MAX = 25'd24_999_999

)

(

input clk,reset,

output reg[5:0] sel,

output reg[7:0] seg

);

reg[24:0] cnt;

reg[3:0] data;

reg cnt_flag;

// 计数器cnt

always @(posedge clk or negedge reset)

if(reset == 1'b0)

cnt <= 25'd0;

else if(cnt == CNT_MAX)

cnt <= 25'd0;

else

cnt <= cnt + 25'd1;

// 产生控制数码管符号变化的信号

always @(posedge clk or negedge reset)

if(reset == 1'b0)

cnt_flag <= 1'd0;

else if(cnt == CNT_MAX - 1)

cnt_flag <= 1'b1;

else

cnt_flag <= 1'b0;

// 数码管符号控制

always @(posedge clk or negedge reset)

if(reset == 1'b0)

data <= 4'd0;

else if(data == 4'd15 && cnt_flag == 1'b1)

data <= 4'd0;

else if(cnt == CNT_MAX)

data <= data + 4'd1;

else

data <= data;

// 数码管位选信号

always @(posedge clk or negedge reset)

if(reset == 1'b0)

sel <= 6'b000_000;

else

sel <= 6'b111_111;

// 数码管段选信号

always @(posedge clk or negedge reset)

if(reset == 1'b0)

seg <= 8'hc0;

else

case(data)

4'd0:seg <= 8'hc0;

4'd1:seg <= 8'hf9;

4'd2:seg <= 8'ha4;

4'd3:seg <= 8'hb0;

4'd4:seg <= 8'h99;

4'd5:seg <= 8'h92;

4'd6:seg <= 8'h82;

4'd7:seg <= 8'hf8;

4'd8:seg <= 8'h80;

4'd9:seg <= 8'h90;

4'd10:seg <= 8'h88;

4'd11:seg <= 8'h83;

4'd12:seg <= 8'hc6;

4'd13:seg <= 8'ha1;

4'd14:seg <= 8'h86;

4'd15:seg <= 8'h8e;

default:seg <= 8'hff;

endcase

endmodule

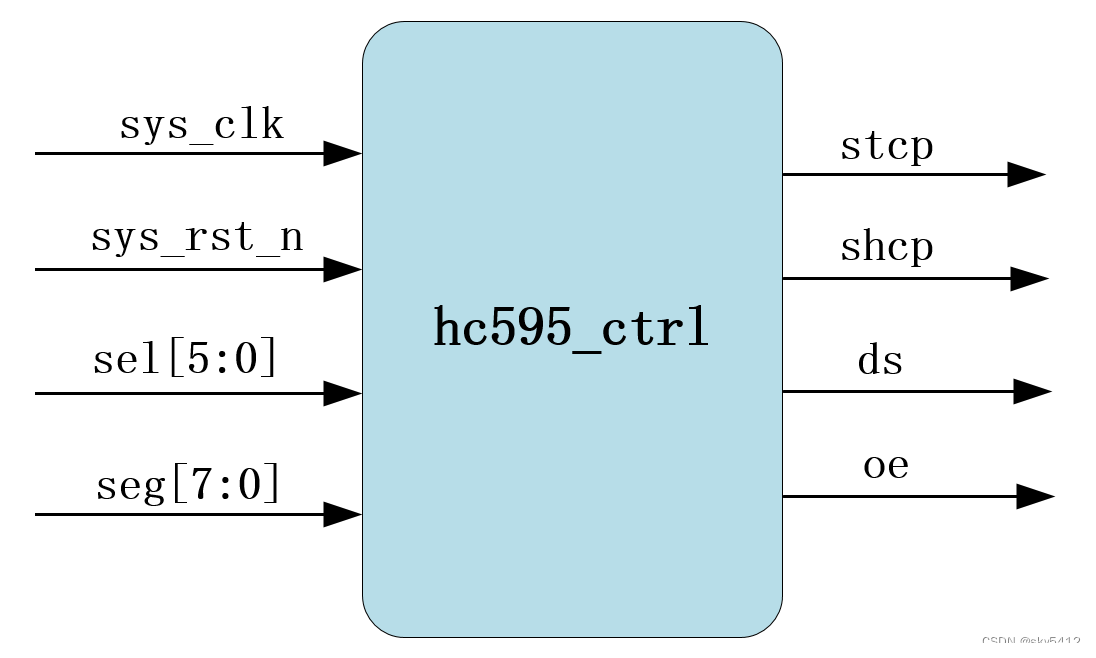

74HC595控制模块

该模块需要产生stcp、shcp、ds、oe四个信号对74HC595进行控制。

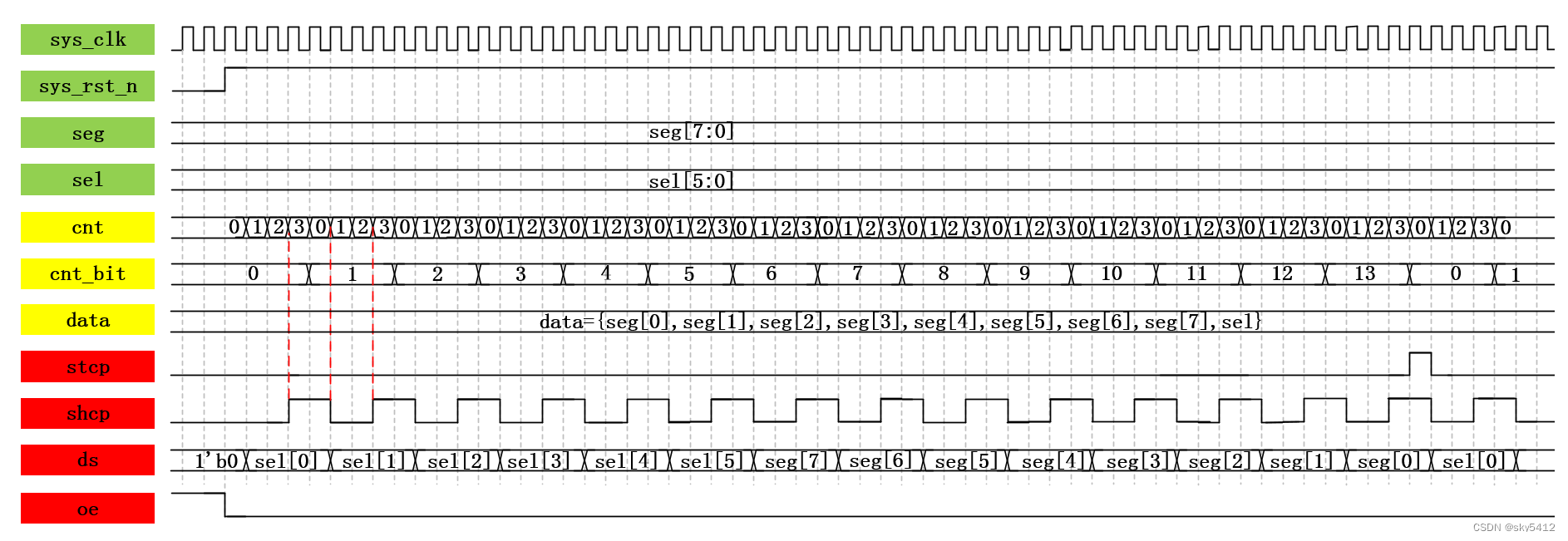

波形图绘制

cnt:对clk进行四分频,因为shcp和stcp的最大频率是有限制的

cnt_bit:传输位数计数器。我们知道我们需要传输14bit的数据,故我们需要一个数据器对传输的位数进行计数,这样我们对传输完成14位数据就可以用这个计数器进行判别了。

data:位选和段选拼接的数据

ds:串行数据输出,根据74HC595芯片规定的数据输入顺序

shcp:移位寄存器时钟,上升沿时将数据写入移位寄存器中。我们在ds数据的中间状态拉高产生上升沿,这样可以使shcp采得的ds数据更加稳定。

stcp:存储寄存器时钟。当我们14位数码管控制信号传输完之后我们需要拉高一个stcp时钟来将信号存入存储寄存器之中。

oe:存储寄存器数据输出使能信号,低电平有效。

代码编写

module hc595_ctrl

(

input clk,reset,

input[5:0] sel,

input[7:0] seg,

output reg ds,shcp,stcp,

output oe

);

wire [13:0] data;

reg[1:0] cnt;

reg[3:0] cnt_bit;

assign data = {seg[0],seg[1],seg[2],seg[3],seg[4],seg[5],seg[6],seg[7],sel};

// 分频计数器

always @(posedge clk or negedge reset)

if(reset == 1'b0)

cnt <= 2'd0;

else if(cnt == 2'd3)

cnt <= 2'd0;

else

cnt <= cnt + 1'b1;

//数据传输位数控制

always @(posedge clk or negedge reset)

if(reset == 1'b0)

cnt_bit <= 4'd0;

else if(cnt_bit==4'd13 && cnt==2'd3)

cnt_bit <= 4'd0;

else if(cnt == 2'd3)

cnt_bit <= cnt_bit + 1'b1;

else

cnt_bit <= cnt_bit;

// ds信号输出

always @(posedge clk or negedge reset)

if(reset == 1'b0)

ds <= 1'b0;

else if(cnt == 2'd0)

ds <= data[cnt_bit];

else

ds <= ds;

always @(posedge clk or negedge reset)

if(reset == 1'b0)

shcp <= 1'b0;

else if(cnt == 2'd2)

shcp <= 1'b1;

else if(cnt == 2'd0)

shcp <= 1'b0;

else

shcp <= shcp;

always @(posedge clk or negedge reset)

if(reset == 1'b0)

stcp <= 1'b0;

else if(cnt_bit==4'd0 && cnt==2'd0)

stcp <= 1'b1;

else if(cnt_bit==4'd0 && cnt==2'd2)

stcp <= 1'b0;

else

stcp <= stcp;

assign oe = 1'b0;

endmodule

仿真测试

`timescale 1 ns/ 1 ns

module seg_595_static_vlg_tst();

reg clk;

reg reset;

wire ds;

wire oe;

wire shcp;

wire stcp;

seg_595_static

i1 (

.clk(clk),

.ds(ds),

.oe(oe),

.reset(reset),

.shcp(shcp),

.stcp(stcp)

);

initial

begin

clk = 1'b1;

reset <= 1'b0;

#20

reset <= 1'b1;

end

always #10 clk = ~clk;

endmodule

567

567

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?