数字集成电路时序分析基础

b站视频:BV1if4y1p7Dq 的学习笔记

第一讲

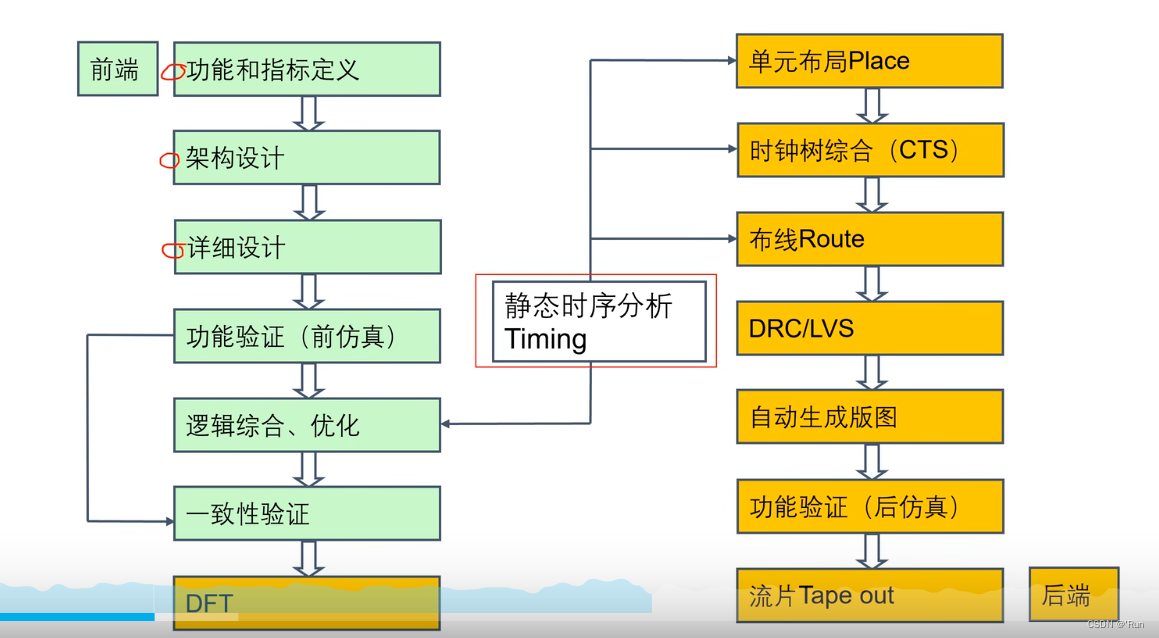

1、数字芯片与FPGA设计流程

第一步:找到现实问题

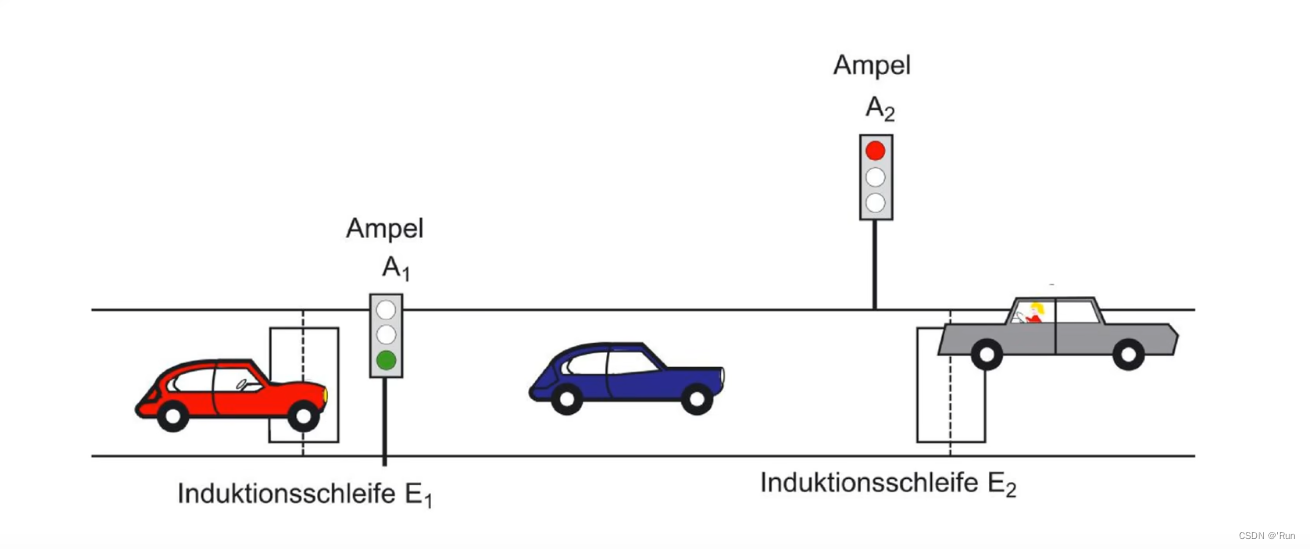

一个红绿灯问题

一个红绿灯问题

第二步:将现实问题抽象为功能和指标

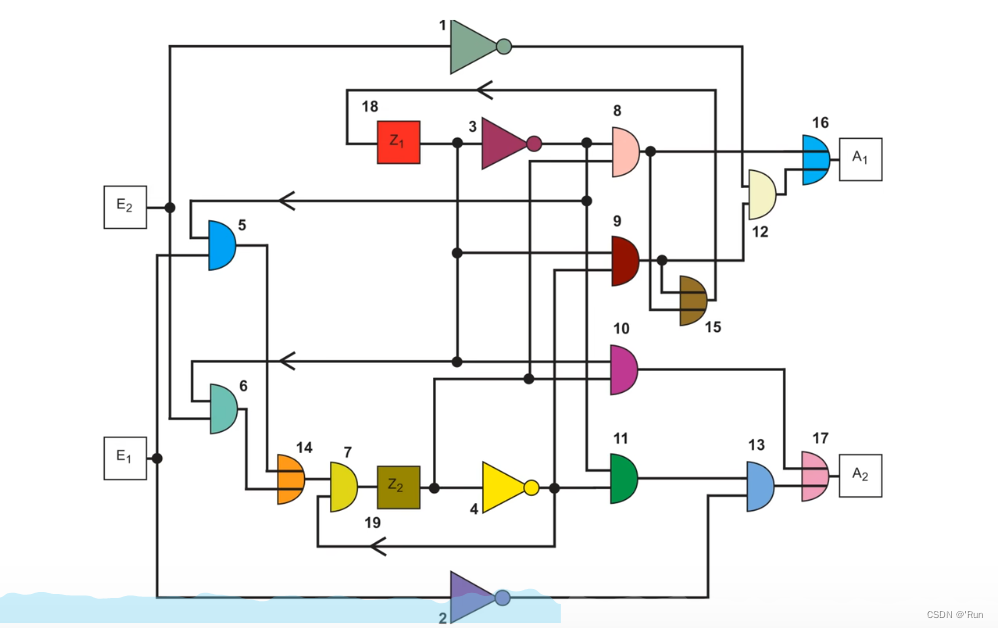

第三步:设计架构

第四步:进行RTL设计

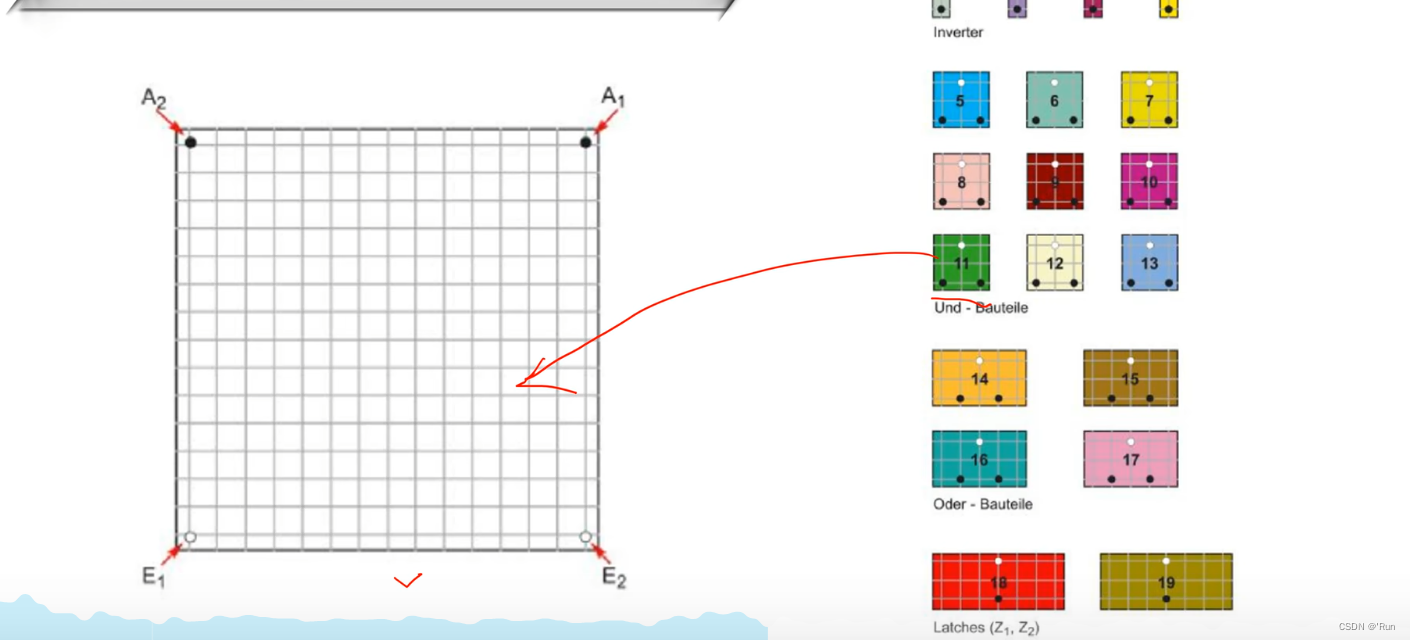

第五步:进行逻辑综合,映射为标准单元

注意此时只是映射为了标准单元但是这些标准单元并没有,解决这些标准单元如何排列在芯片上

注意此时只是映射为了标准单元但是这些标准单元并没有,解决这些标准单元如何排列在芯片上

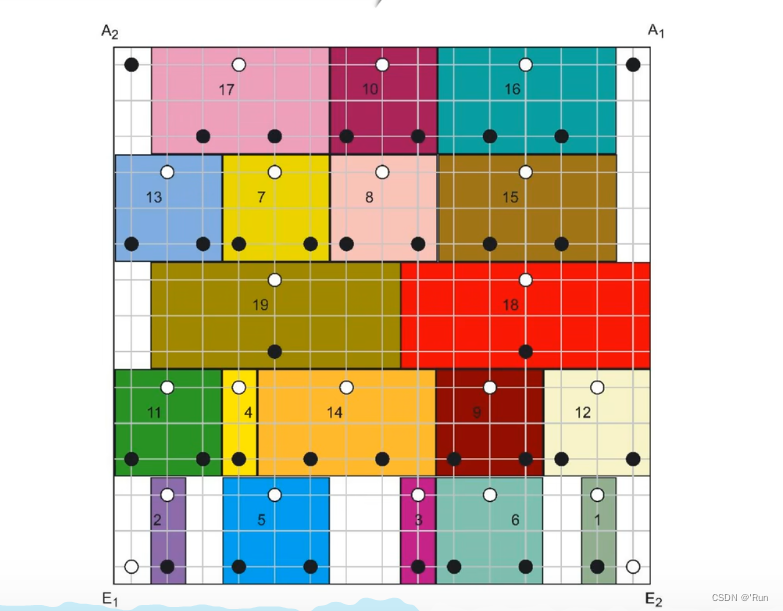

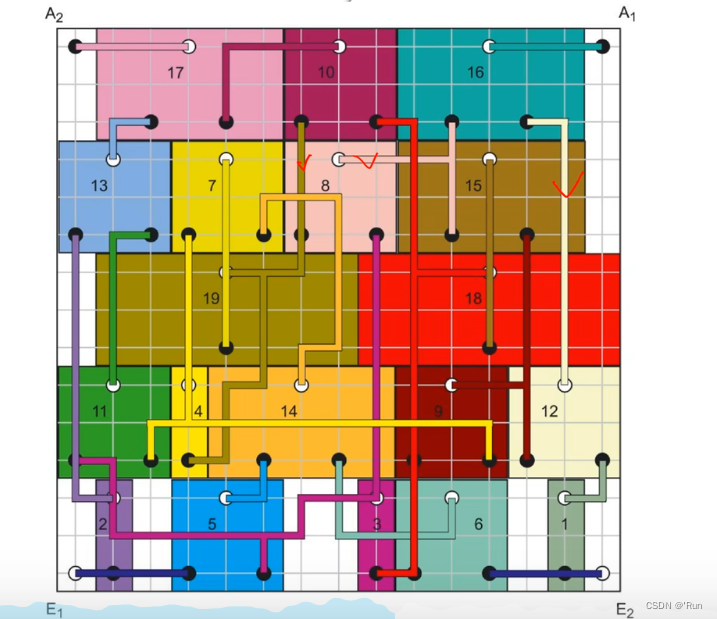

第六步:后端将标准单元放到芯片里,即floor plan

第七步:进行布线,将标准单元正确的链接起来。

一个更加完善的芯片设计流程:

FPGA的设计流程基本相同,只不过要在对应的厂商的软件上完成。

2、静态时序分析概述

静态时序分析本质上就是:检查建立时间和保持时间

1、建立时间(Setup Time):时钟上升沿前数据需要稳定下来的时间。Tsetup

2、保持时间(Hold Time):时间上升沿之后,数据依旧需要保持稳定的时间。

静态时序分析主要是针对同步电路,异步电路有异步二点处理方式,现代IC基本可以看作:局部同步,全局异步。

静态时序分析(STA)与功能验证(simulation)的区别

1、功能验证通过穷举性的,生成测试向量输入,观察输出确定功能是否正确。而静态时序分析,只是观察每个D触发器能否正确采样,所以静态时序分析速度比功能验证更快。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?