一、目标要求

使用verilog语言编程实现在FPGA开发板的蜂鸣器歌唱“两只老虎”

二、如何产生不同的声音

通过给无源蜂鸣器不同频率的PWM方波信号从而实现不同的音调音符。

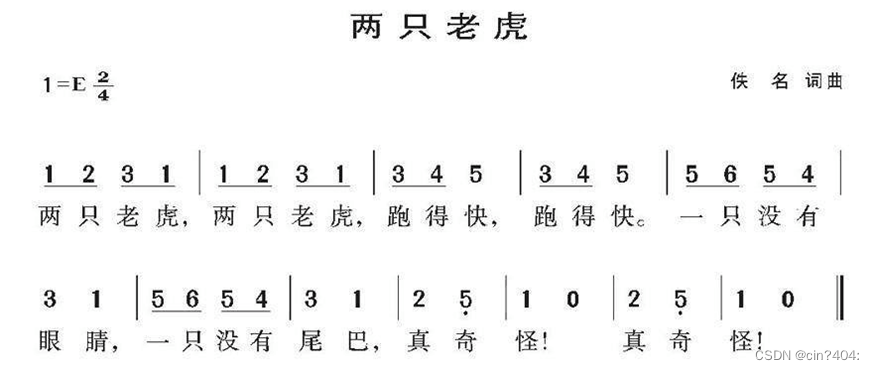

1、“两只老虎”乐普

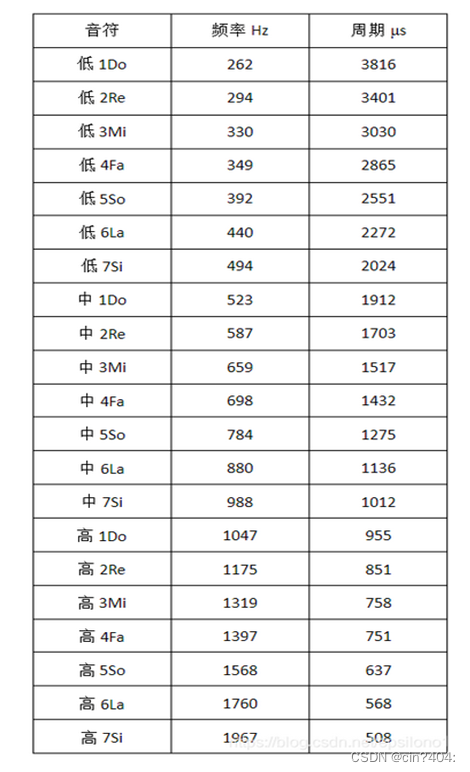

2、各音符对应的频率和周期

三、代码实现思路

首先我们需要一个计数器(cnt_time)来实现对音符的驱动(因为对乐谱不懂哈,所以在本次项目中,博主以250ms唱一个音符)。其次我们需要一个计数器来计算当前时间唱到了哪个音符(cnt_num)以实现当前音符和PWM方波信号的匹配,从而使蜂鸣器能够在正确的时间发出正确的声音,最后我们需要一个计数器(cnt_frq)对各音符对应的PWM方波信号进行计算。具体代码实现如下:

//实现简单的两只老虎

module beep_pwm (

input clk ,

input rst_n ,

output reg beep

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2240

2240

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?