数字电路基础知识

3 MOS管

3.1 CMOS

COMS Complementary - Metal - Oxide - Semiconductor(互补金属氧化物半导体)

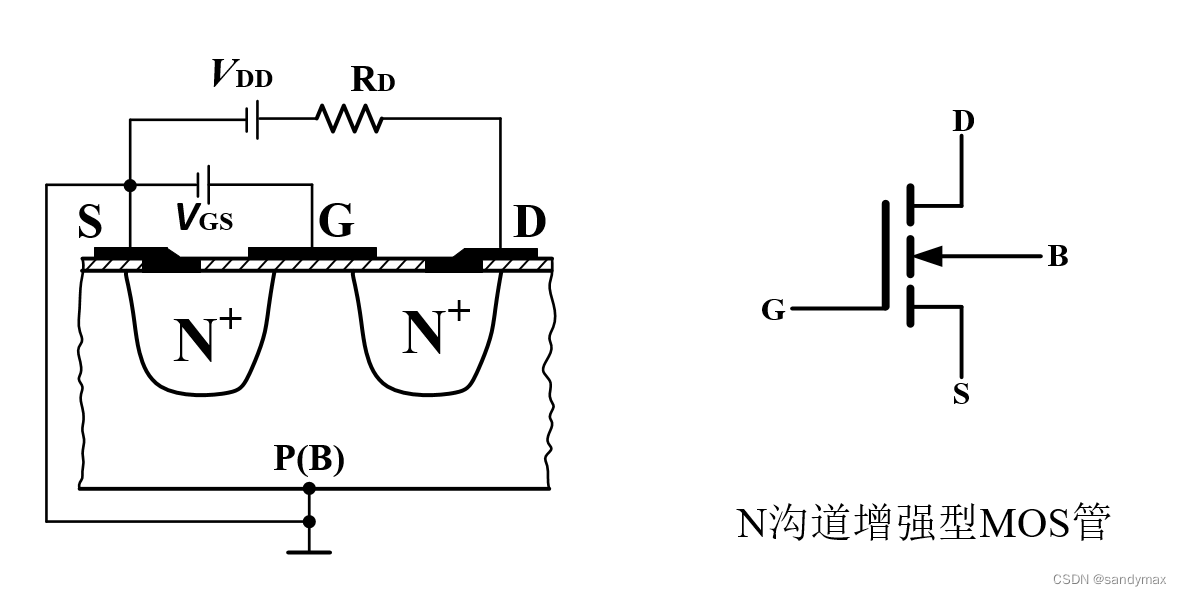

3.1.1 N沟道增强型MOS管

这种类型的MOS管采用P型衬底,导电沟道是N型;

在VGS = 0时没有导电沟道,开启电压VGS(th)为正

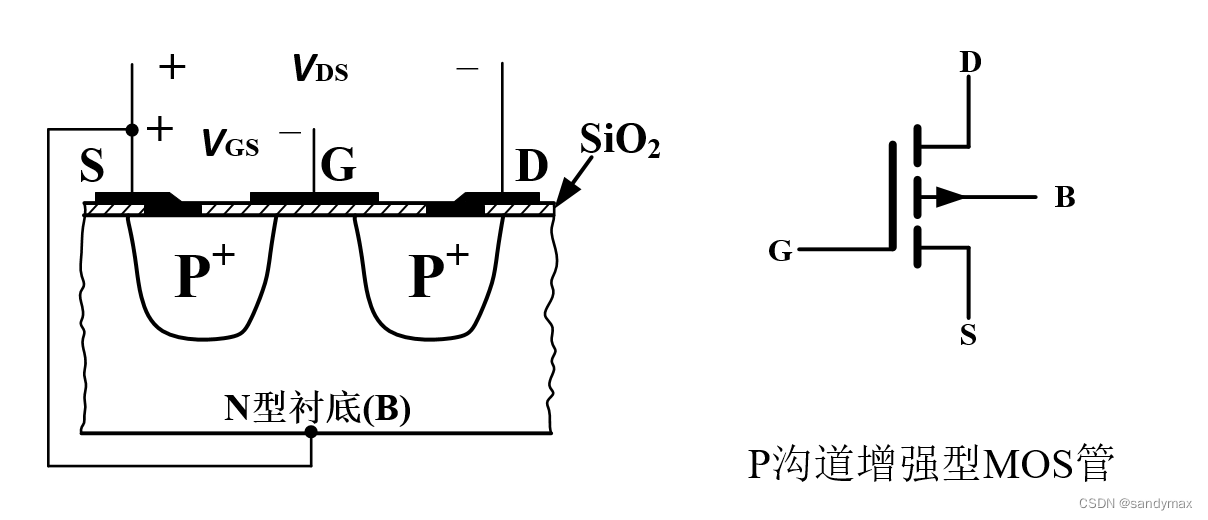

3.1.2 P沟道增强型MOS管

这种类型的MOS管采用N型衬底,导电沟道是P型;

VGS = 0时不存在导电沟道,只有在栅极上加以足够大的负电压时,才能把N型衬底中的少数载流子 - 空穴吸引到栅极下面的衬底表面,形成P型的导电沟道;因此,P沟道增强型MOS管的开启电压VGS(th)为负值。

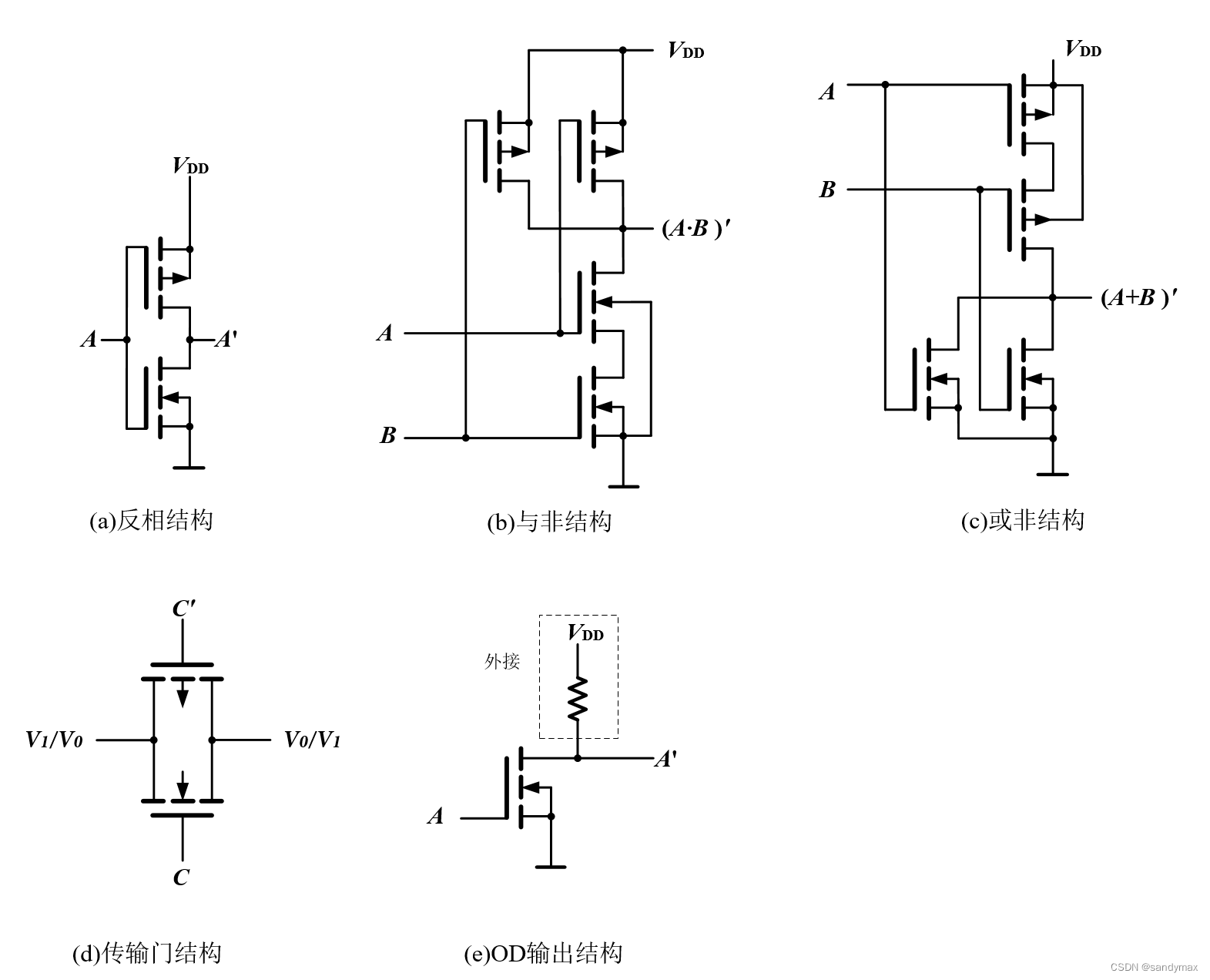

3.2 COMS集成门电路的几种基本功能结构

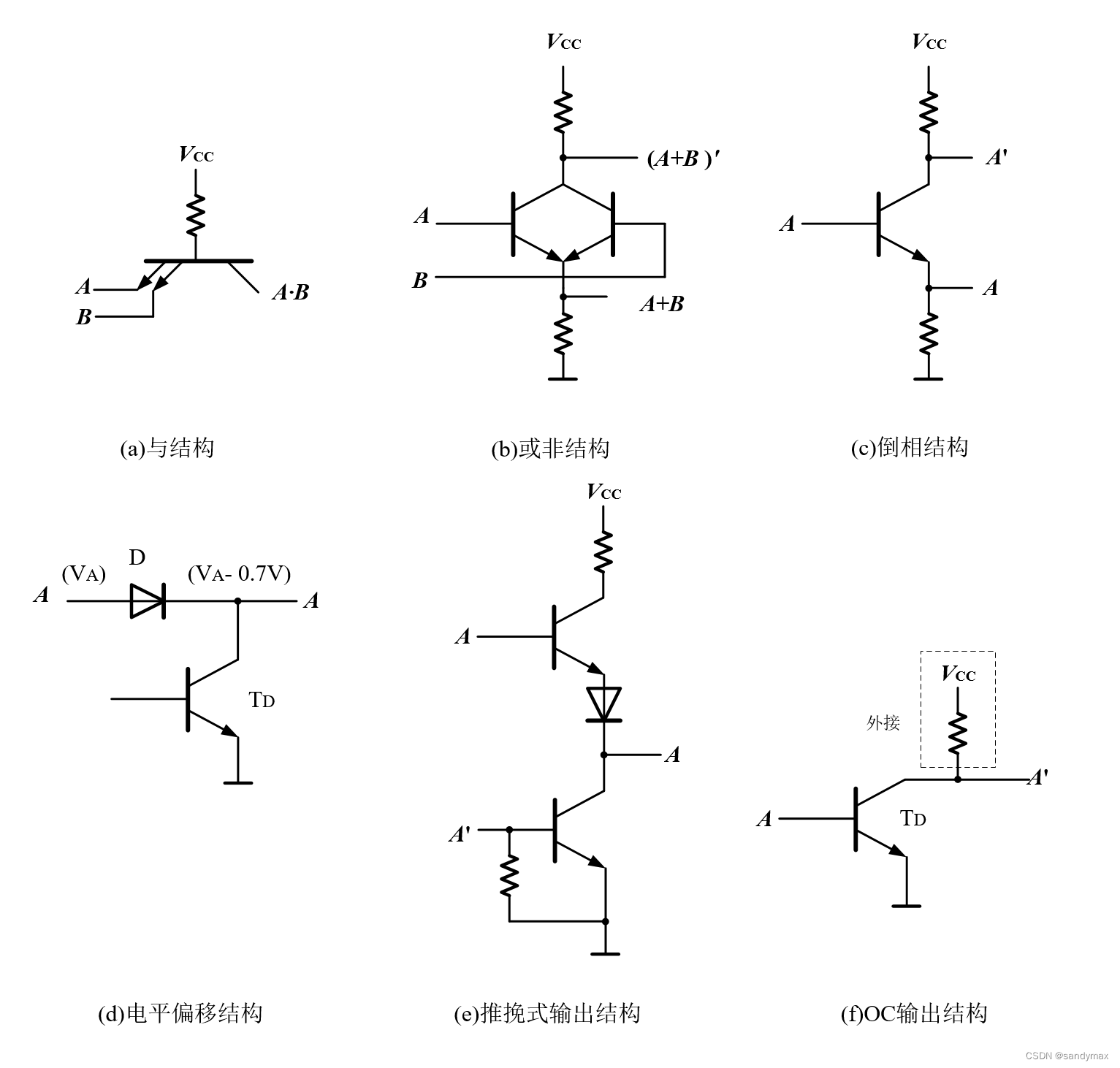

3.3 TTL集成门电路的几种基本功能结构

4. 触发器(Flip Flop)

4.1 SR锁存器(Set-Reset Latch)

4.1.1 或非门构成的SR锁存器

SD称为置位端或置1输入端;

RD称为复位端或置0输入端。

当SD =1、RD =0时,Q=1、Q’=0。在SD =1信号消失以后(即SD 回到0),由于有Q端的高电平接回到G2的另一个输入端,因而电路的1状态得以保持。

当SD =0、RD =1时,Q=0、Q’=1。在RD =1信号消失以后,电路保持0状态不变。

当SD = RD = 0时,电路维持原来的状态不变。

当SD = RD = 1时,Q = Q’ = 0,这既不是定义的1状态,也不是定义的0状态。而且,在SD和RD同时回到0以后无法断定锁存器将回到1状态还是0状态。因此,在正常工作时输人信号应遵守SDRD = 0的约束条件,亦即不允许输入SD = RD = 1的信号。

或非门

| SDRD = 10 | 置1 |

|---|---|

| SDRD = 01 | 置0 |

| SDRD = 00 | 保持 |

| SDRD = 11 | 不允许 |

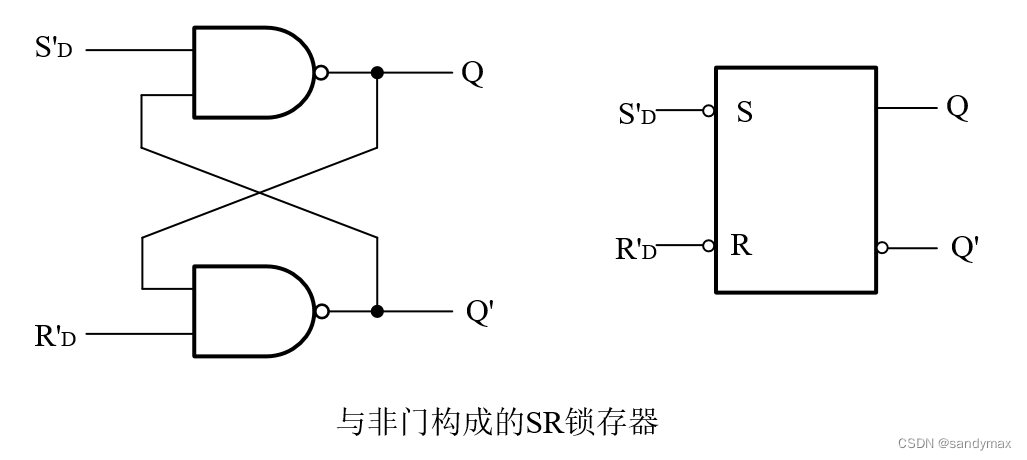

4.1.2 与非门构成的SR锁存器

与非门

| S’DR’D = 01 | 即SDRD = 10 | 置1 |

|---|---|---|

| S’DR’D = 10 | 即SDRD = 01 | 置0 |

| S’DR’D = 11 | 即SDRD = 00 | 保持 |

| S’DR’D = 00 | 即SDRD = 11 | 不允许 |

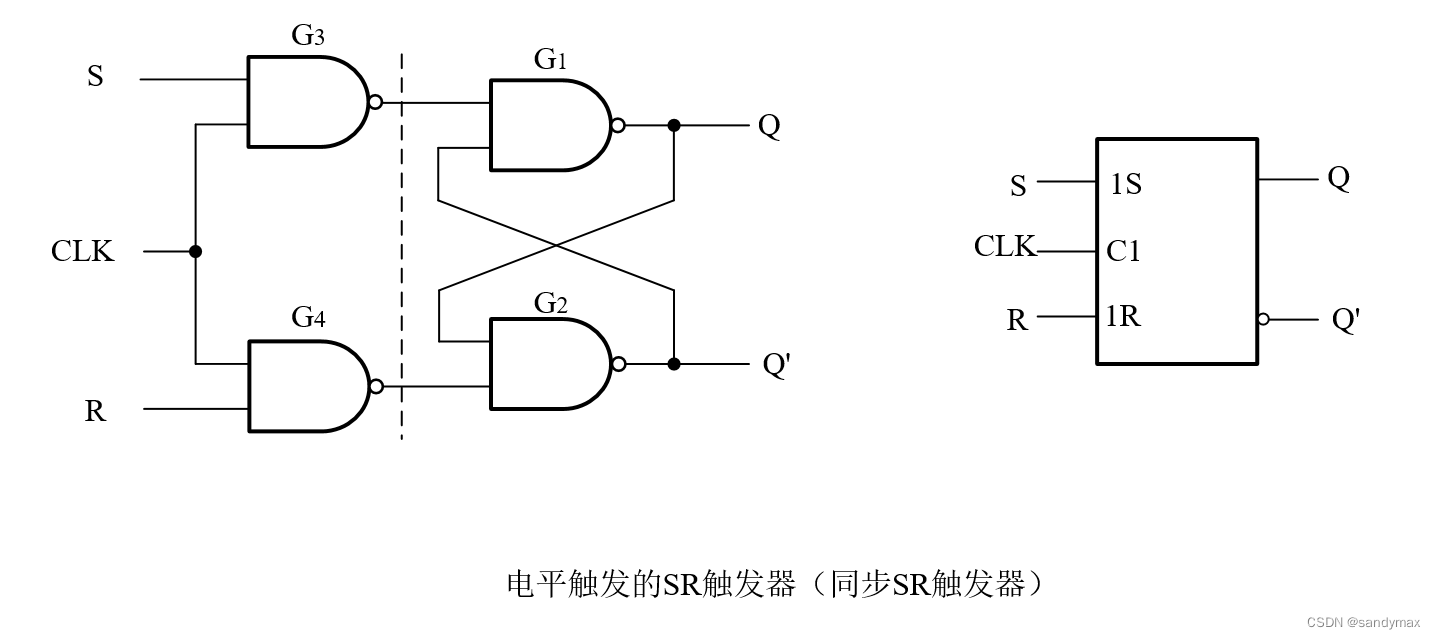

4.1.3 特性表

在SR锁存器中,输入信号直接加在输出门上,所以输入信号在全部作用时间里(即SD或RD为1的全部时间),都能直接改变输出端Q和Q’的状态。

正是由于这个缘故,也将SD(S’D)称为直接置位端,将RD(R’D)称为直接复位端,并且将这个电路称为直接置位、复位锁存器( Set - Reset Latch ) 。

4.1.4 习题的疑问

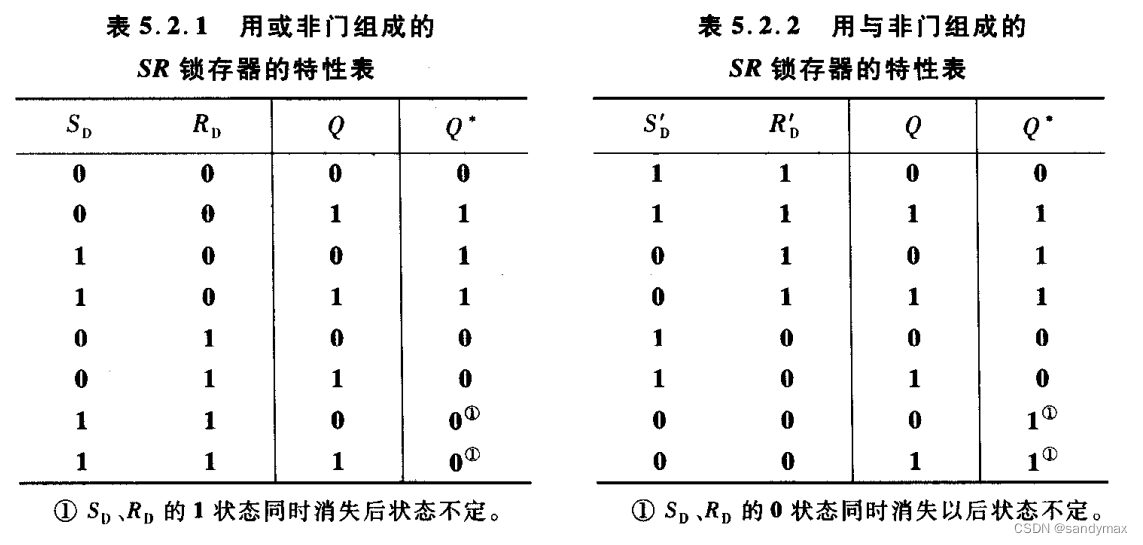

从图所示的波形图上可以看到,虽然在t3 ~ t4和 t7 ~ t8期间输入端出现了SD = RD = 0的状态,但由于SD首先回到了高电平,所以锁存器的次态仍是可以确定的???

4.2 电平触发的触发器

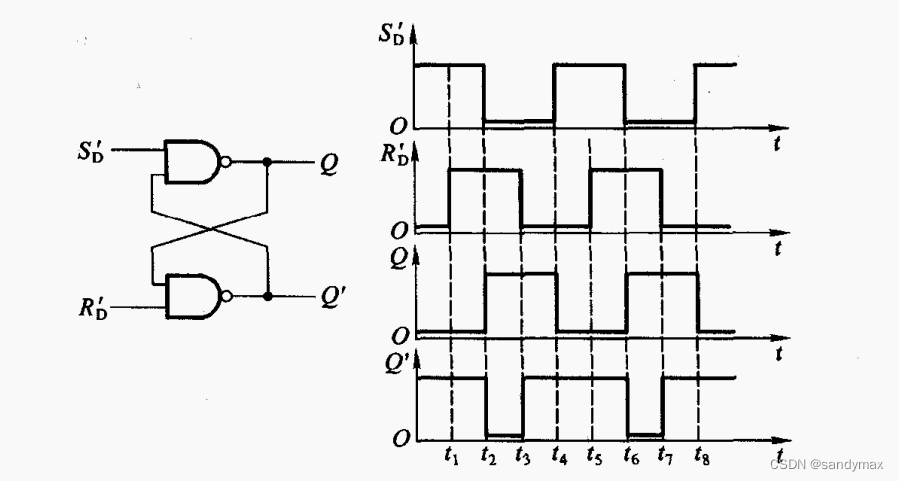

4.2.1 同步SR触发器

由图可知,当CLK = 0时,门G3、G4的输出始终停留在1状态,S、R端的信号无法通过G3、G4而影响输出状态,故输出保持原来的状态不变。

只有当触发信号CLK变成高电平以后,S、R信号才能通过门G3、G4加到由门G1、G2组成的锁存器上,“触发”电路发生变化,使Q和Q’根据S、R信号而改变状态。

因此,将 CLK的这种控制方式称为电平触发方式。

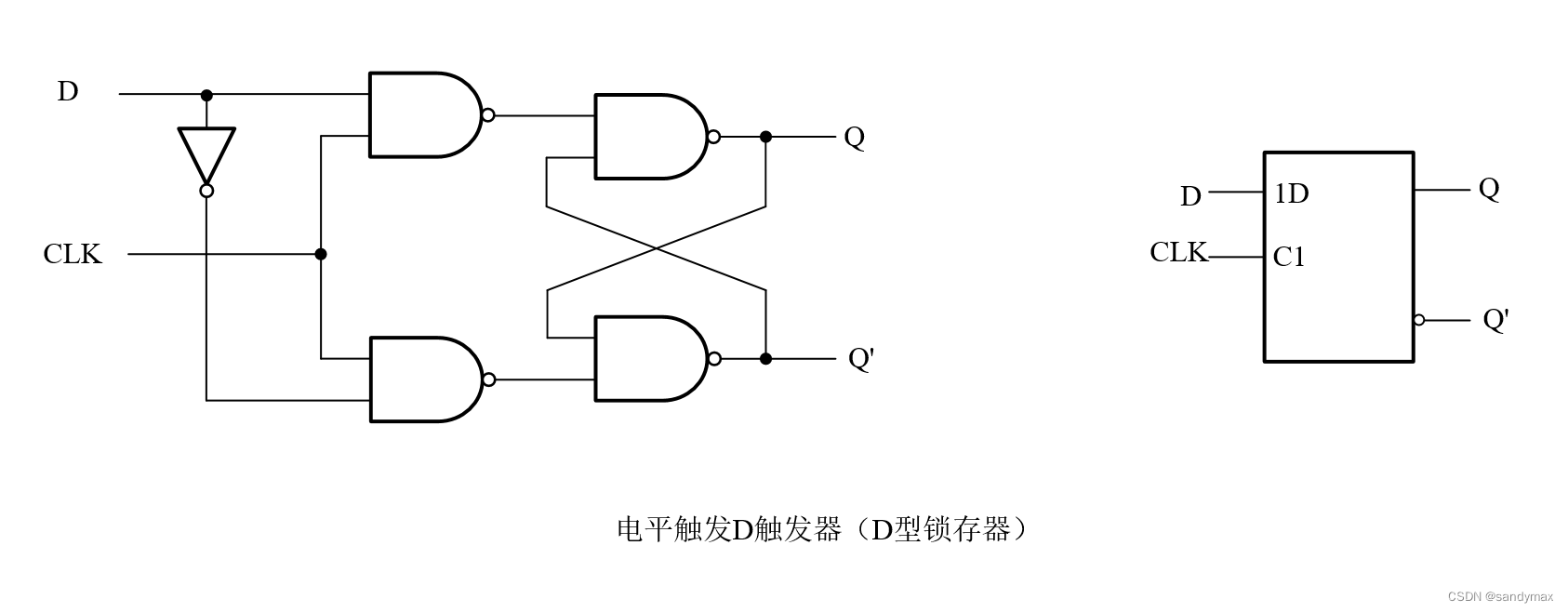

4.2.2 D型锁存器

由图可见,若D = 1,则CLK变为高电平以后触发器被置成Q = 1,CLK回到低电平以后触发器保持1状态不变。

若D = 0,则CLK变为高电平以后触发器被置成Q = 0,CLK回到低电平以后触发器保持0状态不变。

因为它仍然工作在电平触发方式下,所以同样具有电平触发的动作特点。

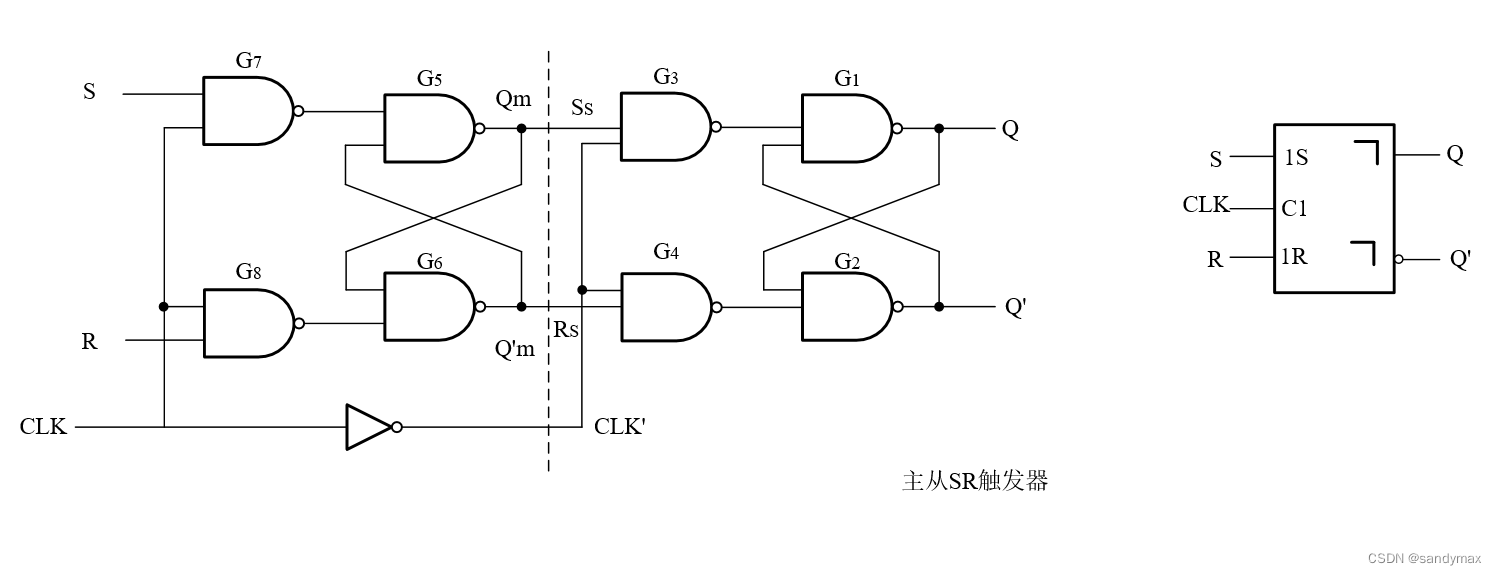

4.3 脉冲触发的触发器

4.3.1 主从SR触发器

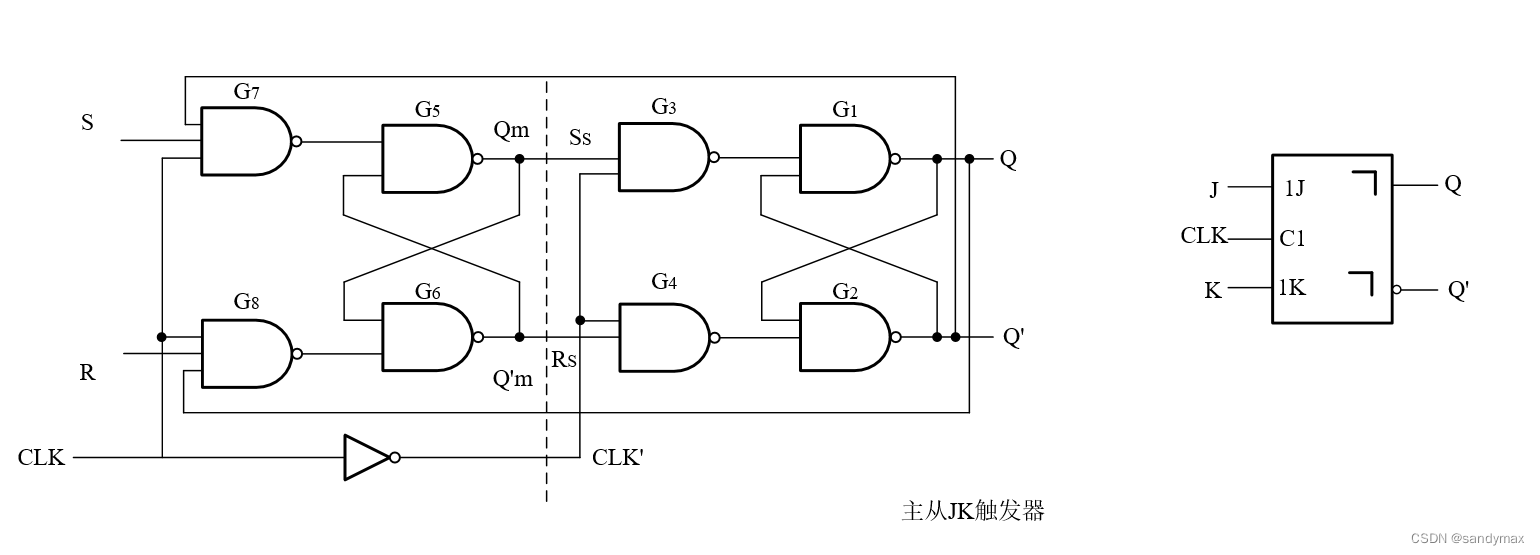

4.3.2 主从JK触发器

4.3.3 脉冲触发方式的动作特点

(1)触发器的翻转分两步动作。

第一步,在CLK =1期间主触发器接收输入端(S、R或JK)的信号,被置成相应的状态,而从触发器不动;

第二步,CLK 下降沿到来时从触发器按照主触发器的状态翻转,所以Q、Q’端状态的改变发生在CLK的下降沿。(若CLK以低电平为有效信号,则Q和Q’状态的变化发生在CLK的上升沿。)

(2)因为主触发器本身是一个电平触发SR触发器,所以在CLK = 1的全部时间里输入信号都将对主触发器起控制作用。

由于存在这样两个动作特点,在使用主从结构触发器时经常会遇到这样一种情况,就是在CLK =1期间输入信号发生过变化以后,CLK下降沿到达时从触发器的状态不一定能按此刻输人信号的状态来确定,而必须考虑整个CLK=1期间里输入信号的变化过程才能确定触发器的次态。

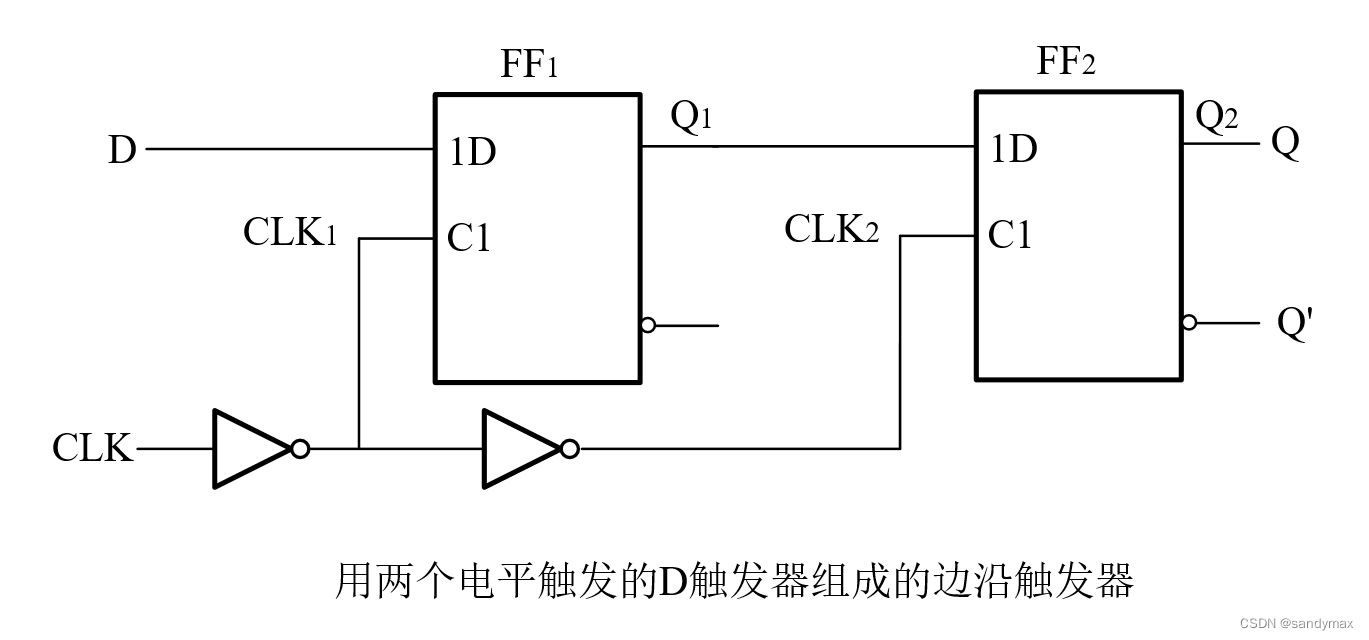

4.4 边沿触发的触发器

上图是用两个电平触发D触发器组成边沿触发D触发器的原理性框图,图中的FF1和FF2是两个电平触发的D触发器(也称为D型锁存器)。

由图可见,当CLK处于低电平时,CLK1为高电平,因而FF1的输出Q跟随输入端D的状态变化,始终保持Q = D。

与此同时,CLK2为低电平,FF2的输出Q,(也就是整个电路最后的输出Q)保持原来的状态不变。

当CLK由低电平跳变至高电平时,CLK1随之变成了低电平,于是Q1保持为CLK上升沿到达前瞬间输入端D的状态,此后不再跟随D的状态而改变。

与此同时,CLK2跳变为高电平,使Q2与它的输入状态相同。

由于FF2的输入就是FF1的输出Q1,所以输出端Q便被置成了与CLK上升沿到达前瞬时D端相同的状态,而与以前和以后D端的状态无关。

583

583

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?