1 数据类型

数据类型是用来表示数字电路中的数据存储和传递单元。

Verilog HDL中共有19种数据类型,其中最基本的有4种:

常:integer型

parameter型

变:reg型

wire型

其他:large, medium, scalared, small, time, tri, tri0, tri1, triand, trior, trireg, vectored, wand, wor等。

2 常量

在程序运行过程中,其值不能被改变的量,称为常量,有:

parameter常量(或称符号常量)

数字(包括整数、x和z、负数)

x:指不定值,0/1,寄存器类型变量(无初值时为x)

y: 指高阻态,断开

2.1 整数型常量

(1) 整数型常量(整常量)

二进制整数(b/B)

八进制整数(o/O)

十进制整数(d/D)

十六进制整数(h/H)

表达方式:

表达方式 | 说明 | 举例 |

<位宽>'<进制><数字> | 完整表达方式 | 8'b1100_0101 or 8'hA5 |

'<进制><数字> | 缺省位宽,由机器系统决定,至少32位 | 'hA5-(32位16进制) 10=32'd10=32'b1010 |

<数字> | 缺省进制-十进制;位宽默认32位 | 197 (32位十进制197) |

位宽指二进制宽度

为提高可读性,较长数字之间可用下划线隔开,但不能用在<进制><数字>之间。

(2) X & Z

X表示不定值;Z 表示高阻态

[eg] 8'b1001_xxxx= 8'b9x

8'b1010_zzzz= 8'baz

每个字符代表的二进制的宽度取决于所用的进制;

当用二进制表示时,已标明位宽的数,若用X or Z表示默写位,则只有在最左边的X or Z具有扩展性。

[eg] 8'bzx= 8'bzzzz_zzzx

8'b1x= 8'b0000_001x

8'haz= 8'h0000_00az

? 是Z的另一种表示符号,在case语句中使用?表示高阻态Z(少用)

[eg] casez(select)

4'b???1 : out =a ; //只看最低位是否为1,若为1,out=a;

4'b??1? : out =b ; //若不为1,看第二位是否为1,若为1,out=b;

4'b?1?? : out =c ;

4'b1??? : out =d ;

endcase

(3) 负数

在位宽前加一个负号,表示负数,求补码。

[eg] -8'd5 = 8'b1111_1011

8 'd5 = 8'b0000_0101

(反码) = 8'b1111_1010

(补码=反码+1) = 8'b1111_1011

[eg] -1 = -32'd1=32'b1111_1111

32'd1 = 32'b0000_0001

(反码) = 32'b1111_1110

(补码=反码+1) = 32'b1111_1111

减号不能放在位宽和进制之间,也不能放在进制与数字之间

2.2 参数型常量

(1)parameter常量(符号常量)

用parameter来定义一个标识符,代表一个常量——称为符号常量。格式:

parameter 参数名1 = 表达式, 参数名2 = 表达式,...;

(参数型数据的确认符) (赋值语句表)

每个赋值语句的右边必须为常数表达式,即只可包含数字或先前定义过的符号常量。

parameter addwidth =16; ✅

parameter addwidth =datawith*2; ❌

作用:

常用参数来定义延迟时间和变量宽度;

用字符串表示的任何地方,都可以用定义的参数来代替;

参数是本地的,只可在本模块内有效;

在模块或实例引用时,可通过参数传递改变在被引用模块或实例中已定义的参数。

(2)localparam符号常量

localparam 参数名1 = 表达式1, 参数名2 = 表达式2;

(参数型数据的确认符) (赋值语句表)

(3)parameter与localparam区别

parameter可用作在顶层模块中例化底层模块时传递参数的接口;

localparam的作用仅限于当前module,不能用作传递参数的借口。

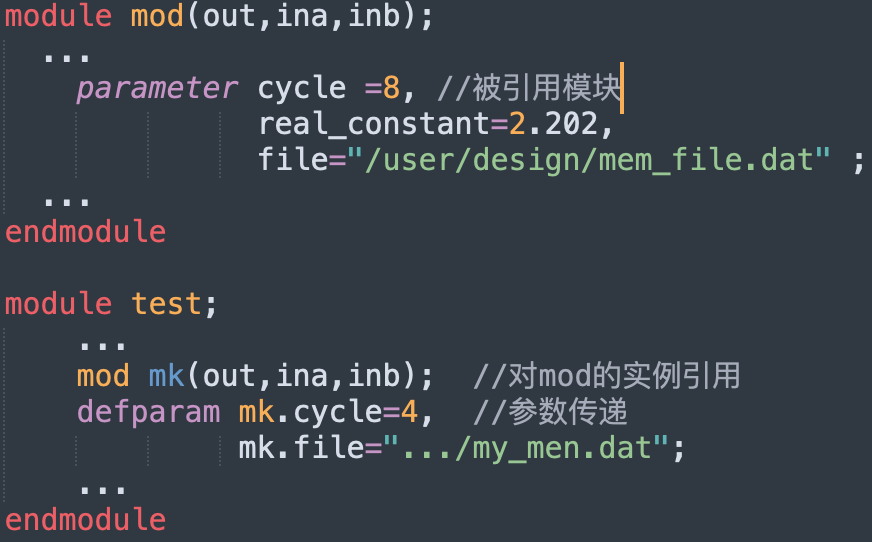

(4)参数的传递

方法一:defparam参数传递

defparam语句在编译时可重新定义参数值。

格式:

defparam 例化模块名. 参数名1 = 常数表达式 1 ,

例化模块名. 参数名2 = 常数表达式2 ;

可综合性:一般情况下是不可综合的;

先例化;

提示:不要使用defparam语句!

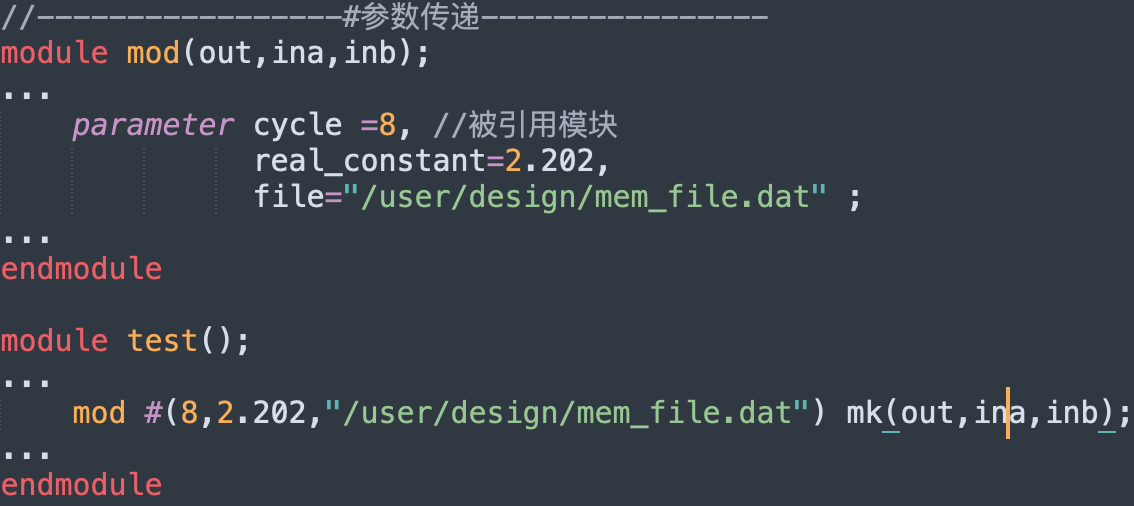

在模块实例引用时,可用# +参数的语法来重新定义参数。

方法二:符号 # 传递参数

格式:

被引用模块名# (参数1,参数2,...) [空格] 例化模块名 (端口列表)

参数位置关联,必须与被引用模块中的参数一一对应

3 变量

在程序运行过程中,可改变值的量称为变量。

数据类型有19种,常用3种:

网络型( nets type)

寄存器型 ( register type)

数组 ( memory type)

3.1 nets型变量

输出始终随输入的变化而变化的变量。

表示结构实体(如门)之间的物理连接。

常用nets型变量:

wire, tri : 连线类型(二者功能一致)

wor, trior : 具有线或特性的连线(二者功能一致)

wand, triand : 具有线与特性的连线(二者功能一致)

* tri1, tri0 : 上拉电阻和下拉电阻

* supply1, supply0 : 电源(逻辑1)和地(逻辑0)

- wire型变量

最常用的nets型变量,常用来表示以assign语句赋值的组合逻辑信号;

模块中的输入/输出类型缺省为wire型;

不声明位宽时,默认为1位;

可做任何方程式的输入,或assign语句和实例元件的输出;

assign <被连续赋值的变量一定是wire型> = <输入>

格式:

wire 数据名1, 数据名2,... , 数据名n; //n个位宽为1的wire;

wire型向量(总线)

wire [n-1:0] 数据名1, 数据名2,... , 数据名m;//每条总线位宽为n;

or wire [n-1:0] 数据名1, 数据名2,... , 数据名m;//共有m条总线;

3.2 reg 型

具有状态保持作用的电路元件(如触发器,寄存器等--可存多个数据,声明有多位);

常用来表示过程块语句(如initial, always, task, function)内的指定信号。

initial- 只能用一次

always- 中被赋值的变量必须声明为reg型;

reg 型必须有初值;

常用register型变量:

reg: 常代表触发器,也可描述组合逻辑信号;

interger: 32位带符号整数型变量;

real: 64位带符号实数型变量;

time: 无符号时间变量;

- reg型变量

在过程块中被赋值的信号,往往代表触发器,也可是组合逻辑信号。

格式:

reg 数据名1, 数据名2, ... , 数据名n;

reg型向量(总线)

reg [n-1:0] 数据名1, 数据名2, ... , 数据名m; //每个向量位宽为n;

reg [n:1] 数据名1, 数据名2, ... , 数据名m; //共有m个reg向量;

[eg] reg [4:1] regc, regd ; //regc,regd是位宽为4的reg型向量

- reg型与nets型区别:

register型变量需要被明确赋值,并在被重新赋值前一直保持原值(保持功能)

- reg型与wire型的区别:

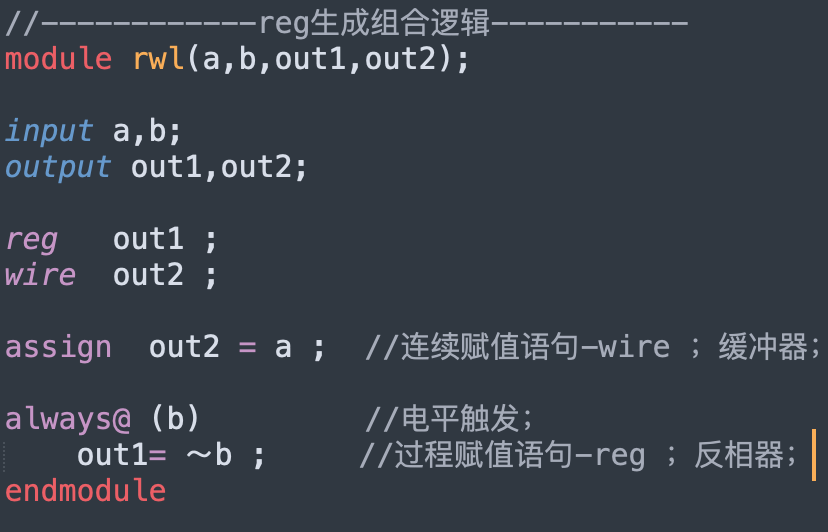

reg型变量:既可生成触发器,也可生成组合逻辑;

过程赋值;

wire型变量只可生成组合逻辑;

连续赋值;

reg生成组合逻辑:

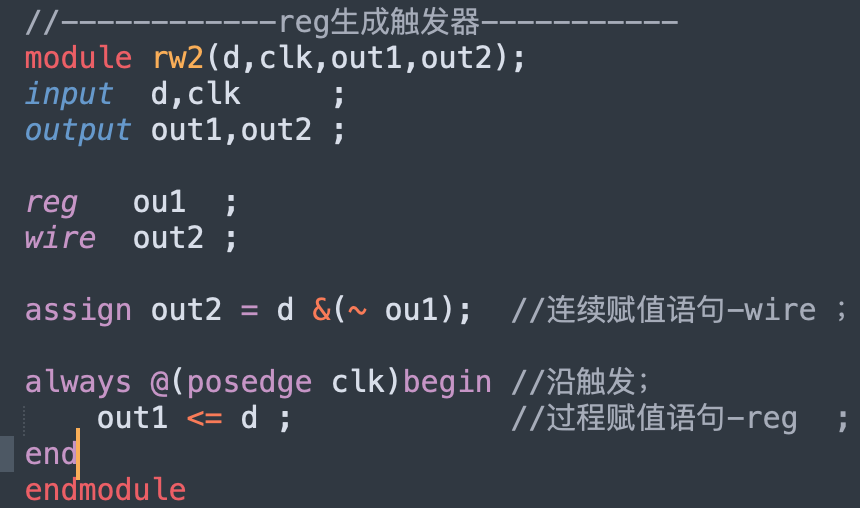

reg生成触发器:

3.3 memory 型变量-数组

由若干个相同宽度的reg型向量构成的数组。

Verilog HDL通过reg型变量建立数组对存储器建模;

memory型变量可描述RAM、ROM和reg文件;

memory型变量通过扩展reg型变量的地址范围来生成。

reg [n-1:0] 存储器名 [m-1:0] ; //声明1个位宽为n的扩展型变量

or reg [n:1] 存储器名 [m:1] ; //有m个存储单元

- memory型变量与reg型变量的区别

含义不同

[eg] reg [n-1:0] rega ; //一个n位的寄存器

reg[2:0] mema [n-1:0] ; //由n个3位寄存器组成的存储器

赋值方式不同

一个n位的寄存器可用一条赋值语句赋值;一个完整的存储器不行!

若对某存储器中的存储单元进行读写操作,必须指明该单元在存储器中的地址!

[eg] reg a =0; //合法赋值语句

mem a =0; //非法

mem a[8] =1; //合法

mem a[1023:0]=0; //合法

以上内容均为学习笔记,若有误请随时纠正

本文介绍了VerilogHDL中的数据类型,包括基本的integer、parameter、reg和wire类型,以及常量的定义,如整数、符号常量X和Z,并详细阐述了参数parameter和localparam的使用。同时,讨论了变量的概念,如nets型的wire和具有状态保持功能的reg型变量,以及它们在组合逻辑和时序逻辑中的应用。

本文介绍了VerilogHDL中的数据类型,包括基本的integer、parameter、reg和wire类型,以及常量的定义,如整数、符号常量X和Z,并详细阐述了参数parameter和localparam的使用。同时,讨论了变量的概念,如nets型的wire和具有状态保持功能的reg型变量,以及它们在组合逻辑和时序逻辑中的应用。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?