ADV7392/ADV7393配置

配置代码格式如:{8'[i2c_slave_dev_addr], 8'[i2c_slave_reg_addr], 8'[i2c_write_data]}

相关寄存器声明可见器件手册或其他博文

-

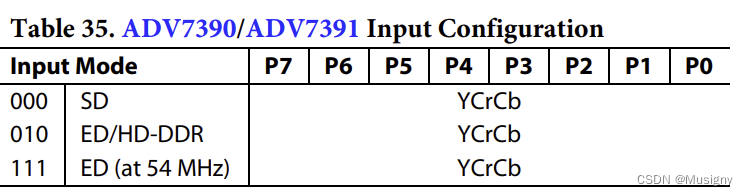

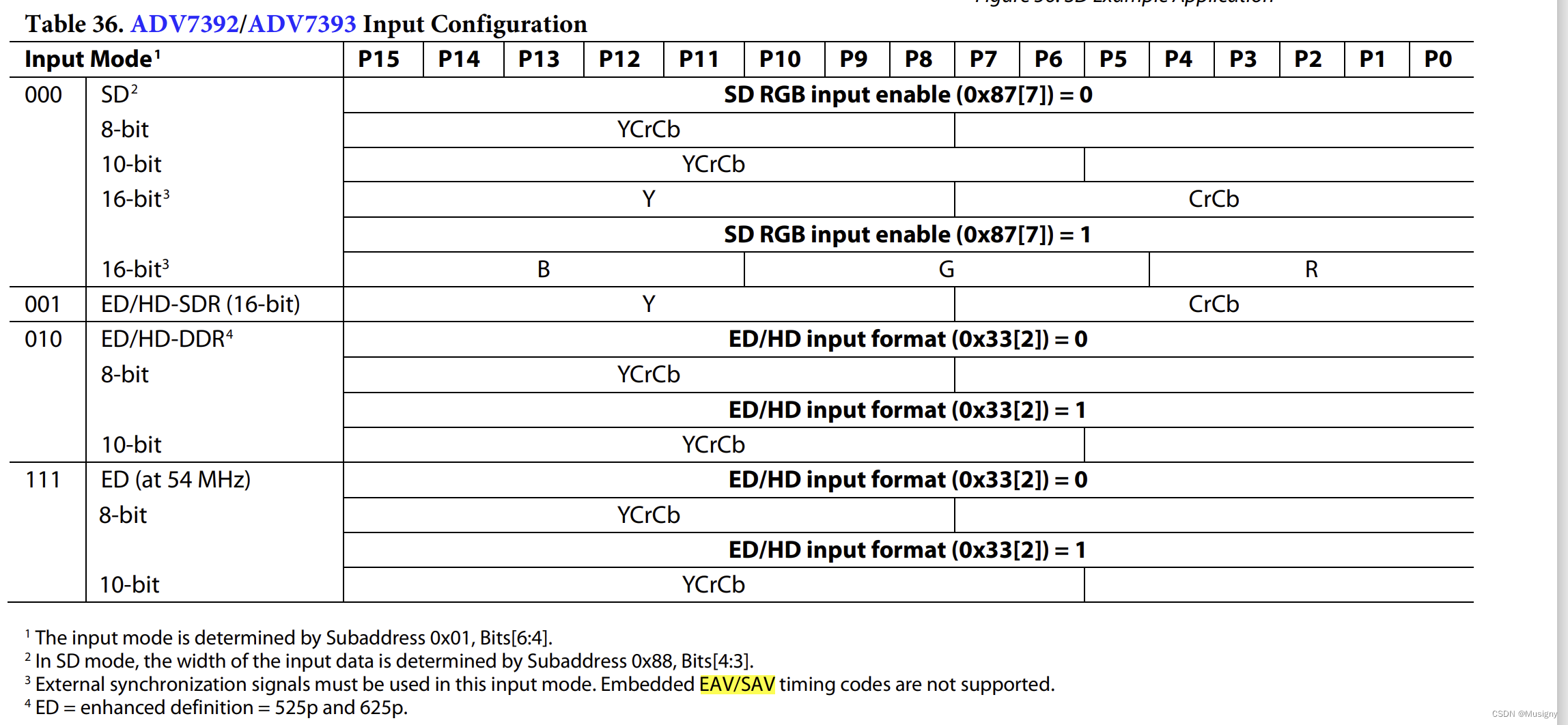

输入格式:【本次选择SD模式(包括NTSC和PAL)】在CLKIN引脚上必须提供27mhz时钟信号。如果需要,可以在HSYNC和VSYNC引脚上提供外部同步信号。嵌入式EAV/SAV时序代码也支持8位和10位模式。 使用子地址0x01, Bits[6:4]选择所需的输入模式。

输入配置寄存器{8'hd4, 8'h01, 8'h11}

-

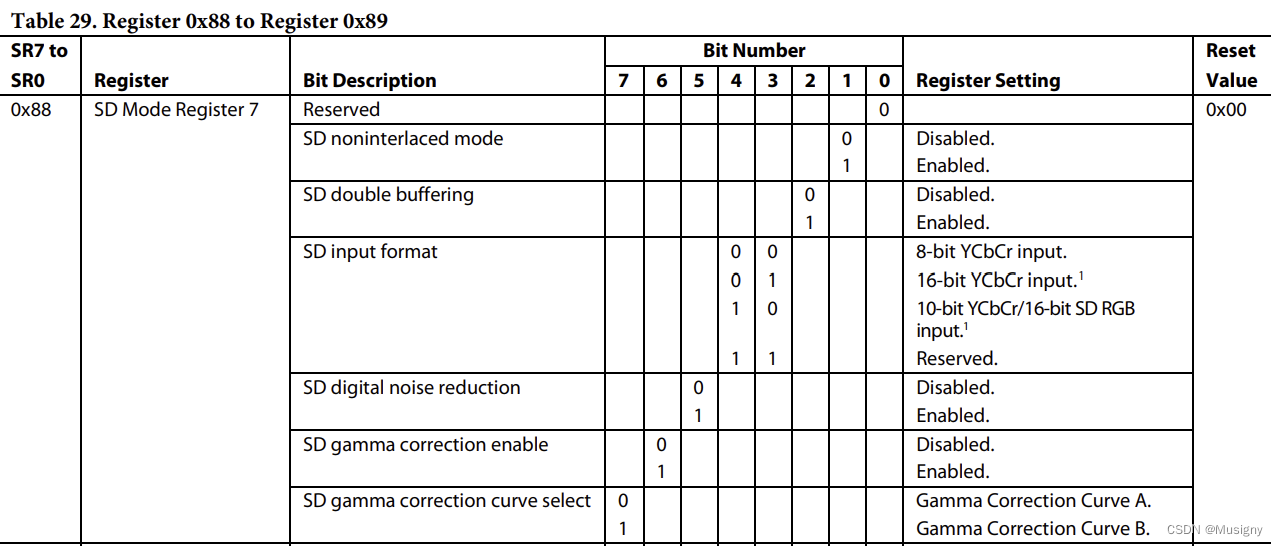

输入数据宽度:【本次选用10-bit 4:2:2 YCrCb 数据输入】该输入模式下,将交错像素数据输入引脚P15至引脚P6,引脚P6为LSB。支持ITURBT.601/656输入标准。颜色编码方式见其他博文。

输入数据宽度寄存器{8'hd4, 8'h88, 8'h10}

-

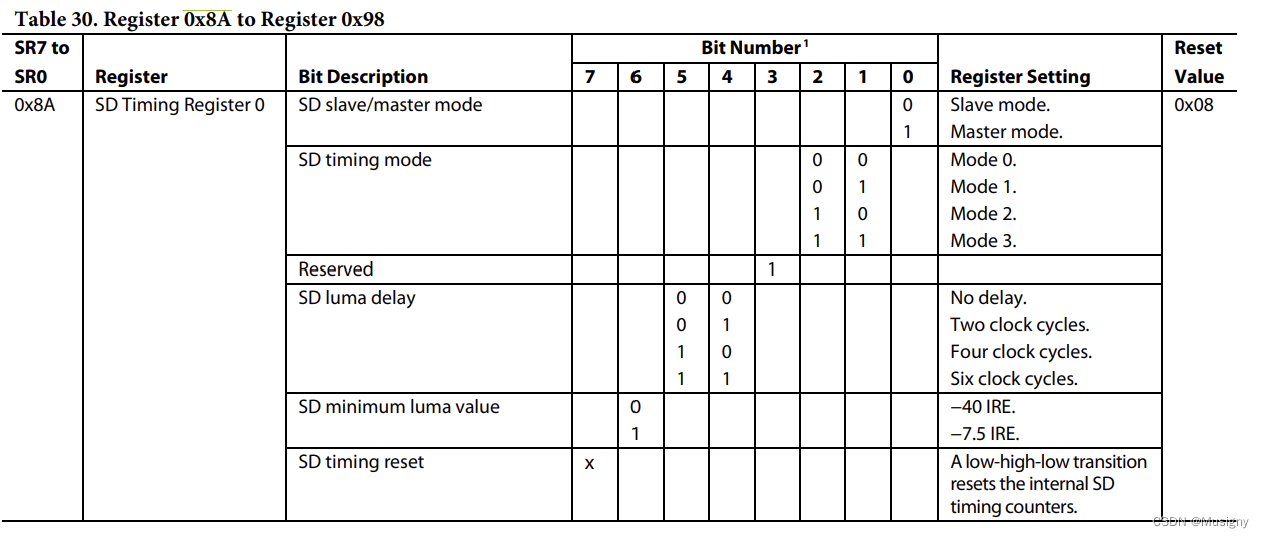

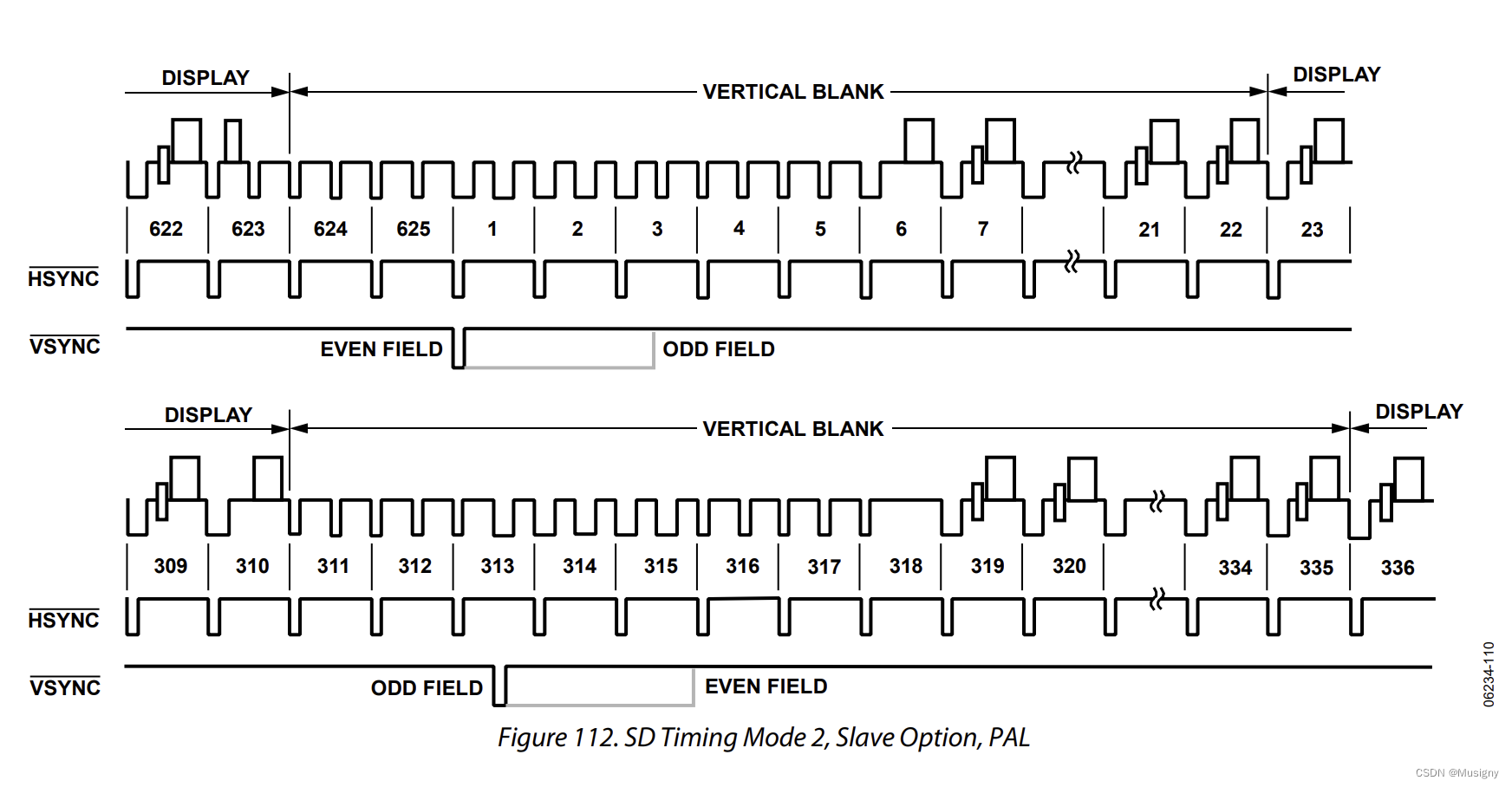

时序输入方式:该系列器件均支持式EAV/SAV时序码、外部视频同步信号以及I2C、通信协议。【本次选择使用HSYNC和VSYNC信号,标清从机模式2】在这种模式下,ADV7390/ADV7391/ADV7392/ADV7393接受水平和垂直同步信号。同时HSYNC和VSYNC输入的低跃迁表示奇数字段的开始。当HSYNC为高时,VSYNC低转换表示偶数字段的开始。ADV7390/ADV7391/ADV7392/ADV7393根据cir -624标准的要求自动清空所有正常空白行。HSYNC和VSYNC分别在HSYNC和VSYNC引脚上输入。

标清时序寄存器0{8'hd4, 8'h8A, 8'h0C}

时序图如下所示。

视频输出相关时序图可见其他博文,

视频输出相关时序图可见其他博文,

附一个别人的代码在文后。 -

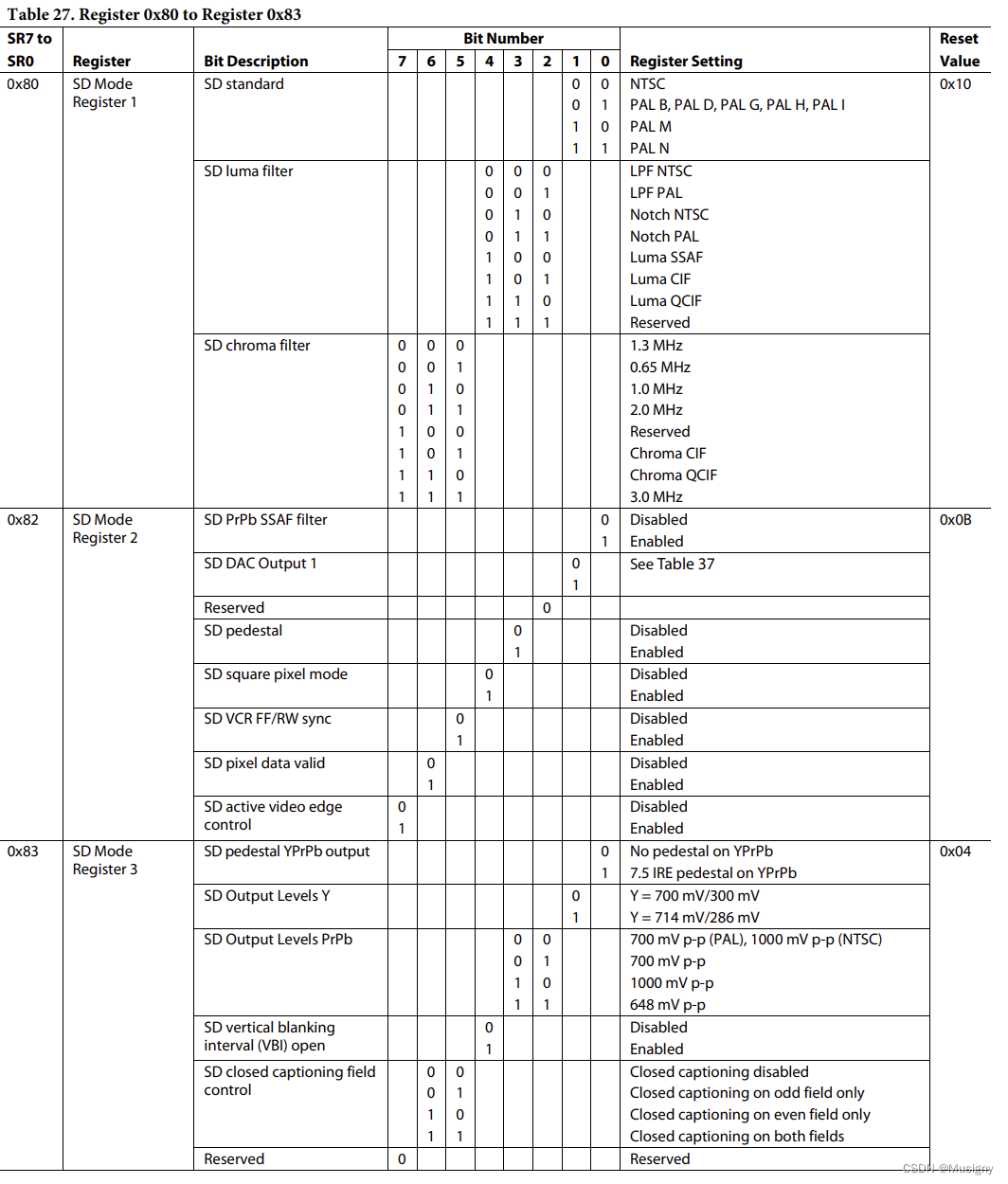

输出色彩空间:【本次选用CVBS/Y-C】

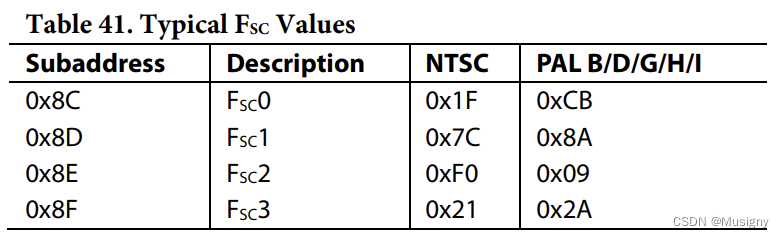

寄存器代码配置{8'hd4, 8'h8C, 8'hCB} {8'hd4, 8'h8D, 8'h8A} {8'hd4, 8'h8E, 8'h09} {8'hd4, 8'h8F, 8'h2A}

-

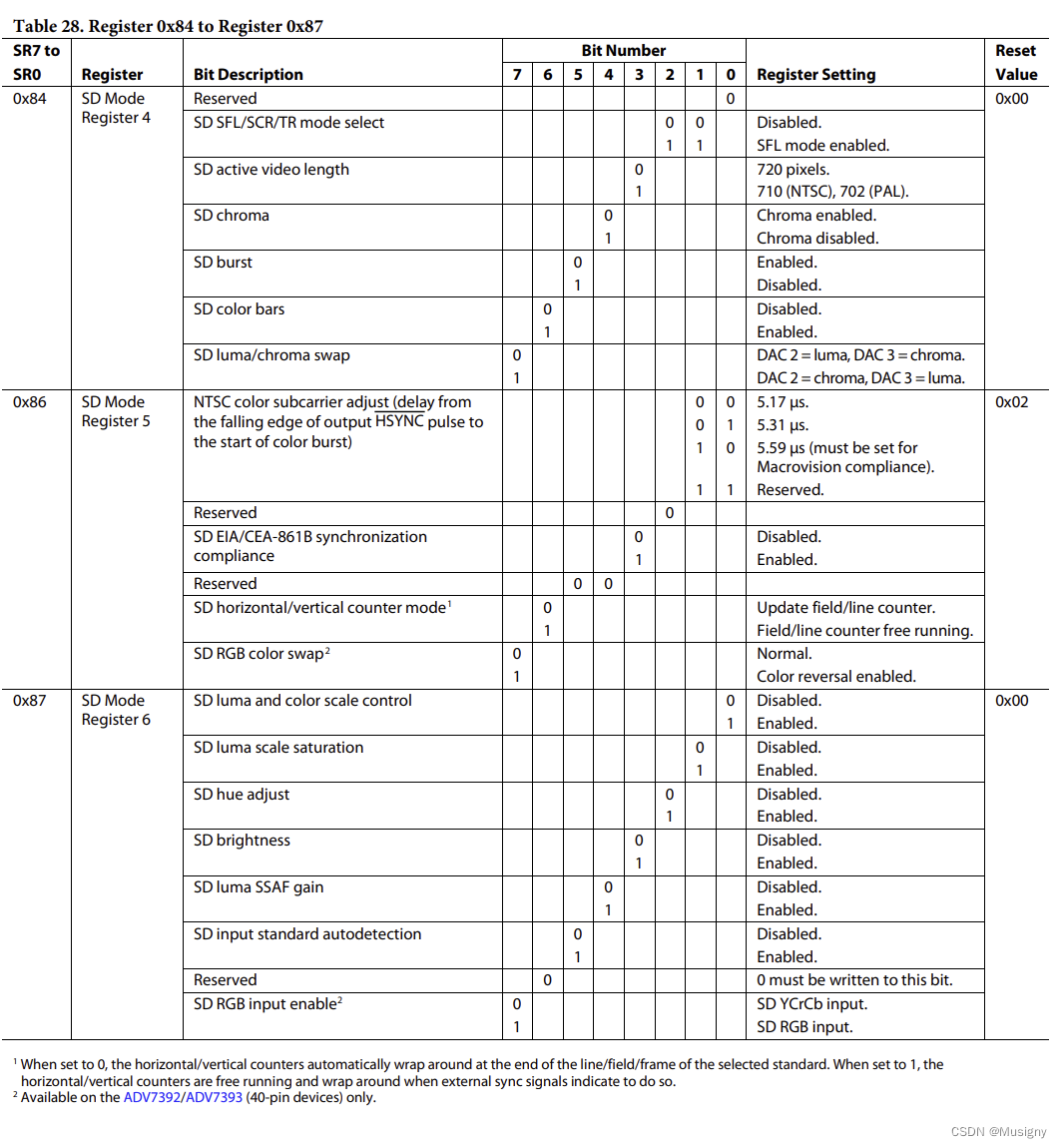

标清副载波频率控制:【本次不选用】在副载波频率锁定(SFL)模式下(子地址0x84位[2:1] = 11),

ADV739x可用于锁定外部视频源。副载波频率寄存器值被分割为4个FSC寄存器值,如上例所示。这四个副载波频率寄存器必须按顺序更新,从副载波频率寄存器0开始,至副载波频率寄存器3结束。只有在ADV739x收到最后一个副载波频率寄存器字节后,副载波频率才会更新。必须禁用标清输入标准自动检测特性。

-

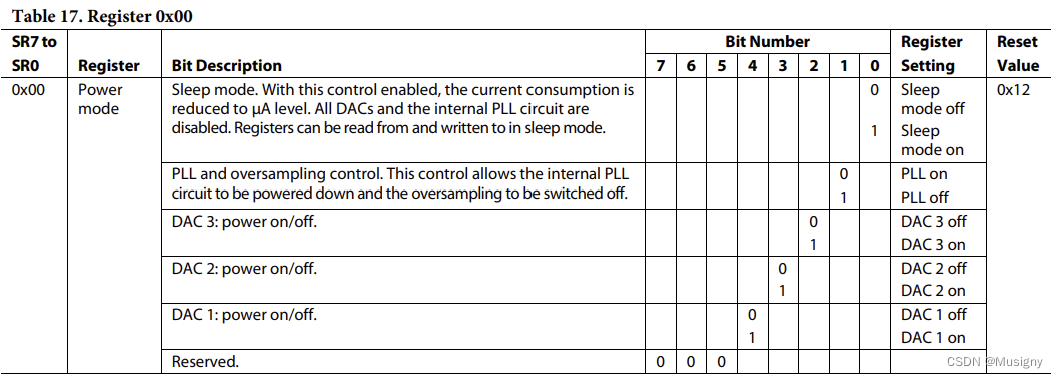

其他:

功耗模式寄存器{8'hd4, 8'h8C, 8'hCB}

标清模式寄存器{8'hd4, 8'h80, 8'h11} {8'hd4, 8'h82, 8'h0B} {8'hd4, 8'h83, 8'h04} {8'hd4, 8'h84, 8'h00} {8'hd4, 8'h86, 8'h02} {8'hd4, 8'h87, 8'h00} {8'hd4, 8'h88, 8'h10} {8'hd4, 8'h89, 8'h00}(table37?没看懂)

(其中default设置的寄存器可以不声明赋值)

module pal_d_sync(

input reset_l,

input clk,

output sync, //行同步信号

output reg blank,

output reg vsync, //场同步信号

output reg odd_even_flag

);

parameter CLK_FREQ = 13.5;

parameter DW = 16;

parameter VALID_HLEN = 640;//视频尺寸640*512

parameter VALID_VLEN = 512;

parameter H_TOTAL = 864;

parameter H_SYNC = 63;

parameter H_BP = 76;

parameter H_FP = 23;

parameter H_ACT = 702;

parameter H_HALF = 432;

parameter H_SYNC_HALF = 32;

parameter H_START = H_SYNC + H_BP + 30;

parameter H_END = H_START + VALID_HLEN;

parameter V_TOTAL = 625;

parameter V_HALF = 313;

parameter V_START = 38;

parameter V_END = V_START + ((VALID_VLEN >> 1));

parameter H_MAX = ((H_TOTAL - 1));

parameter V_MAX = V_TOTAL;

reg [9:0] h_cnt;

reg [9:0] v_cnt;

reg normal_sync;

reg v_sync;

reg v_sync1;

reg v_sync2;

reg v_sync3;

//horizon counter

always @(posedge clk or negedge reset_l)

if (((~(reset_l))) == 1'b1)

h_cnt <= {10{1'b0}};

else

begin

if (h_cnt == H_MAX)

h_cnt <= #1 {10{1'b0}};

else

h_cnt <= #1 h_cnt + 10'b0000000001;

end

//vertical counter

always @(posedge clk or negedge reset_l)

if (((~(reset_l))) == 1'b1)

v_cnt <= 10'b0000000000;

else

begin

if (h_cnt == H_MAX)

begin

if (v_cnt == V_MAX)

v_cnt <= #1 10'b0000000001;

else

v_cnt <= #1 v_cnt + 10'b0000000001;

end

end

always @(posedge clk or negedge reset_l)

if (((~(reset_l))) == 1'b1)

normal_sync <= 1'b1;

else

begin

if ((v_cnt >= 10'b0000000110 & v_cnt <= 10'b0100110110) | (v_cnt >= 10'b0100111111 & v_cnt <= 10'b1001101110))

begin

if (h_cnt == 10'b0000000000)

normal_sync <= #1 1'b0;

else if (h_cnt == ((H_SYNC - 1)))

normal_sync <= #1 1'b1;

end

else

normal_sync <= #1 1'b1;

end

always @(posedge clk or negedge reset_l)

if (((~(reset_l))) == 1'b1)

v_sync <= 1'b1;

else

begin

if (v_cnt == 10'b0000000100 | v_cnt == 10'b0000000101 | v_cnt == 10'b0100110111 | v_cnt == 10'b0100111000 | v_cnt == 10'b0100111100 | v_cnt == 10'b0100111101 | v_cnt == 10'b1001110000 | v_cnt == 10'b1001110001)

begin

if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1)))

v_sync <= #1 1'b0;

else if (h_cnt == ((H_SYNC_HALF - 1)) | h_cnt == ((H_HALF + H_SYNC_HALF - 1)))

v_sync <= #1 1'b1;

end

else

v_sync <= #1 1'b1;

end

always @(posedge clk or negedge reset_l)

if (((~(reset_l))) == 1'b1)

v_sync1 <= 1'b1;

else

begin

if (v_cnt == 10'b0000000001 | v_cnt == 10'b0000000010 | v_cnt == 10'b0100111010 | v_cnt == 10'b0100111011)

begin

if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1)))

v_sync1 <= #1 1'b0;

else if (h_cnt == ((H_HALF - H_SYNC - 1)) | h_cnt == ((H_TOTAL - H_SYNC - 1)))

v_sync1 <= #1 1'b1;

end

else

v_sync1 <= #1 1'b1;

end

always @(posedge clk or negedge reset_l)

if (((~(reset_l))) == 1'b1)

v_sync2 <= 1'b1;

else

begin

if (v_cnt == 10'b1001101111)

begin

if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1)))

v_sync2 <= #1 1'b0;

else if (h_cnt == ((H_SYNC - 1)) | h_cnt == ((H_HALF + H_SYNC_HALF - 1)))

v_sync2 <= #1 1'b1;

end

else if (v_cnt == 10'b0000000011)

begin

if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1)))

v_sync2 <= #1 1'b0;

else if (h_cnt == ((H_HALF - H_SYNC - 1)) | h_cnt == ((H_HALF + H_SYNC_HALF - 1)))

v_sync2 <= #1 1'b1;

end

else if (v_cnt == 10'b0100111001)

begin

if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1)))

v_sync2 <= #1 1'b0;

else if (h_cnt == ((H_SYNC_HALF - 1)) | h_cnt == ((H_TOTAL - H_SYNC - 1)))

v_sync2 <= #1 1'b1;

end

else

v_sync2 <= #1 1'b1;

end

always @(posedge clk or negedge reset_l)

if (((~(reset_l))) == 1'b1)

v_sync3 <= 1'b1;

else

begin

if (v_cnt == 10'b0100111110)

begin

if (h_cnt == 10'b0000000000)

v_sync3 <= #1 1'b0;

else if (h_cnt == ((H_SYNC_HALF - 1)))

v_sync3 <= #1 1'b1;

end

else

v_sync3 <= #1 1'b1;

end

assign sync = normal_sync & v_sync1 & v_sync2 & v_sync3 & v_sync;

always @(posedge clk or negedge reset_l)

if (((~(reset_l))) == 1'b1)

blank <= 1'b0;

else

begin

if ((v_cnt >= V_START & v_cnt <= ((V_END - 1))) | (v_cnt >= ((V_START + V_HALF)) & v_cnt <= ((V_END + V_HALF - 1))))

begin

if (h_cnt == H_START)

blank <= #1 1'b1;

else if (h_cnt == H_END)

blank <= #1 1'b0;

end

else

blank <= 1'b0;

end

always @(posedge clk or negedge reset_l)

if (((~(reset_l))) == 1'b1)

begin

vsync <= 1'b1;

odd_even_flag <= 1'b0;

end

else

begin

if ((v_cnt <= 10'b0000000101 | v_cnt >= 10'b1001101111))

vsync <= #1 1'b1;

else

vsync <= #1 1'b0;

if (v_cnt <= 10'b0100111001 & v_cnt >= 10'b0000000101)

odd_even_flag <= #1 1'b0;

else

odd_even_flag <= #1 1'b1;

end

endmodule

推荐参考论文:

高阳,王代华,王晓楠.基于PAL的弹载图像采集系统设计.科学技术与工程,2017,17(14):196-202.

本文详细解释了ADV7392/ADV7393视频处理芯片的配置方法,涉及SD模式选择、时钟输入要求、EAV/SAV时序代码、10-bit数据输入、标清时序寄存器设置等,旨在帮助工程师理解和实现相关硬件接口的配置。

本文详细解释了ADV7392/ADV7393视频处理芯片的配置方法,涉及SD模式选择、时钟输入要求、EAV/SAV时序代码、10-bit数据输入、标清时序寄存器设置等,旨在帮助工程师理解和实现相关硬件接口的配置。

1755

1755

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?