28034的SCI没有接入DMA总线,不过它的收发都有4级的FIFO,在一定程度上也能够缓解cpu的压力。

本文的设计思想如下:

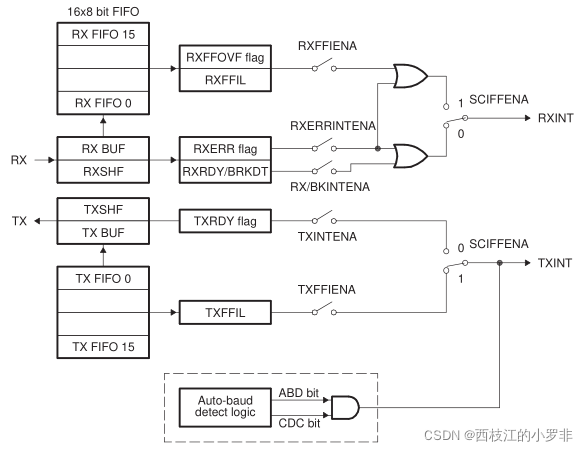

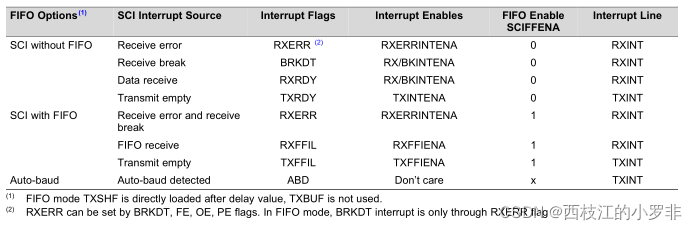

接收:通过中断的方式,4级FIFO满后在中断里将RXDATA出栈。不过就存在这种情况,发送端发出的数据未必能填满4级FIFO,然而此时配置的是4级FIFO触发中断,所以这种情况下中断无法及时地触发。怎么办?

本文的做法是在主程序下循环读取FIFO。这样就可以确保在数据高速传输时,通过中断和主程序及时和有效地接收到总线的数据。(不过当总线波特率较低时可能中断是几乎不会被触发^_^)

发送:发送一样用到中断的方式。首先发送的中断在初始化的时候是不会被触发的,当数据需要发送的时候,在完成第一次的TXFIFO拷贝之后,发送中断将会被使能。假如此时的数据还没有发送完成,那么在发送中断到来时,剩下的数据将在发送中断里面进行拷贝,如此往复,直到所有数据都完成了发送,在最后一次中断产生时,再次把发送的中断去使能&#x

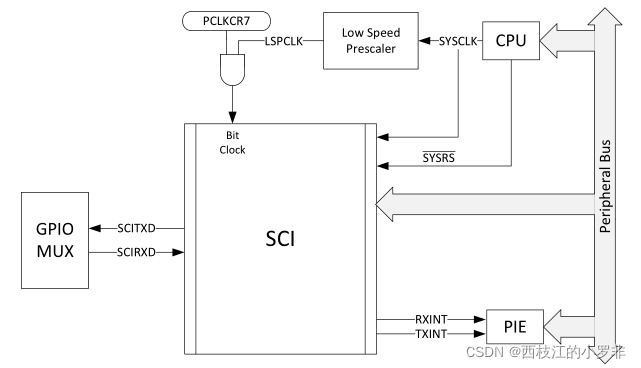

本文介绍了基于TMS320F28034微控制器的SCI(Serial Communication Interface)技术,重点讨论了在没有DMA支持的情况下,如何利用4级FIFO来减轻CPU负担。对于接收,采取中断和主程序循环读取FIFO的结合方式确保数据高效接收。发送则采用中断触发,首次拷贝数据后启用发送中断,中断处理剩余数据,最后在数据发送完毕时关闭发送中断,防止循环触发。

本文介绍了基于TMS320F28034微控制器的SCI(Serial Communication Interface)技术,重点讨论了在没有DMA支持的情况下,如何利用4级FIFO来减轻CPU负担。对于接收,采取中断和主程序循环读取FIFO的结合方式确保数据高效接收。发送则采用中断触发,首次拷贝数据后启用发送中断,中断处理剩余数据,最后在数据发送完毕时关闭发送中断,防止循环触发。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?