一、IP核简介

PLL锁相环

FIFO

RAM

ROM

altera公司使用的是模拟锁相环,相比于数字锁相环,其输出的信号稳定度高、相位连续可调、延时连续可调。缺点是当温度过高或者电磁辐射过强的时候会失锁

锁相环是一个反馈系统

PLL(Phase Locked Loop,即锁相环)是最常用的IP核之一,其性能强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟。

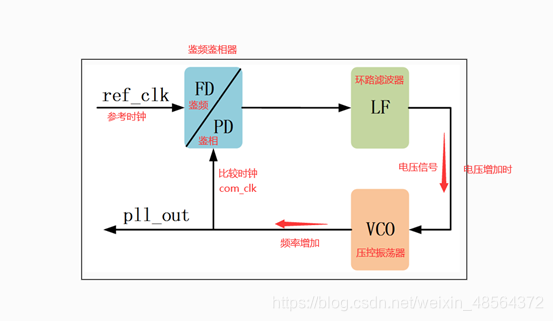

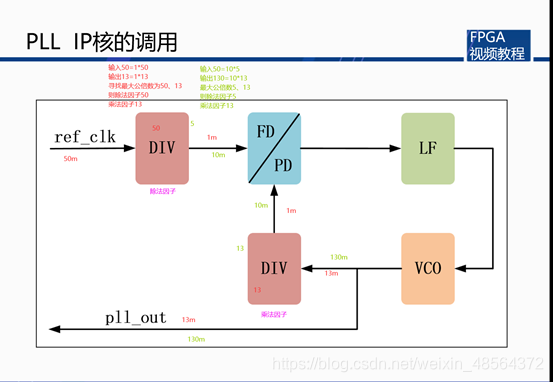

1、PLL的基本工作原理

鉴频鉴相器:主要比较参考时钟与比较时钟的频率核相位的差异

环路滤波器:用于控制噪声的带宽,滤掉高频噪声,使得波形更加平滑,输出一个电压信号

压控振荡器:输入的电压信号越高,则输出的信号的频率越高。

当参考时钟与比较时钟频率相等时,鉴频鉴相器输出的0,表示参考时钟与比较时钟的频率相同

当参考时钟大于比较时钟,鉴频鉴相器输出一个变大的成正比的值

当参考时钟小于比较时钟,鉴频鉴相器输出一个变小的成正比的值

假设参考时钟的频率50m,而压控振荡器的基准频率为10m,此时的参考时钟大于比较时钟,则鉴频鉴相器输出一个变大的成正比的值,这个值输入到环路滤波器中,环路滤波器输出的电压信号增强,增强的电压信号输入到压控振荡器中,压控振荡器输出一个升高的频率,这个频率大于10m,因此这样不断的循环,直到比较时钟为50m。pll_out最终输出的为50m,这就是PLL的基本工作原理。

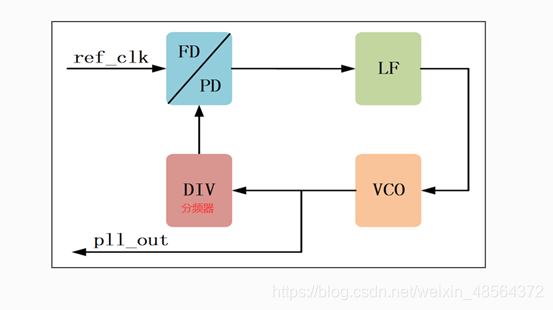

2、PLL的倍频

PLL的倍频与基本原理图相似,只是在比较信号处多了一个分频器,假设DIV是一个2倍频,当比较时钟与参考时钟都是50m时,则pll_out输出的是一个100m,根据DIV倍频的倍数就可以实现输出的任意倍频

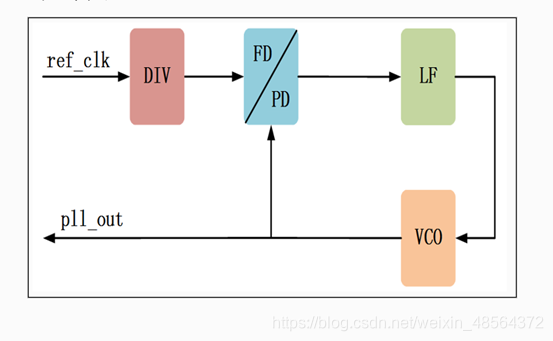

3、PLL的分频

与倍频的原理相似,根据DIV的分频倍数就可以实现输出的频率

源同步:数据和时钟来自同一信号源

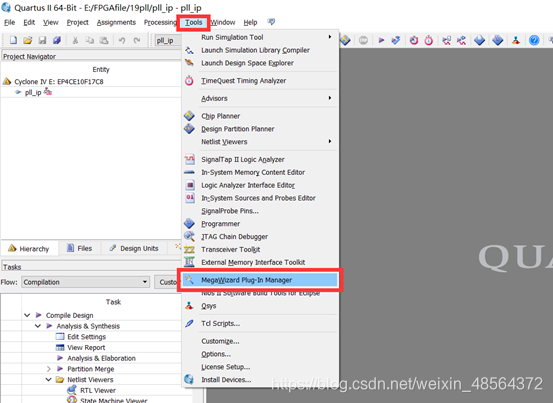

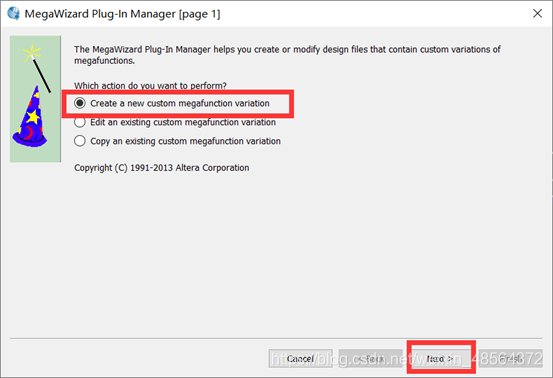

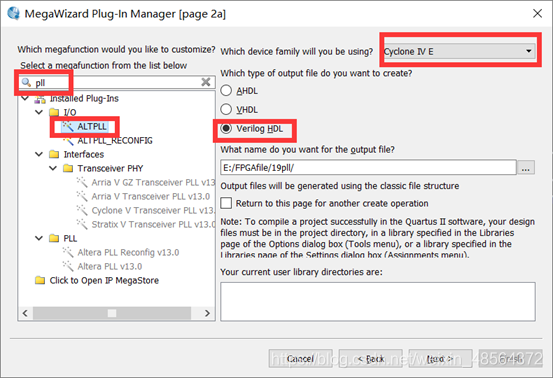

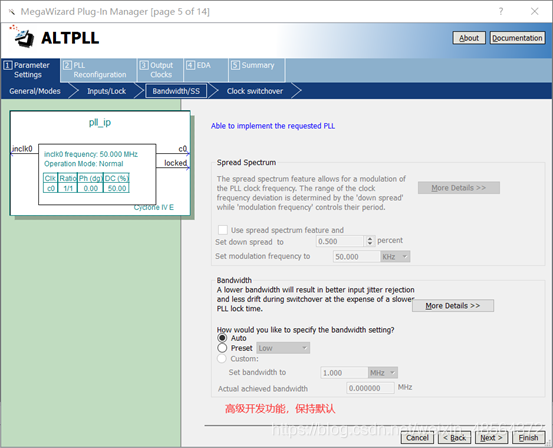

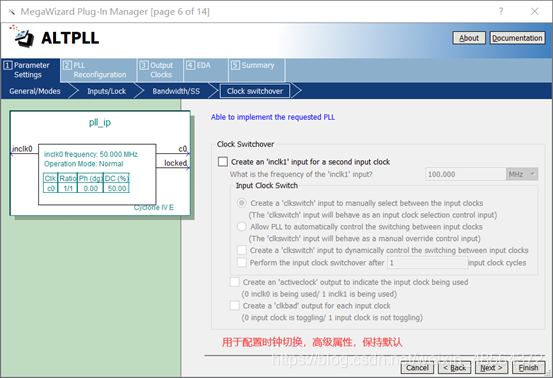

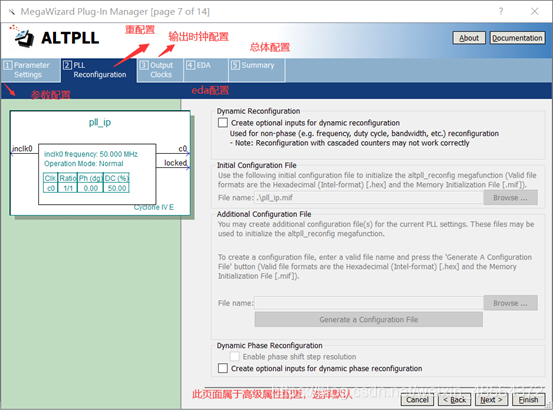

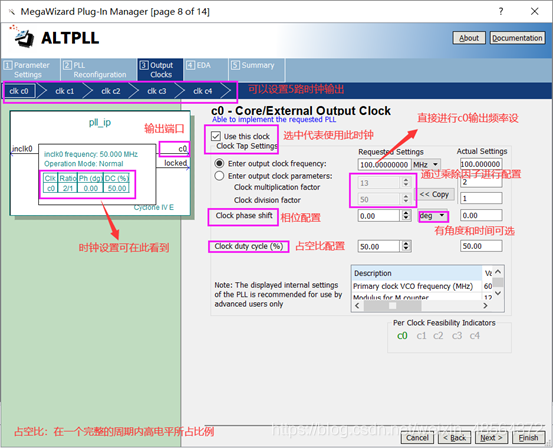

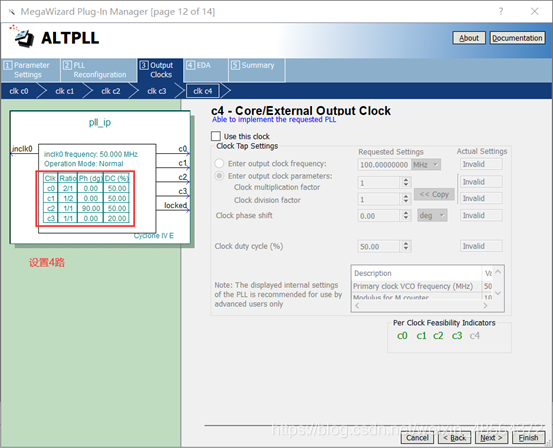

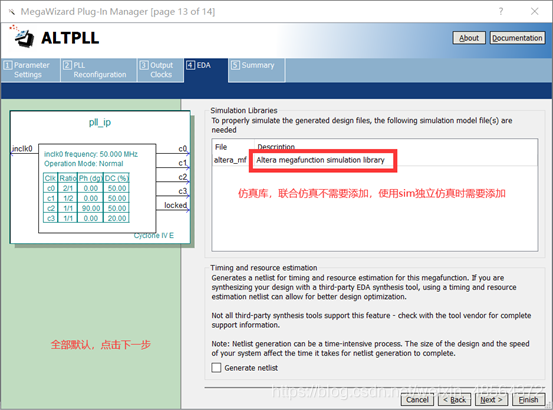

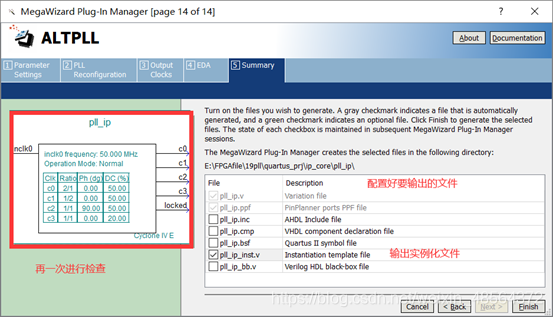

二、IP核的配置

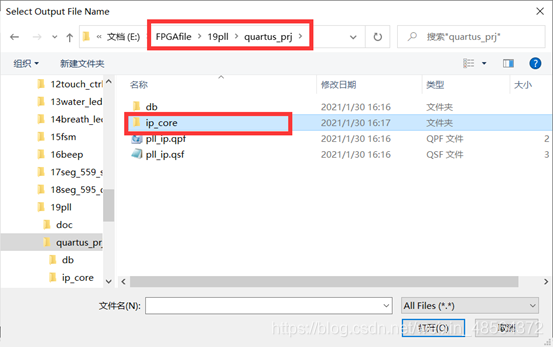

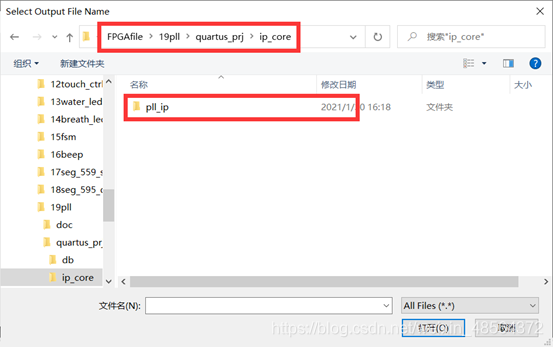

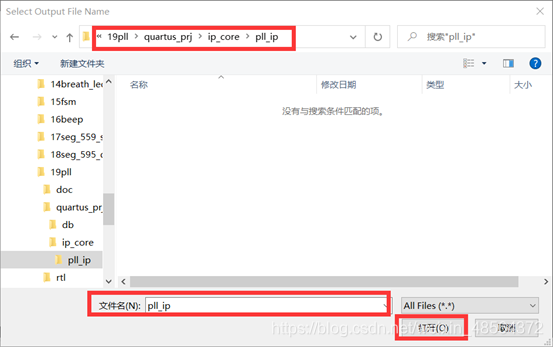

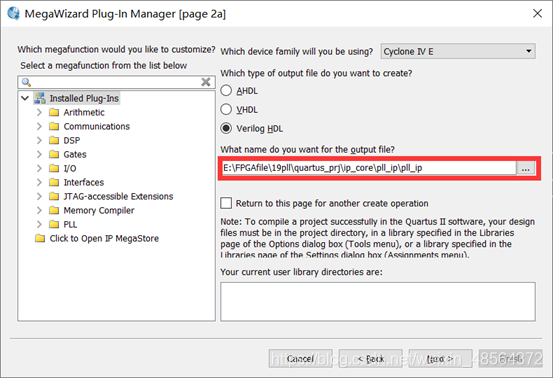

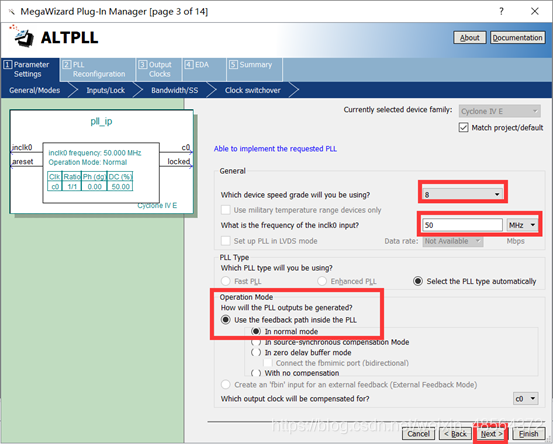

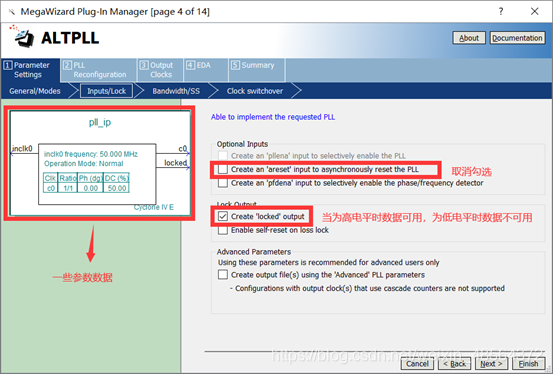

在工程里面新建一个文件夹,用来存放多个ip核,再建一个文件夹用来放锁相环ip核

本文详细介绍了PLL锁相环的基本工作原理及其在FPGA中的应用,包括PLL的倍频与分频操作,并探讨了如何配置IP核。

本文详细介绍了PLL锁相环的基本工作原理及其在FPGA中的应用,包括PLL的倍频与分频操作,并探讨了如何配置IP核。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?