问题:

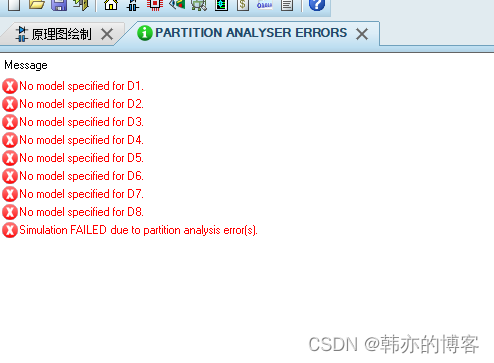

当我画好电路图后,开始进行仿真后,就出现了如图所示,这么多错误,那一刻,我瞬间有了放弃学习单片机的想法。沮丧过后,还是得从现实出发,寻找错误点,首先,我检查了自己电路图等等,以及最小系统的画法,并没有发现任何错误,一切正常。网上搜索后,有部分博主表示可能是元器件没有添加PCB模型,我一看,还真是:

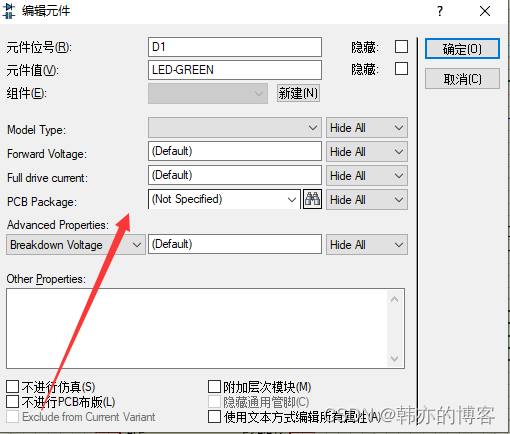

于是连忙根据自己的元器件添加了PCB模型:

但事实上,添加完后仿真,依然没有任何变化。

最终解决:

这让我开始思考这么多元器件,为什么都出现了一样的问题,是不是他们元器件属性方便有问题,观察一段时间后,终于找到了错误所在:

实际上是元器件的text被我删除掉,导致出错:

在使用Proteus进行51单片机电路仿真时遇到'No model specified for D1'和'Simulation FAILED due to partition analysis error(s)'的问题。经过检查电路图和添加PCB模型后问题仍未解决。最终发现是由于删除了元器件的text属性导致,修复text后,仿真成功。

在使用Proteus进行51单片机电路仿真时遇到'No model specified for D1'和'Simulation FAILED due to partition analysis error(s)'的问题。经过检查电路图和添加PCB模型后问题仍未解决。最终发现是由于删除了元器件的text属性导致,修复text后,仿真成功。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?