1、uvm寄存器相关的一些操作

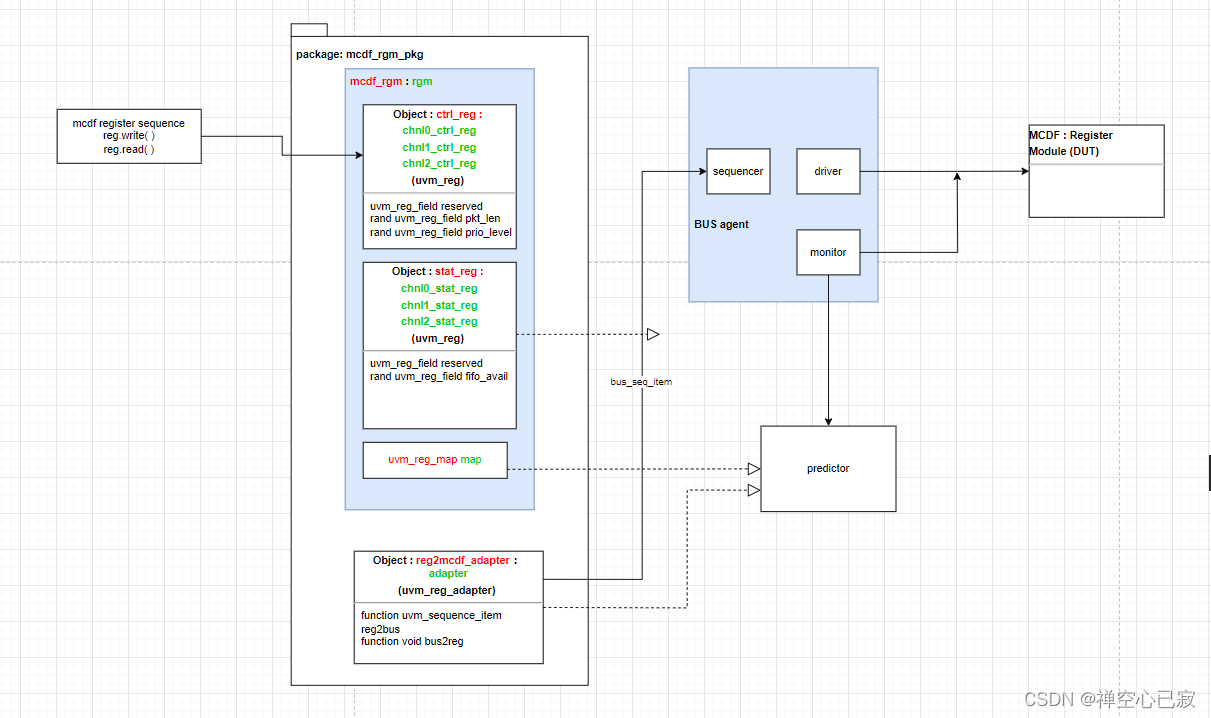

mcdf_rgm模块包括寄存器模块和map

mcdf_rgm模块包括寄存器模块和map

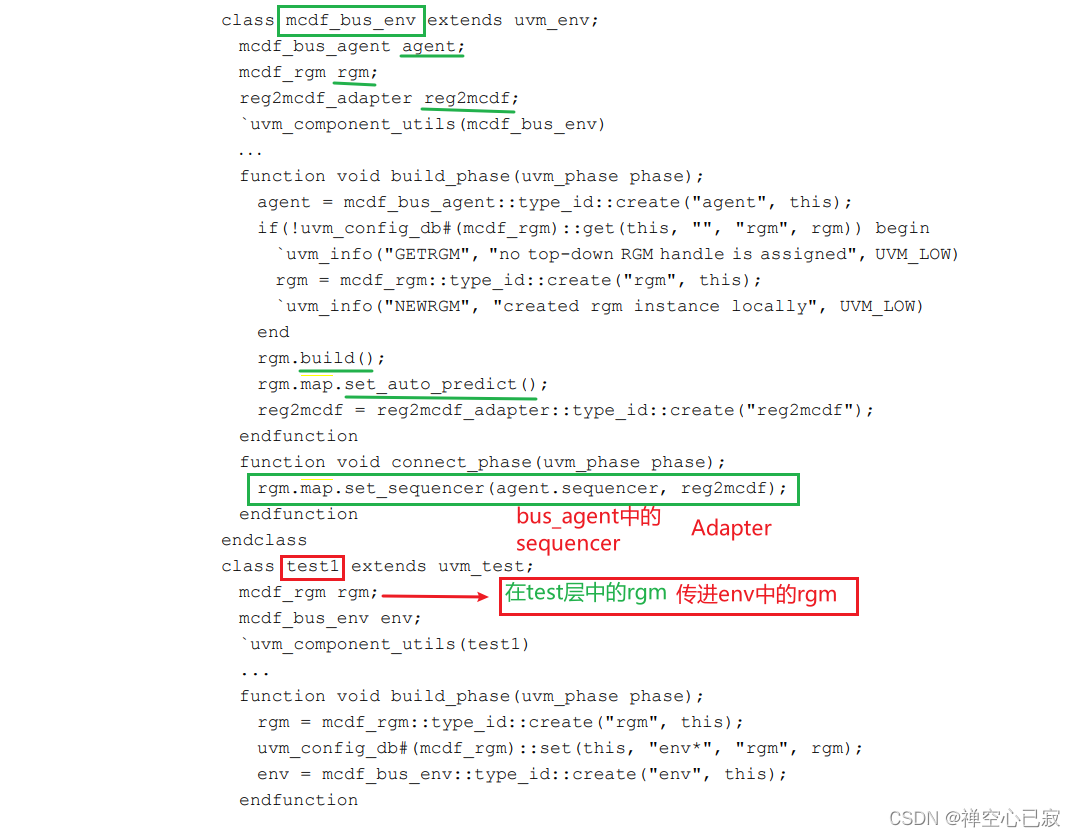

另外包括独立的adapter

二者共同是寄存器相关的,与总线UVC进行事务传递。

BUS_agent代码:

(总线UVC的实现)在漫游红皮书P410页中

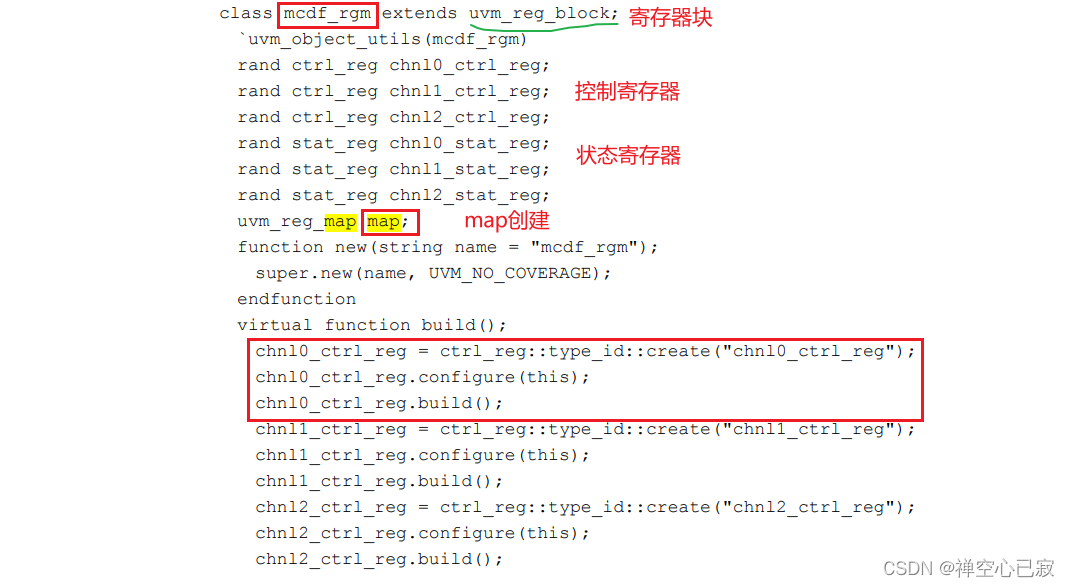

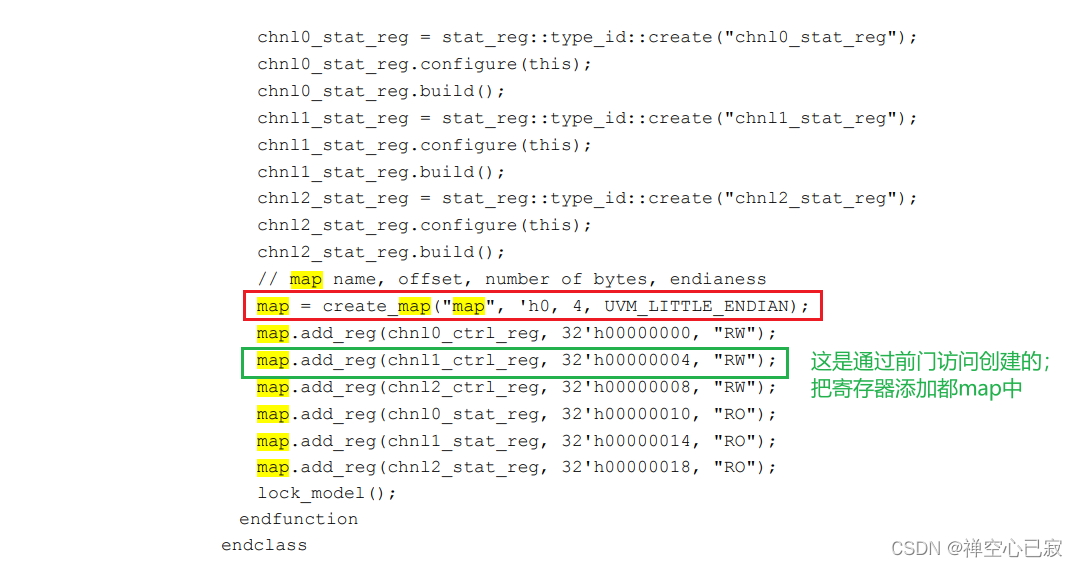

关于寄存器块:

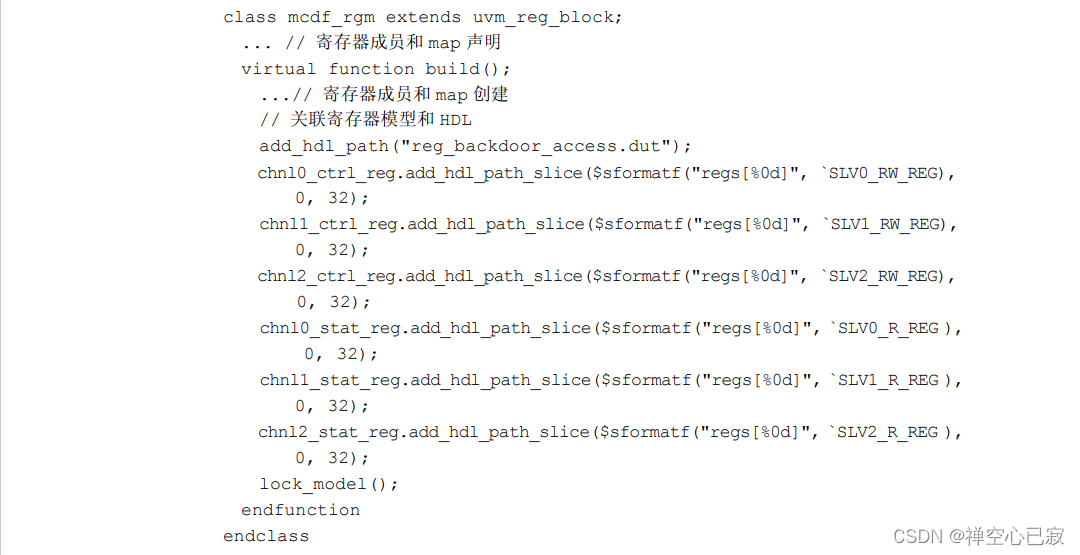

后门访问时要确保寄存器模型在建立时将各个寄存器映射到了DUT一侧的HDL路径。

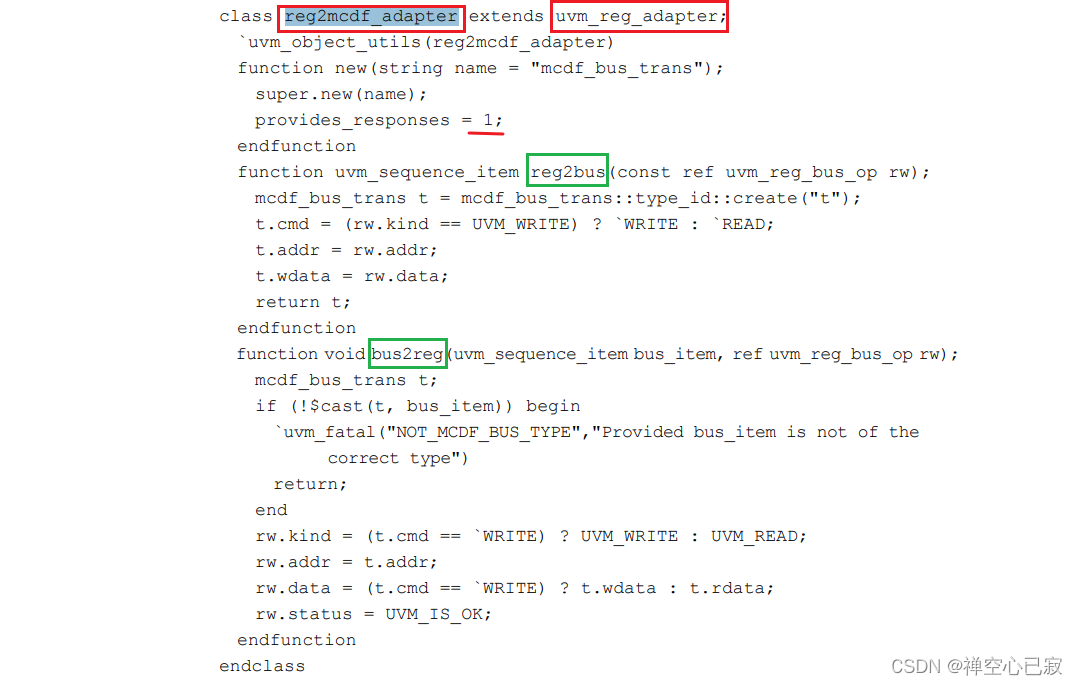

Adapter的实现:

Adapter的集成(在env中):

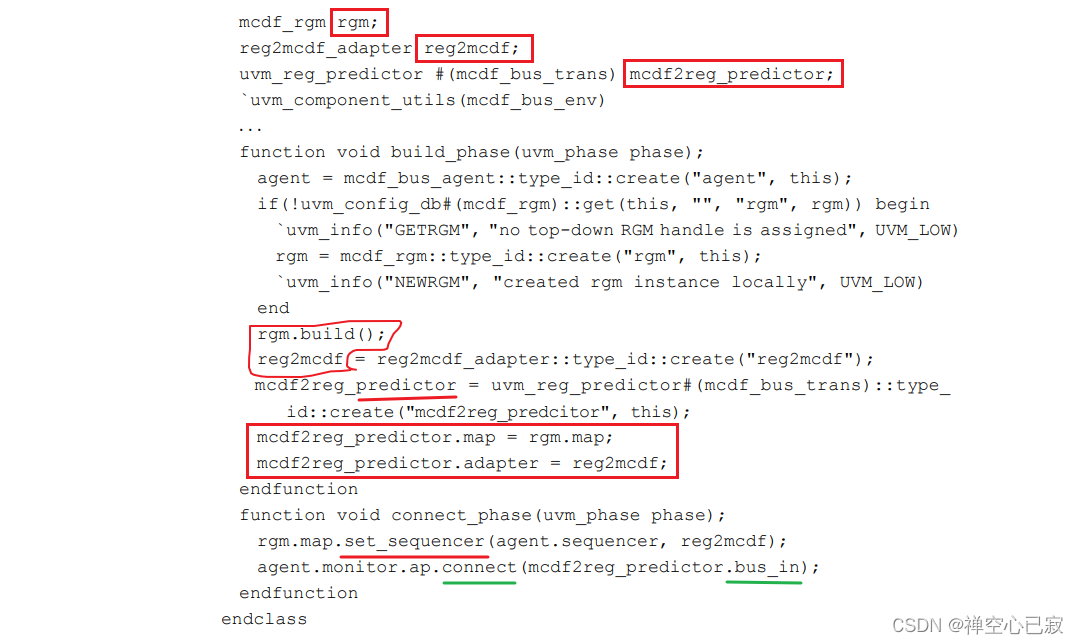

关于predictor在顶层环境中的集成:

uvm白皮书reg_predictor:

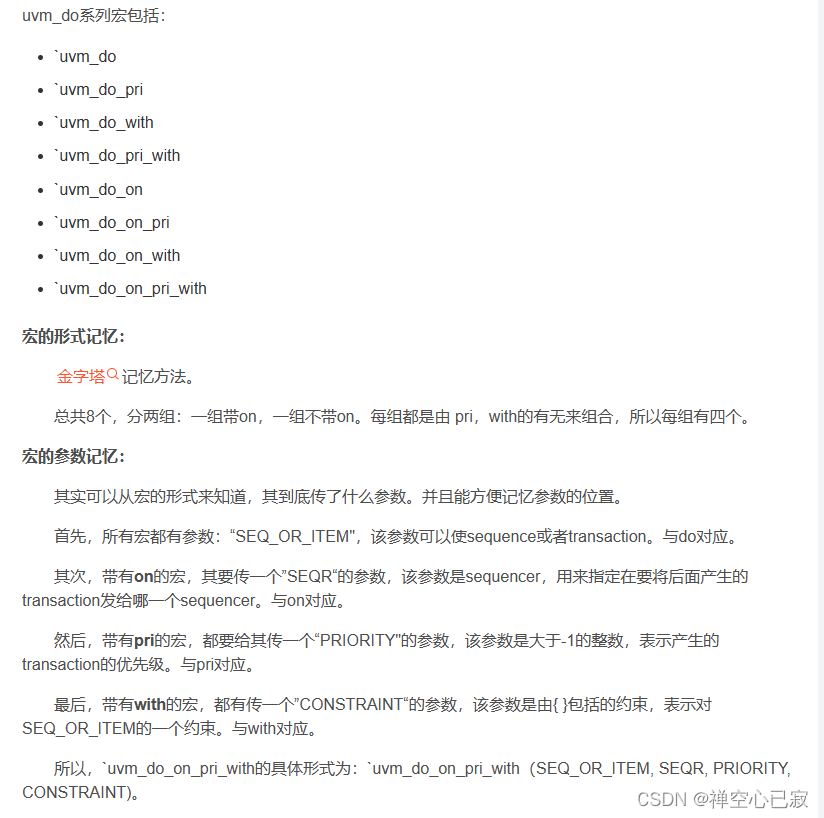

2、uvm_do系列宏

系列宏主要完成三个步骤:

- sequence或item的创建;

- sequence或item的随机化;

- sequence或item的传送;

3、m_sequencer和p_sequencer的区别

m_sequencer是sequence或sequence item的成员变量,即sequence、sequence item一旦“挂载”到某个sequencer上,那么该sequencer的句柄即被赋值给 m_sequencer (uvm_sequencer_base类)。

p_sequencer通常需要在定义sequence类时,通过宏 `uvm_declare_p_sequencer(SEQUENCER)进行声明(间接定义p_sequencer的变量)。

m_sequencer和p_sequencer均指向同一个挂载的sequencer实例,前者是父类句柄类型,后者是子类句柄类型。

4、reg_intf reg_if(.*)含义

这是一个SystemVerilog中的接口声明语句,其中reg_intf是接口类型的名称,reg_if是接口实例的名称。".*"表示将所有信号连接到接口上,即将所有信号与接口的端口一一对应连接起来。这个语句的作用是将信号与接口进行绑定,使得信号可以在接口中传输。

3215

3215

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?