问题:在使用proteus仿真STM32时,发现外部时钟启动出错导致时钟频率不对,延时函数不准。影响外设的正常使用;

解决方法:使用STM32内部时钟作为系统时钟,可以解决此问题,但是没办法使用过高的时钟频率,最高大约可以达到50Mhz左右;建议使用40MHZ;

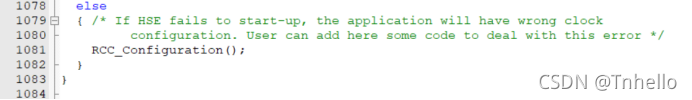

将以下函数写进,ST提供的系统时钟文件( system_stm32f10x.c)里,位置如图:

将下方函数作为,外部时钟启动出错时的解决方案,就是采用内部高速时钟

| //选择HSI作为内部时钟 void RCC_Configuration(void) { RCC_DeInit(); //重设RCC寄存器为缺省值 RCC_HSICmd(ENABLE); //使能HSI内部高速晶振 while(RCC_GetFlagStatus(RCC_FLAG_HSIRDY) == RESET); //等待使能成功 //配置AHB时钟频率与系统时钟频率一致 RCC_HCLKConfig(RCC_SYSCLK_Div1); //配置APB1低速时钟频率为AHB时钟频率的1/2 RCC_PCLK1Config(RCC_HCLK_Div2); //配置APB2高速时钟频率与AHB时钟频率一致 RCC_PCLK2Config(RCC_HCLK_Div1); //配置ADC时钟频率为APB2时钟频率的1/4 RCC_ADCCLKConfig(RCC_PCLK2_Div4); //将内部晶振时钟2分频后作为PLL时钟源,倍频系数为10(即系统时钟为40MHz) RCC_PLLConfig(RCC_PLLSource_HSI_Div2,RCC_PLLMul_10); //使能PLL(如果PLL被用于系统时钟,那么它不能被失能) RCC_PLLCmd(ENABLE); //等待指定的RCC标志位设置成功,等待PLL初始化成功 while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET); RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); //以PLL时钟作为系统时钟源 //0x00:HSI作为系统时钟 //0x04:HSE作为系统时钟 //0x08:PLL作为系统时钟 while(RCC_GetSYSCLKSource() != 0x08); //等待PLL时钟成功作为系统时钟源 } |

2021/11/16

当STM32在Proteus仿真中遇到外部时钟启动错误导致时钟频率不准确的问题,可以改用内部高速时钟(HSI)作为系统时钟源。通过配置RCC寄存器,设置HSI,然后进行系统时钟、APB时钟和ADC时钟的配置,最后启用PLL并切换到PLL时钟,确保系统时钟稳定在40MHz。这种方法虽限制了最高时钟频率,但能保证外设正常工作。

当STM32在Proteus仿真中遇到外部时钟启动错误导致时钟频率不准确的问题,可以改用内部高速时钟(HSI)作为系统时钟源。通过配置RCC寄存器,设置HSI,然后进行系统时钟、APB时钟和ADC时钟的配置,最后启用PLL并切换到PLL时钟,确保系统时钟稳定在40MHz。这种方法虽限制了最高时钟频率,但能保证外设正常工作。

3344

3344

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?