考点一:

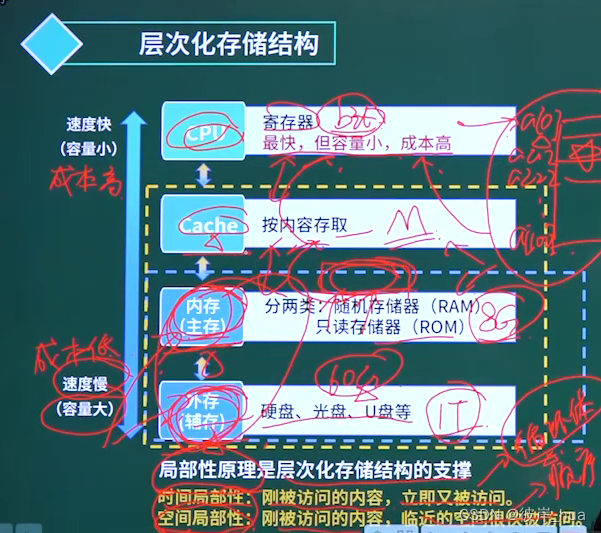

层次化存储结构:

Cache的作用是抽取内存中的数据以供CPU使用,主要作用是解决内存和CPU处理速度不匹配的问题。

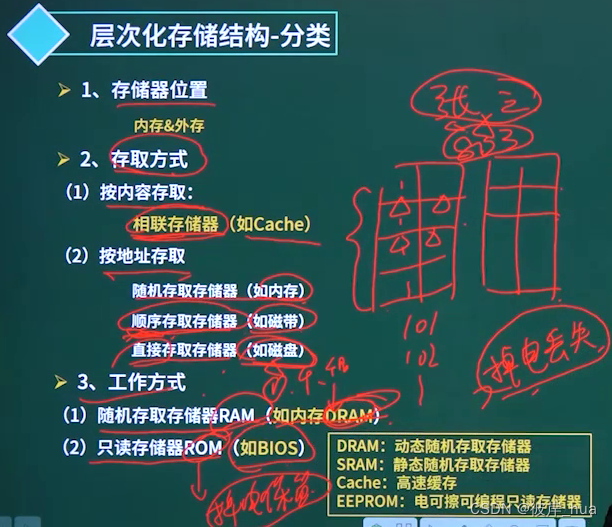

内存和外存统称为虚拟存储体系

内存、外存和Cache统称为三级存储体系

层次化存储结构-分类:

RAM是会掉电丢失(突然关机未保存的数据会丢失)

ROM则是掉电保留(突然关机数据不会丢失)

例题:

答案:C

解析:只有时间局部性和空间局部性两种。

已访问一个存储单元,接下来有可能访问附近的存储单元,这种被称为空间局部性。

当已经被访问了,不久的将来还有可能会被访问,则是时间局部性。

答案:A

解析:虚拟存储体系由主存和外存(辅存)组成。

三级存储体系由主存、外存和Cache组成。

答案:A

解析:BIOS是存储数据到主板上的,且是掉电保留数据,所以是ROM上。

CPU的寄存器、RAM都是掉电丢失数据的。

虚拟存储器是主存和外存组成。

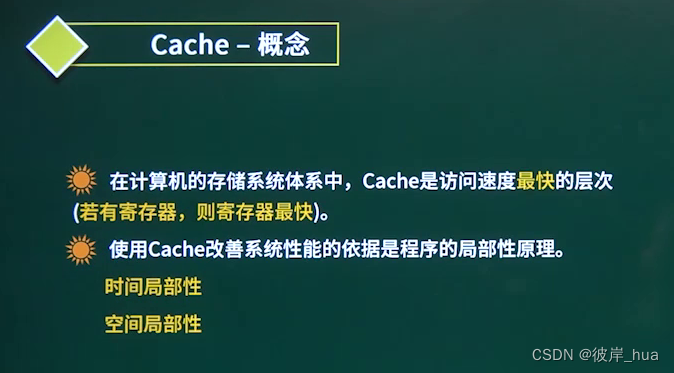

考点二:Cache

简介:

Cache是位于CPU和内存之间的,CPU(寄存器)是存储速度最快的,剩下的就是Cache主要作用处理CPU和内存之间数据处理速度不一样的问题。

局部性:

时间局部性:调用了一次之后隔一段时间会在调用一次。

空间局部性:在调用之后大概路还会调用附近的。

Cache的命中率很高,且在其中抽取数据的速度快。

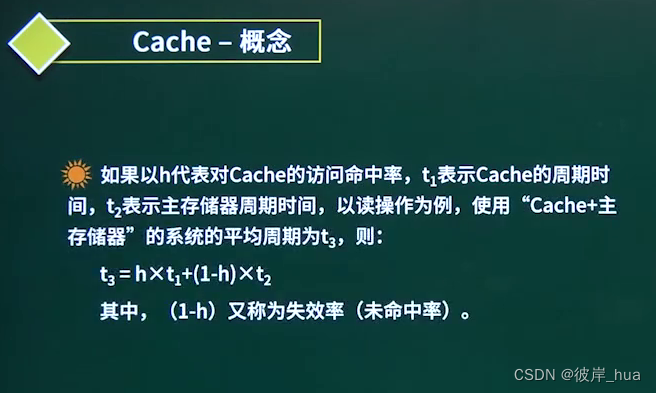

假设命中率为百分之90,Cache的周期为1秒,主存储器的周期为10秒,则平均周期t3等于0.9*1+(1-0.9)*100=10.9。

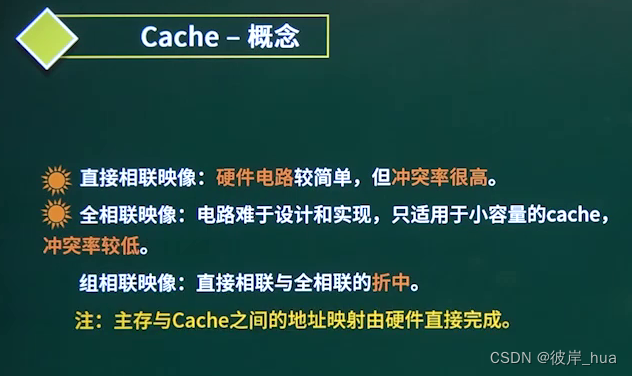

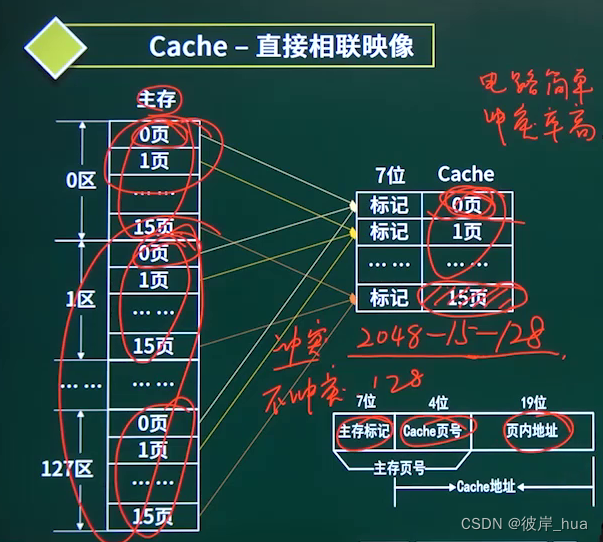

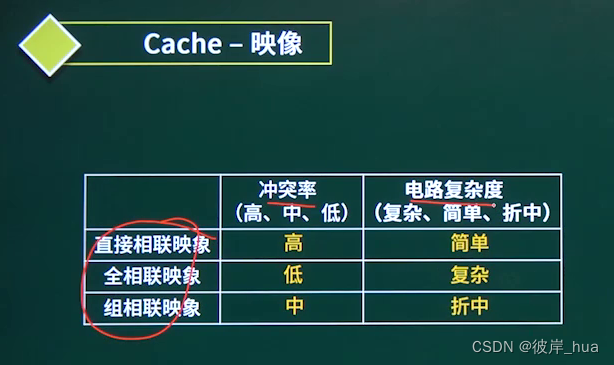

直相连:电路简单,冲突率高。

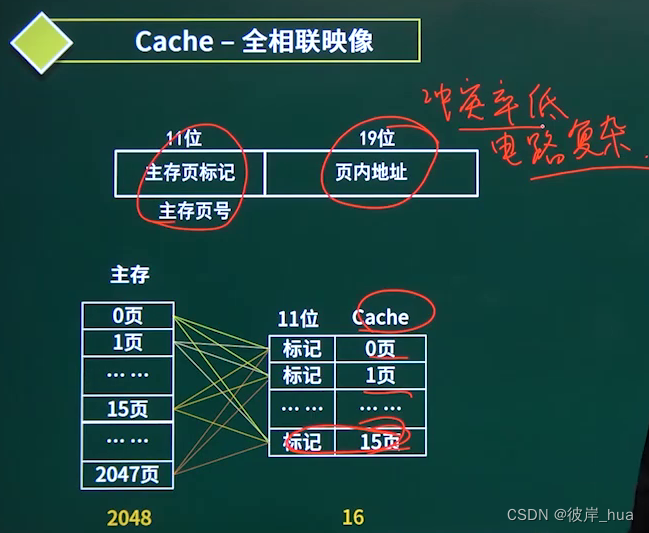

全相连:电路复杂,冲突率低。

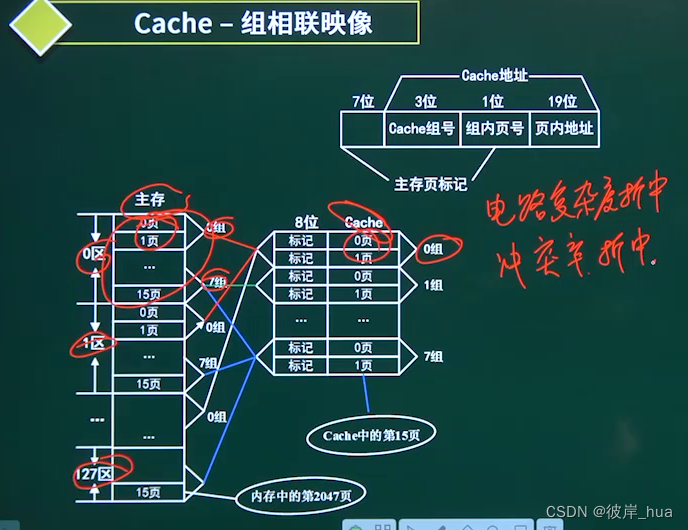

组相连:电路折中,冲突率中。

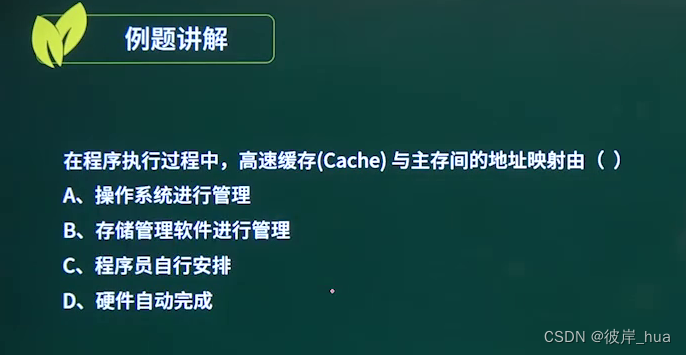

注:主存与Cache之间的地址映射由硬件直接完成。

例题:

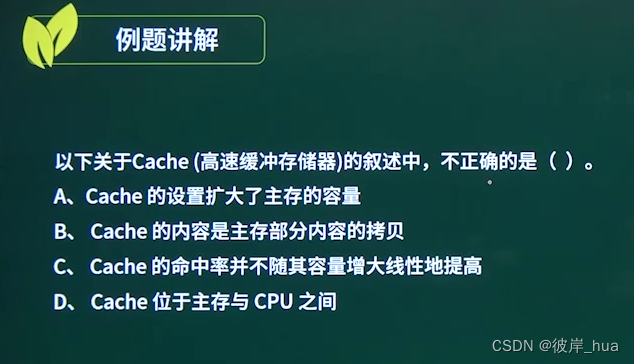

答案:A

解析:Cache的设置不会增大主存的容量,只会增加数据处理速度。

答案:D

解析:硬件

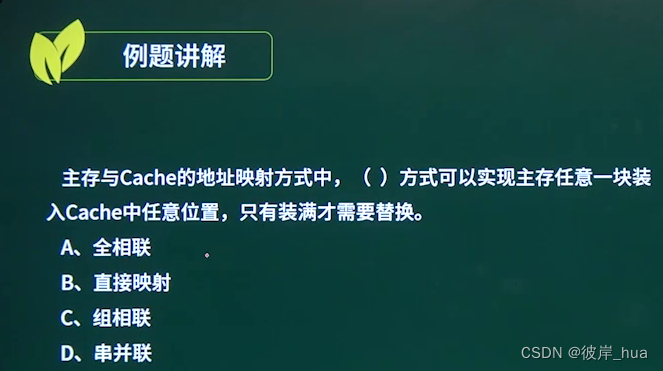

答案:A

解析:全相连的电路简单,冲突率低,所以可以任意存储,冲突率越高,存储的位置越有局限性。

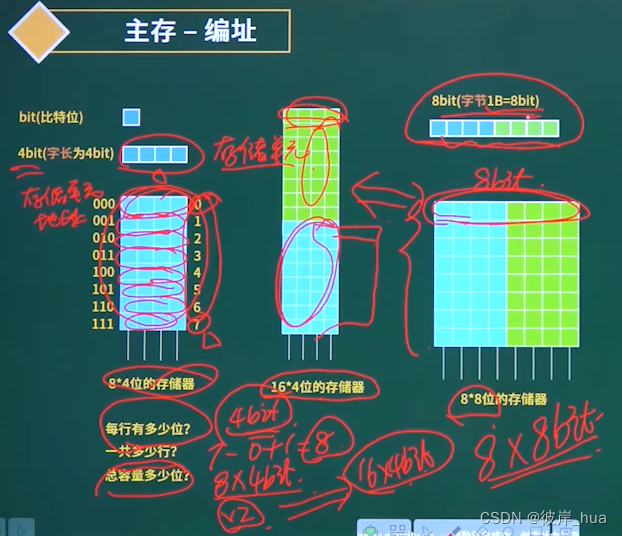

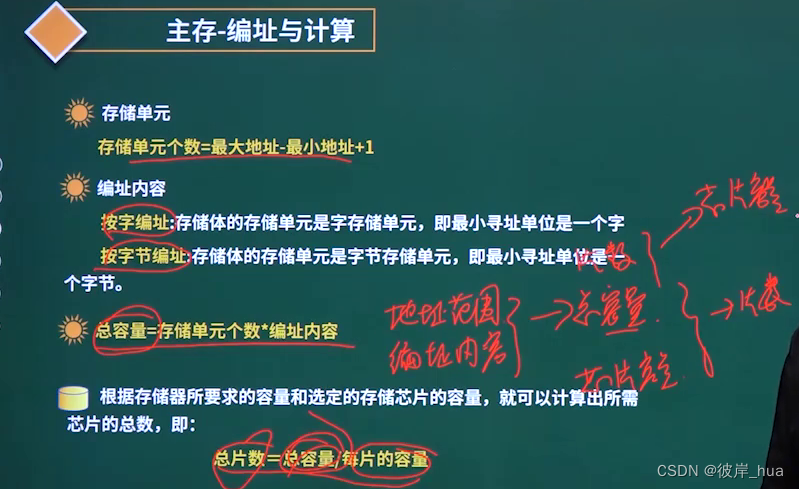

考点三:主存编址计算

简介:

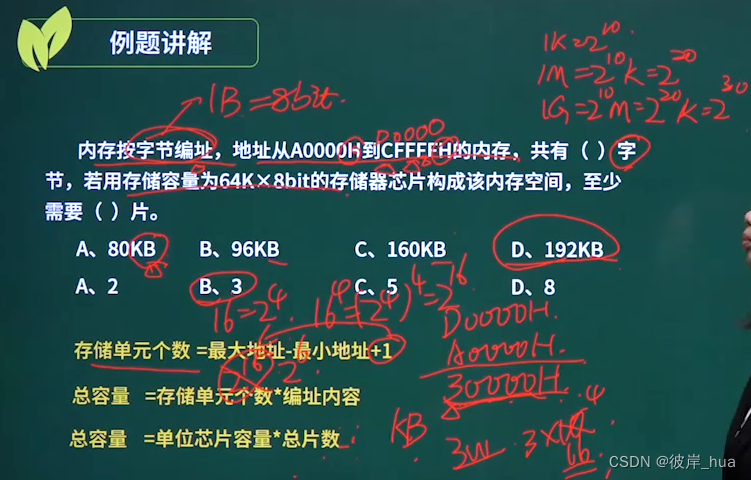

例题:

答案:D、B

解析:按字节编址,为1B=8bit,存储单元格数=最大地址-最小地址+1=CFFFFH-A0000H+1=D0000H-A0000H=30000H=3*16^4。

总容量=3*16^4*8bit=3*2^16*1B

需要将B转为KB,进制转换为1KB=2^10B

等于=(3*2^16*1B)/2^10B=3*2^6=3*64=192KB。

第二空:

总容量=192KB,单位芯片容量为64KB*8bit,192/64=3片。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?