计算机组成原理复习知识点与考点总结(第5章)

-----------------Date by 2022.7.24---------------------

5.1 存储系统的组成

(一) 存储器的分类

1. 按存储器在计算机系统中的作用分类

(1)高速缓冲存储器(Cache)

高速缓冲存储器位于主存与CPU之间,用来存放正在执行的程序段和数据,以便CPU能使用高速地使用它们。

(2)主存储器

主存用来存放计算机运行时存放的程序与数据,CPU可直接随机地进行读/写功能。

(3)辅助存储器

辅助存储器存放在主机的外部,用来存放暂时不参与运行的程序和数据以及一些需要永久性保存的信息。

2.按存取方式分类(考了 论述题)

(1)随机存取存储器(RAM)

CPU可以对存储器中的内容随机地存取,CPU对任何一个存储单元的写入与读出时间是一样的。

(2)只读存取存储器(ROM)

存储器中的内容只能随机读出而不能写入。

(3)顺序存取存储器(SAM)

SAM的内容是按某种顺序存取,存取时间的长短与信息在存储体上的物理位置有关。

(4)直接存取存储器(DAM)

介于RAM与SAM直接。存储器的存取时间也是与信息所在的物理位置有关,但比SAM的存储时间要短。

3.按存储介质分类

(1)磁芯存储器

(2)半导体存储器

(3)磁表面存储器

(4)光存储器

4.按信息的可保存性分类

(1)易失性存储器

断电后存储信息即消失的存储器。如:半导体RAM。

(2)非易失性存储器

断电后存储信息不会消失,仍然保存的存储器。如:半导体ROM、磁芯存储器、磁表面存储器、光存储器。

(二)存储系统层次结构

多级存储系统由n种不同的存储器构成,M1速度最快、容量最小;Mn容量最大、速度最小。

5.2 主存储器的组织

(一)主存储器的基本结构

1. 主存的构成:

主存通常是由存储体、地址译码驱动电路、I/O和读写电路组成。

(1)存储体:

存储体是主存的核心,主要用于存放程序和数据。

(2)地址译码驱动电路:

包括“译码器”和“驱动器”两部分。

“译码器”将地址线传来的地址码转化为对应译码输出线上的有效电平,以表示选中某一存储单元。

“驱动器”提供驱动电流来驱动相应的读写电路,完成对选中存储单元的读写操作。

(3)I/O和读写电路:

包括放大器、写入电路、读写控制电路,用来完成被选中存储单元中各位的读出和写入操作。

(二)主存储器的存储单元

1. 存储单元的含义:

存放存储字或存储字节的主存单元或主存单元。

2. 字节编制计算机的地址安排方案:

(1)大端方案:

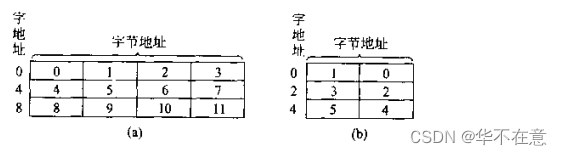

字地址等于最高有效字节地址。字地址为4的倍数。

(2)小端方案

字地址等于最低有效字节地址。字地址为2的倍数。

(a)图为大端方案;(b)图为小端方案。

(三)数据在主存中的存放

1. 数据在主存中的存放方式:

边界对齐方式。

5.3 半导体随机存储器和只读存储器

(一)RAM记忆单元

1. 记忆单元的含义:

把存放一个二进制位的物理器件成为记忆单元。

2. RAM分类:

(1)SRAM(静态RAM)

(2)DRAM(动态RAM)

3. 记忆单元电路分类:

(1)6管SARM记忆单元电路

集成度低,多用于高速缓冲存储器。(这里的集成度是指:单块芯片所容纳的元件数目,数目越多、集成度越高;数目越少、集成度越低)

(2)4管DRAM记忆单元电路

集成度高,多用于大容量主存系统。

(3)单管DRAM记忆单元电路

集成度更高,功耗更小。

(二)动态RAM的刷新

1. DRAM刷新的原因:(考了 简答题)

给栅极电容补充电荷

2. 刷新间隔:

2ms

3. 刷新方式:(考了 简答题)

(1)集中刷新方式:

在允许的最大刷新间隔内,按照存储芯片容量的大小集中安排若干个刷新周期,刷新时停止读写。(因为集中刷新阶段停止读写,所以这段时间称为“死区”。存储容量越大、死区越大。)

(2)分散刷新方式:

把刷新操作分散到每个存取周期内进行,此时系统的存取周期被分为两部分,前一部分时间进行读写操作或保持、后一部分时间进行刷新操作。

(3)异步刷新方式:

异步刷新方式是前两种的结合。充分利用了最大刷新间隔时间,将刷新操作平均分配到整个最大的刷新间隔时间中。

(三)RAM芯片分析

1. RAM芯片:

RAM芯片与外部连接是通过地址线、数据线和控制线。

(1)地址线:

单向输入

(2)数据线:

双向输入:

(3)控制线:

①控制读写线

②片选线

2. 存储器的规格:

存储器或存储芯片的规格为:M*N

M表示存储单元;N表示每个单元位数。

如:容量为1024 * 4时,地址线有:10根(2的10次方等于1024),数据线有:4根。

容量为64K*1时,地址线有:16根(2的16次方等于64K),数据线有:1根。

(四)半导体只读存储器

1.ROM的类型

(1)掩膜式ROM(MROM)

(2)一次可编程ROM(PROM)

(3)可擦除可编程ROM(EPROM)

(4)闪存存储器

5.4主存储器的连接与控制

(一)主存容量的扩展

1.芯片数个数的确定:

总片数 = (总容量)/(容量)

如:存储容量为 8K*8,若选用1K*4的存储芯片,则:

(8K*8)/(1K*4) =16片

2.芯片连接的方式:

(1)位扩展:

是指只在位方向扩展,将个存储芯片的地址线、片选线、读写线相应地并联起来,将数据线单独列出。

(2)字扩展:

是指只在字方向扩展,将个存储芯片的地址线、数据线、读写线相应地并联起来,用片选线来区分各个芯片。

(3)位和字同时扩展:

在位数和字数上同时扩展

5.7 高速缓冲存储器

(一) 高速缓冲工作原理

1.程序的局部性原理

(1)时间局部性

如果一个存储单元被访问,那么这个存储单元很快被再次访问,因为程序存在着循环。

(2)空间局部性

如果一个存储单元被访问,那么该单元相邻的单元也很快被访问,因为程序大部分指令是顺序存储、顺序执行的。

7516

7516

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?