采用CSMC0.18um工艺。VCC=5V,VIN=VIP=2.5V。

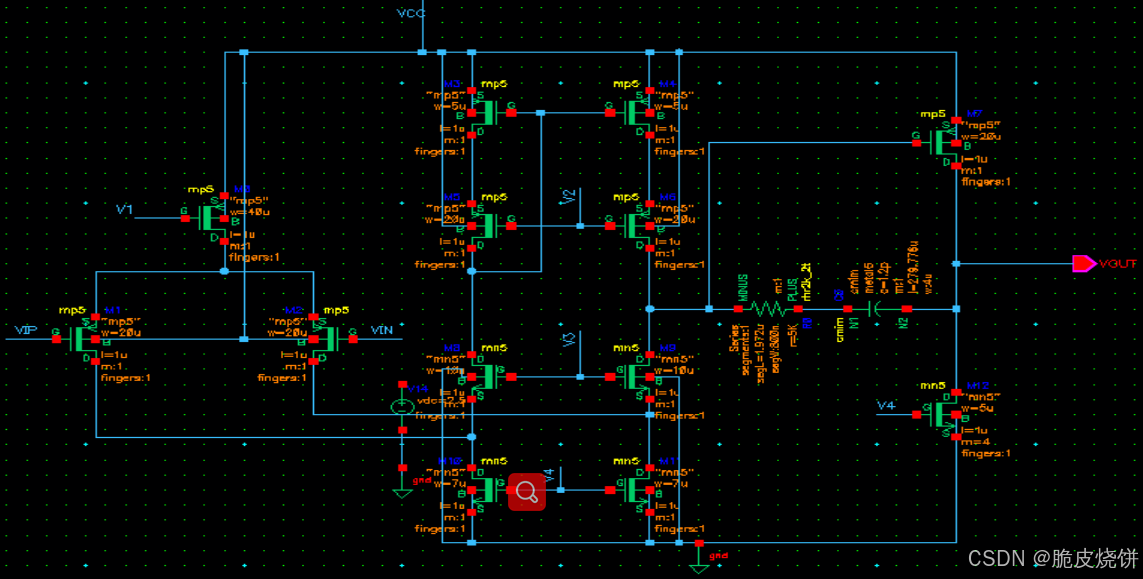

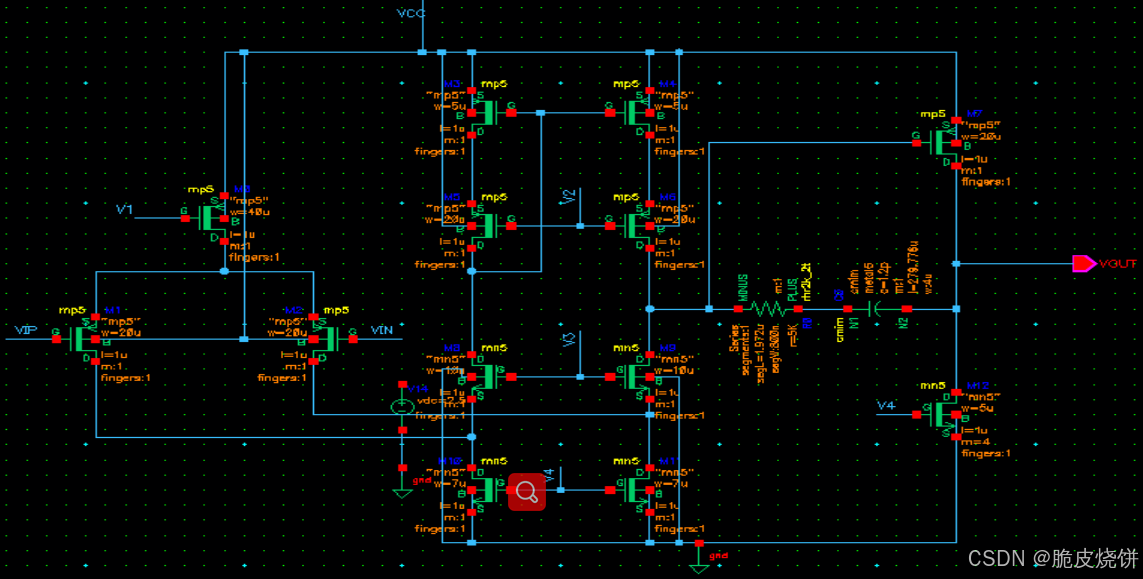

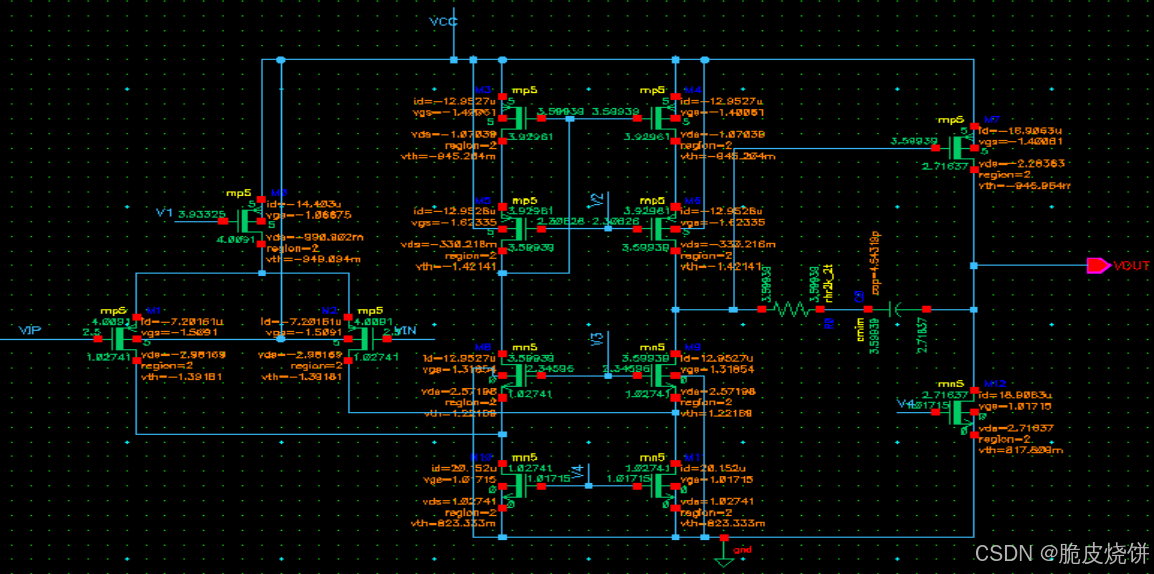

电路图为:

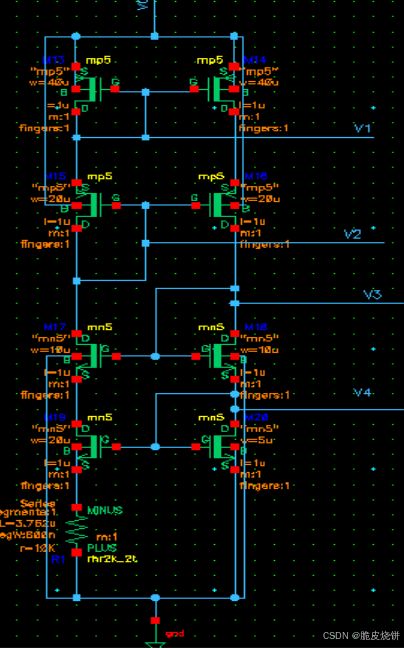

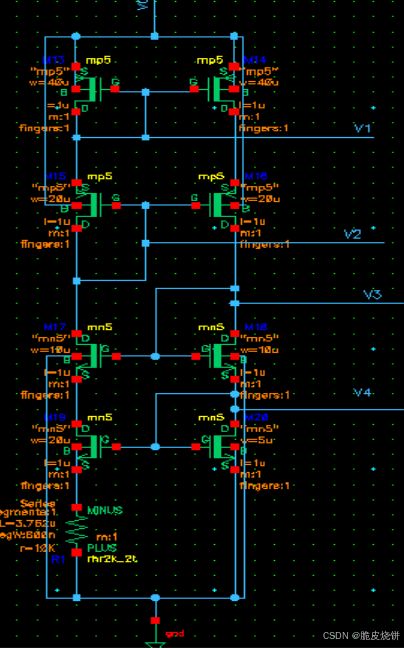

偏置电路参考复旦两级运放设计,但这种结构在流片后可能不能达到最完美的结果。R=10K。

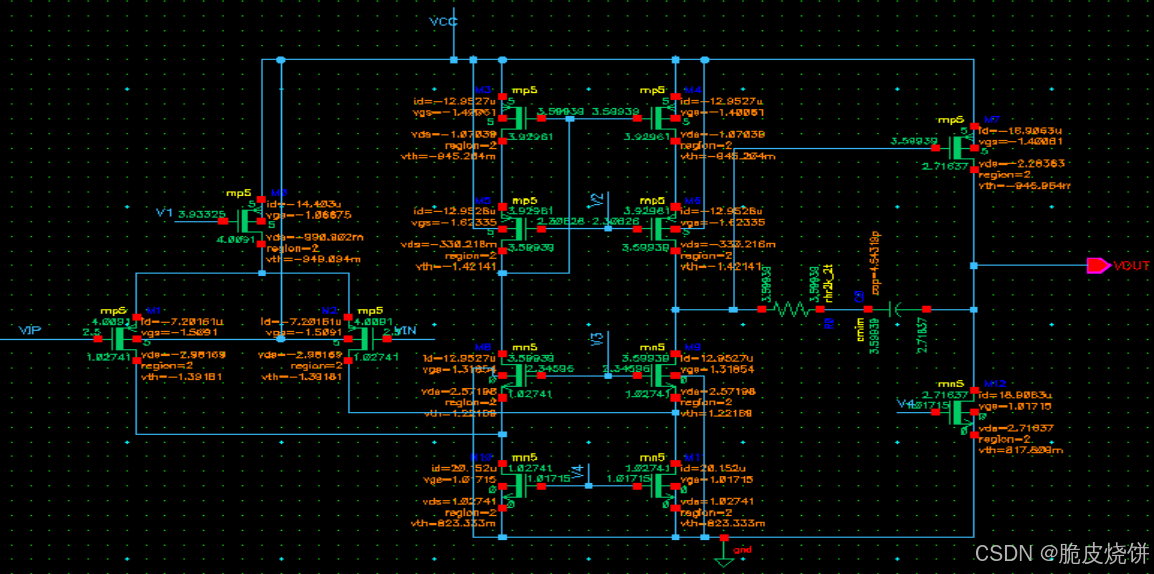

DC仿真各个管子都在饱和区。

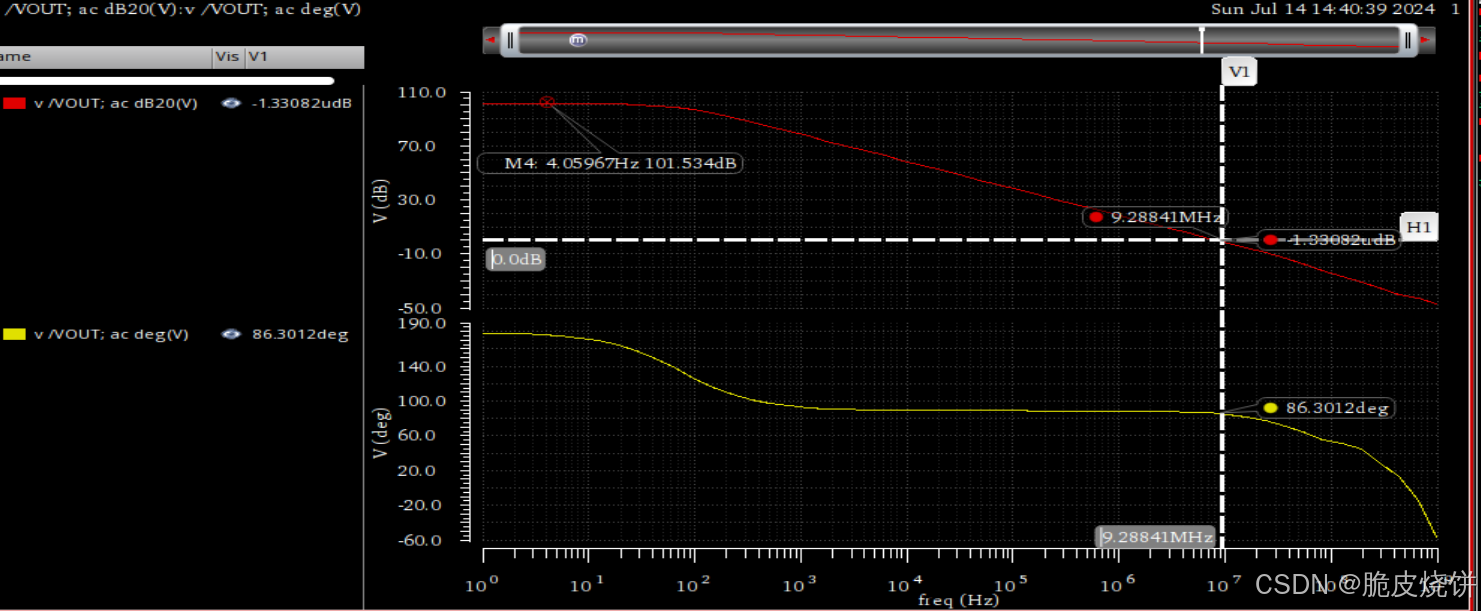

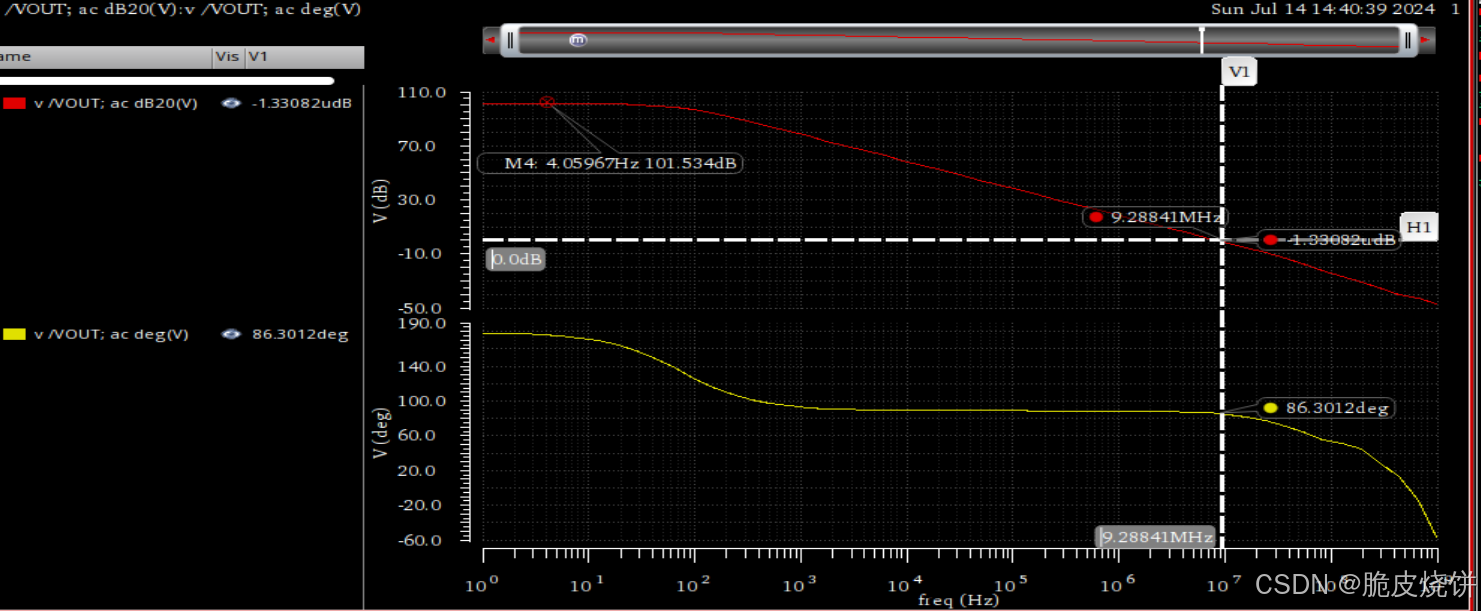

接下来进行AC仿真查看增益、带宽和相位裕度。增益是101dB 带宽是9M 相位裕度94°。

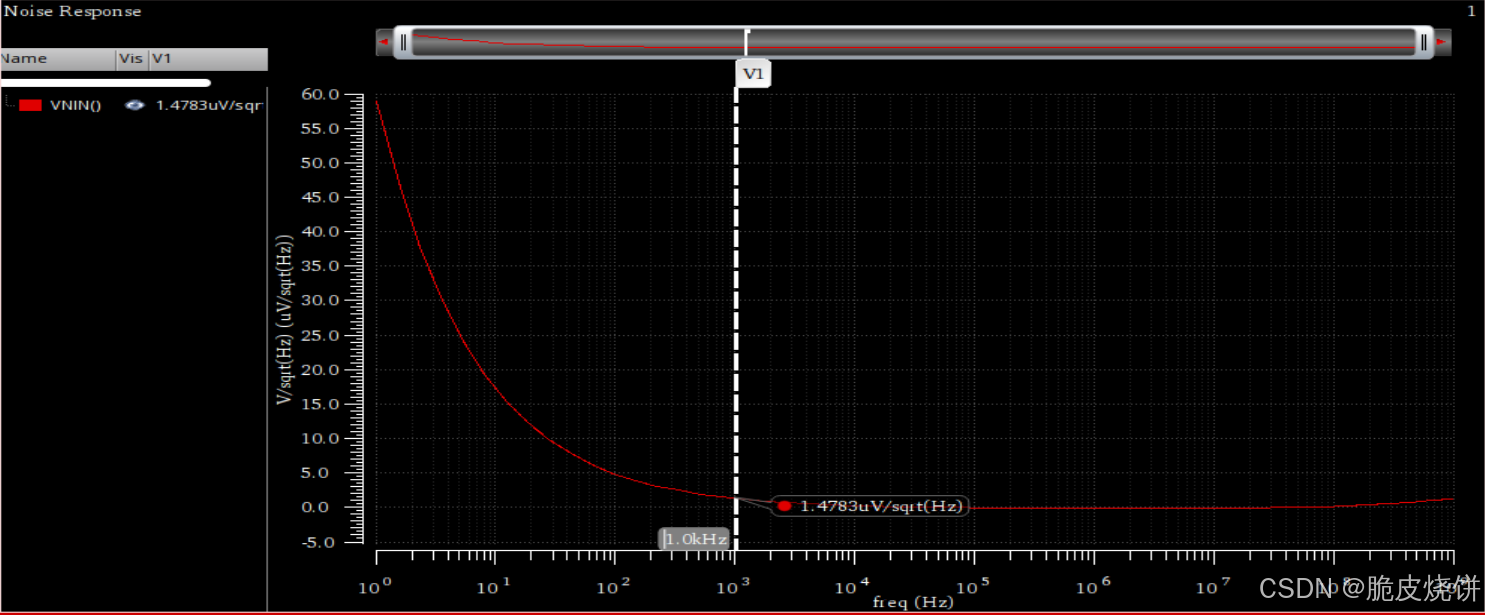

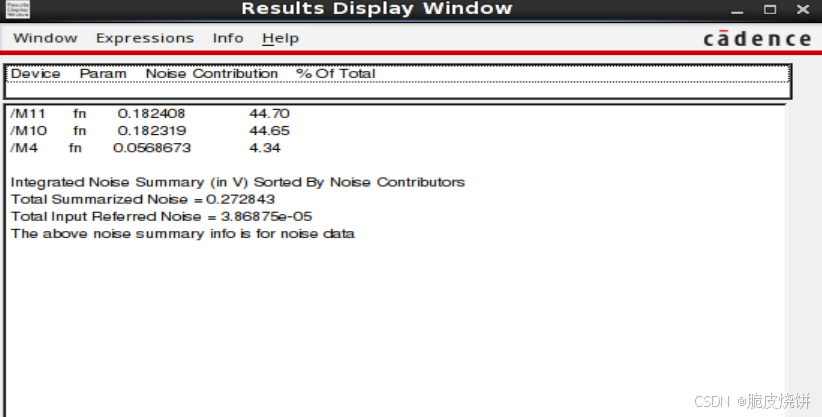

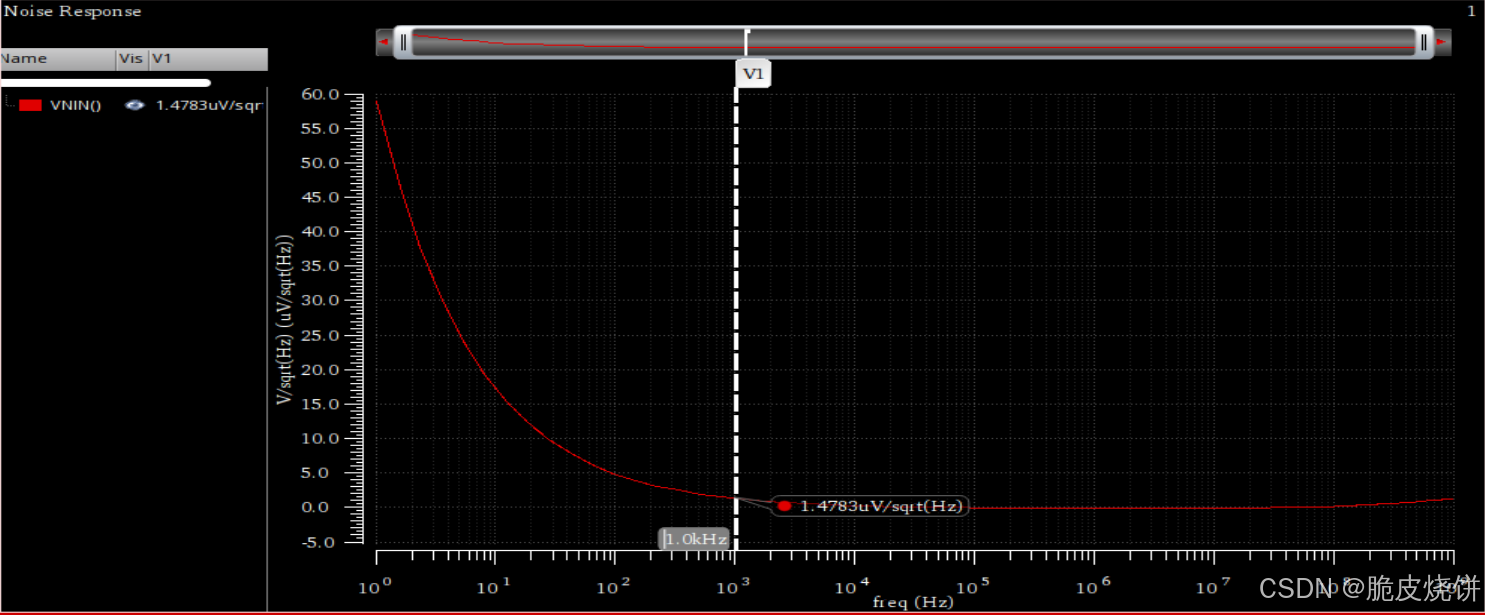

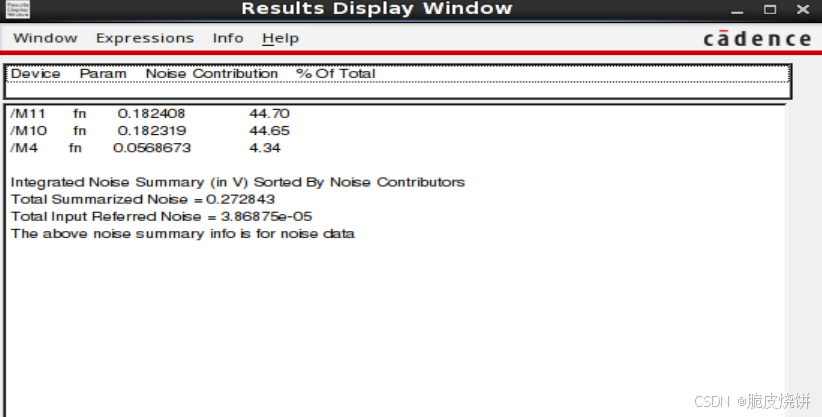

接下来进行噪声仿真。在1KHz时,噪声为1.48uV/sqrt(Hz)。对1K-2K区间做积分,等效输入噪声为38uVrms。

在相位裕度和噪声方面还要继续改进。

采用CSMC0.18um工艺。VCC=5V,VIN=VIP=2.5V。

电路图为:

偏置电路参考复旦两级运放设计,但这种结构在流片后可能不能达到最完美的结果。R=10K。

DC仿真各个管子都在饱和区。

接下来进行AC仿真查看增益、带宽和相位裕度。增益是101dB 带宽是9M 相位裕度94°。

接下来进行噪声仿真。在1KHz时,噪声为1.48uV/sqrt(Hz)。对1K-2K区间做积分,等效输入噪声为38uVrms。

在相位裕度和噪声方面还要继续改进。

1万+

1万+

915

915

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?