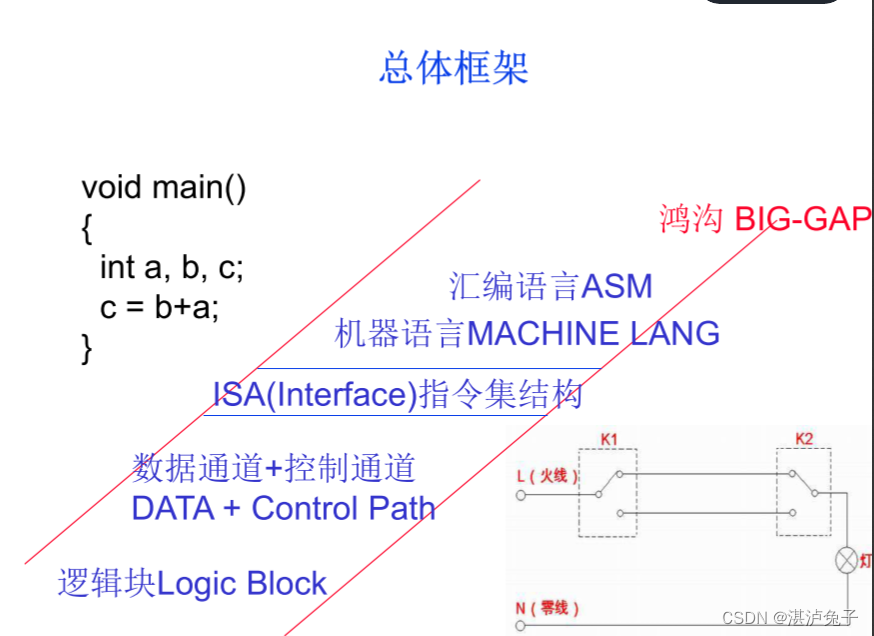

整个学习的结构

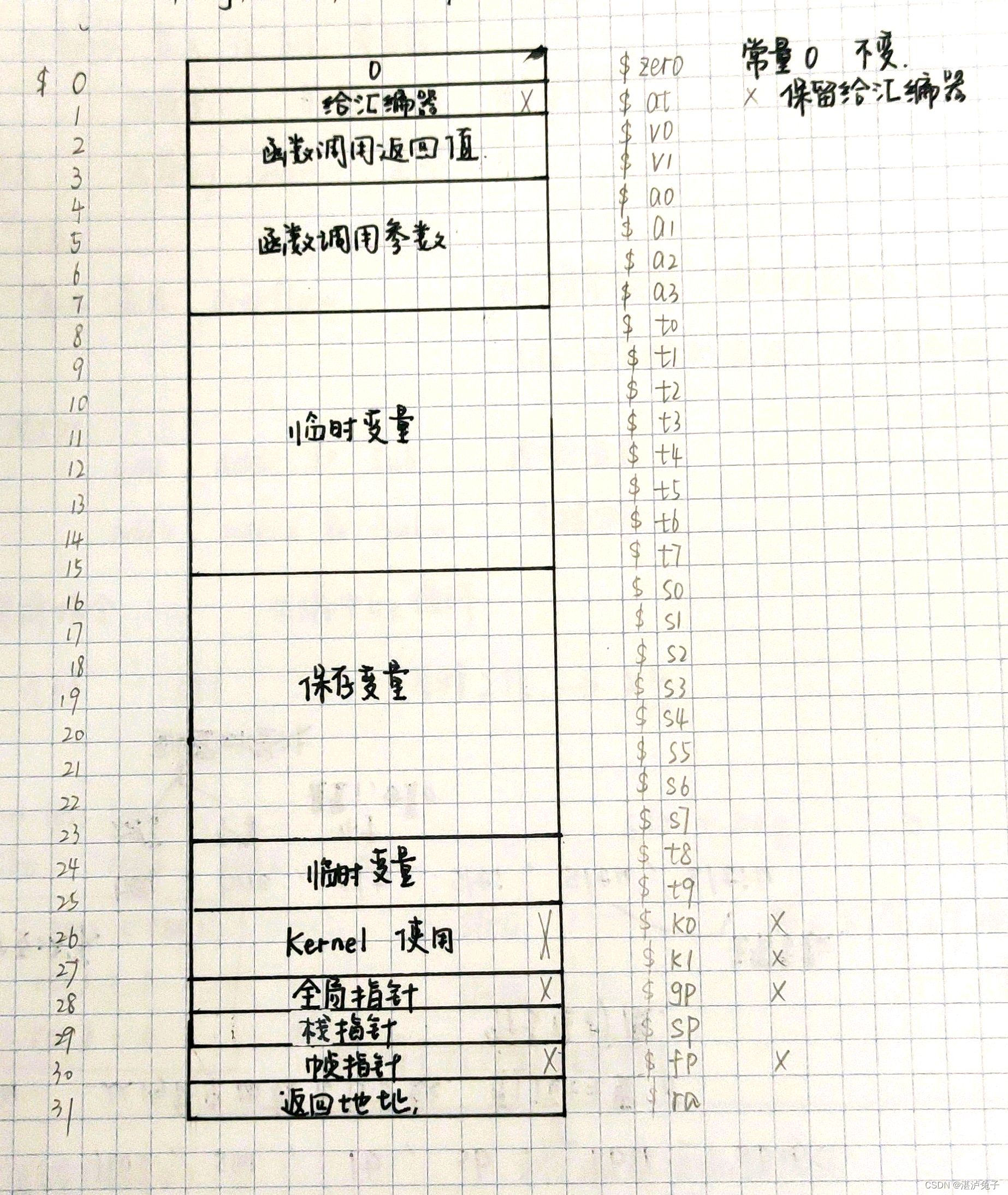

寄存器

MIPS所采用的寄存器如上图所示,下面列出几个常用的寄存器

$zero存储唯一值——0$a0-\$a3这三个寄存器存储函数参数$t0-\$t7、$t8-\$t9存储临时变量;注意这两组寄存器并不相连$s0-\$s7用于保存变量的值$sp保存栈指针;指向栈顶位置$ra存储下一条需要执行指令的地址

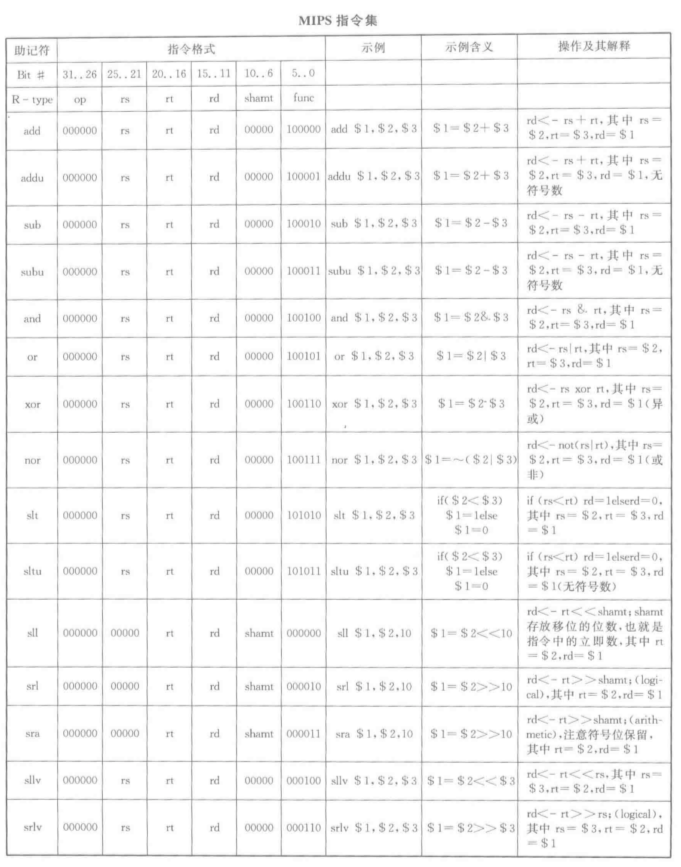

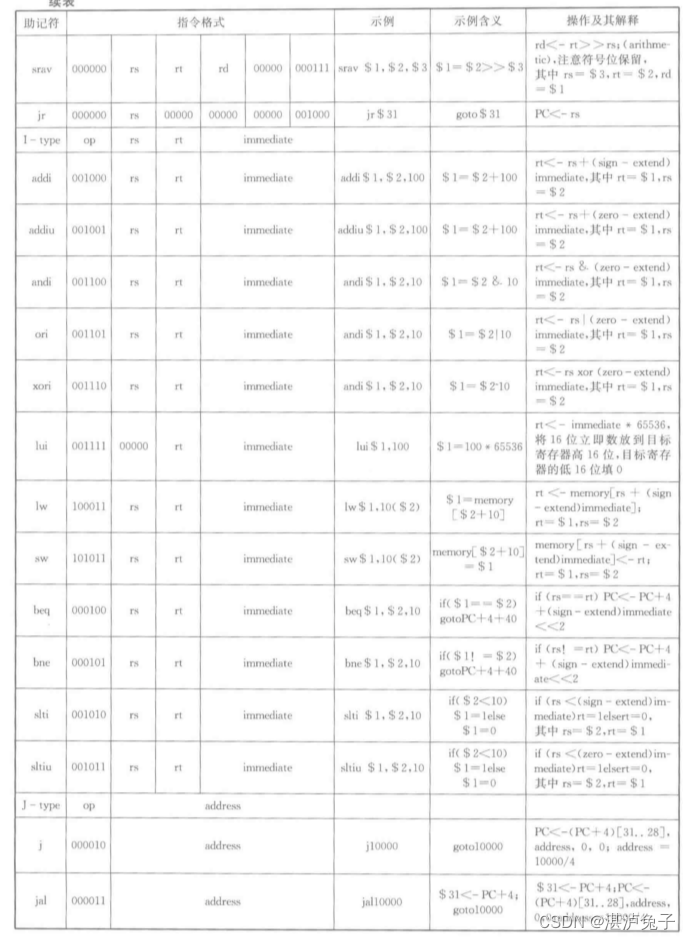

指令自查表

汇编语言与汇编指令

常用的MIPS指令

算术运算

add

加法

add $Destination,$num1,$num2

上述等价于—> Destination = num1 +num2

sub

减法

sub $Destination,$num1,$num2

上述等价于—> Destination = num1 - num2

addi

加立即数immediate

addi $Destination,$num1,num2

num2是一个数字而非寄存器

📌注意!没有subi;subi可以用addi加负数代替

addu&subu

不检测溢出的加减法

addu $Destination,$num1,$num2

subu $Destination,$num1,$num2

Ada检测溢出、C不检测溢出

因此,编译器对于溢出的会按照语言的不同来转换不同的机器指令

addu和subu就是不检测溢出的指令

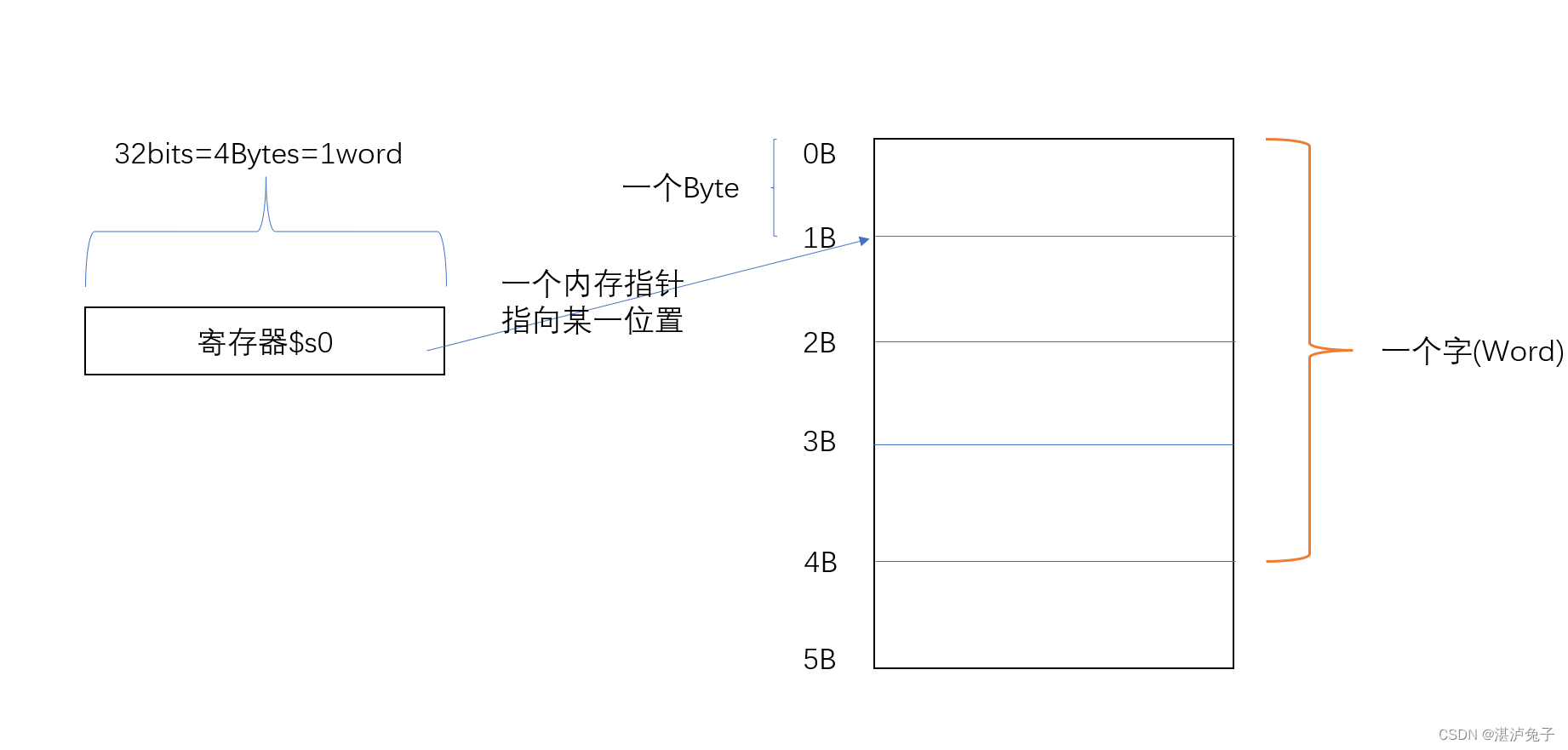

内存相关数据传送

lw

LoadWord 从内存中加载一个字(通常是32位)

lw $t0,offset($s0)

表示从$s0指向的内存地址加offset偏移量后取得32位数据存入寄存器t0

此处的$s0实际上存储的是一个指针

上图中内存指针指向1B;在1B的基础上+offset,以此为起始位置,取一个字放入$t0

sw

StoreWord 向内存中存储一个字(通常是32位)

sw $t0,offset($s0)

和上图原理一致,只是方向相反,取$t0的值,在$0指向的内存地址上+offset作为起始地址存储一个Word

字对齐:相邻字之间的地址相差四个字节而不是一个字节

lb&sb

LoadByte

lb $s0,3($s1)

从$s1+3的地址开始取一个Byte的数据存入$s0

🤦♂️这里出现问题了,寄存器有4Byte,要存入1Byte怎么存放呢?

答案是将这8bits存到寄存器的低8位,高24位 符号位扩展

- 对于有符号数

- 符号位扩展:高24位与符号位相同(lb默认操作)

- 对于无符号数

- 零扩展:高24位均取0

- 有一条特殊指令

lbuLoadByteUnsighed;该指令会对高位进行零扩展

StoreByte

sb $s0,3($s1)

从$s0中取一个Byte存入内存中$s1+3的位置

😶32位寄存器中取8位存入,那剩下的24位怎么办?

比较指令

beq

相等

$beq $reg1,$reg2,Label

当 reg1==reg2 时跳转到 Label 处

bne

不相等

$bne $reg1,$reg2,Label

当 reg1 != reg2 时跳转到 Label 处

j

无条件跳转

j Label

跳转到 label处

slt

Set on less than;

slt reg1,reg2,reg3

- reg2<reg3 reg1=1

- 否则 reg1=0

使用这一条指令,可以实现

<、>、≤、≥的判断

小于

if (g<h) goto Less; #变量映射是 g:$s0,h:$s1

------------>

slt $t0,$s0,$s1

bne $t0,$0,Less

大于等于

if (g≥h) goto GTE; #变量映射是 g:$s0,h:$s1

------------>

slt $t0,$s0,$s1

beq $t0,$0,GTE

小于等于

if (g≤h) goto LTE; #变量映射是 g:$s0,h:$s1

------------>

slt $t0,$s1,$s0

beq $t0,$0,LTE

大于

if (g>h) goto LTE; #变量映射是 g:$s0,h:$s1

------------>

slt $t0,$s1,$s0

bne $t0,$0,LTE

👉还有立即数比较的

slti无符号比较的

sltu

跳转指令

jr

Jump Regster 直接跳转寄存器

jr $reg

最常用的就是直接跳转到 $ra 即下一行要执行指令的位置

jal

Jump and Link 跳转并保存

jal Label

- Link 保存下一条指令的地址到$ra

- Jump 跳转到给定标记处

逻辑运算

and

按位与运算

and $reg1,$reg2,$reg3

reg1=reg2®3

andi

与立即数进行与运算

and $reg1,$reg2,immediate

reg1=reg2&immediate

⭐使用掩码做与运算将位串的特定部分分离出来

1110&0011 = 0010 即分离出了后两位

or

按位与运算

or $reg1,$reg2,$reg3

reg1=reg2®3

ori

与立即数进行与运算

ori $reg1,$reg2,immediate

reg1=reg2|immediate

⭐任何数与1做或为1,与0做或为原数—>强制某些位为1

sll

Shift Left Logical 逻辑左移

sll $reg1,$reg2,num

将reg2里的值左移num位放入reg1中

空出来的位填0

srl

和sll类似,不过右移num位

空出来的位填0

sra

Shift Right Arithmetic 算术右移

左移num位就是$ ×2^{num}$

右移$ ×2^{-num} , 或 者 说 ,或者说 ,或者说 ÷2^{num}$

📌要做计算的时候记得用sra

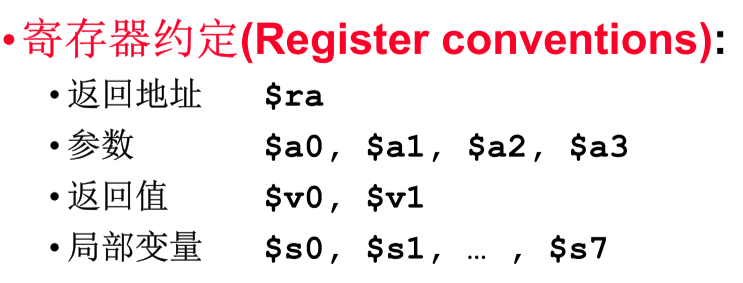

函数调用

简单的嵌套调用可以使用寄存器约定;但是复杂的多层嵌套调用就必须使用栈了!

寄存器约定保存信息

使用栈保存信息

- 手工编译

Caller&Callee

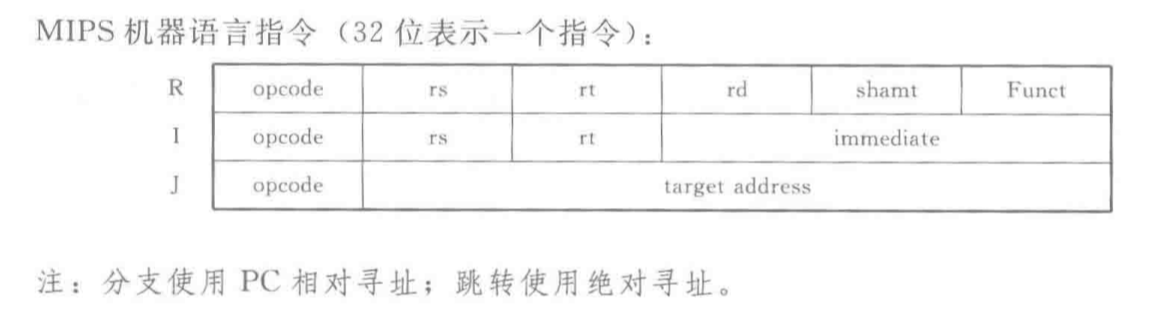

机器语言

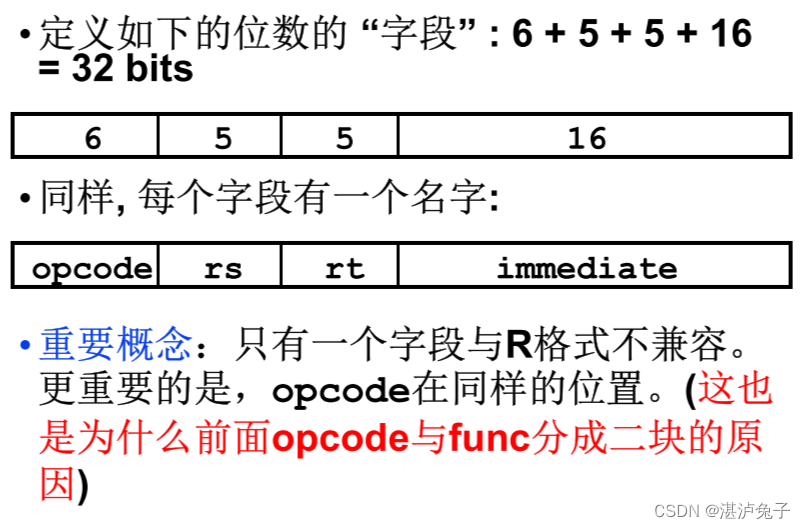

- I-格式

- 带立即数

- lw&sw

- 分支语句

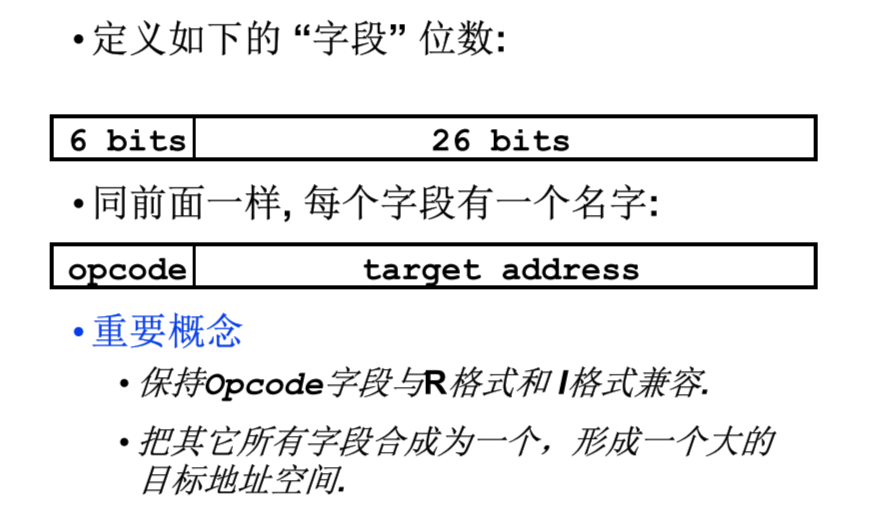

- J-格式

- j&jal

- R-格式

- 其他所有指令

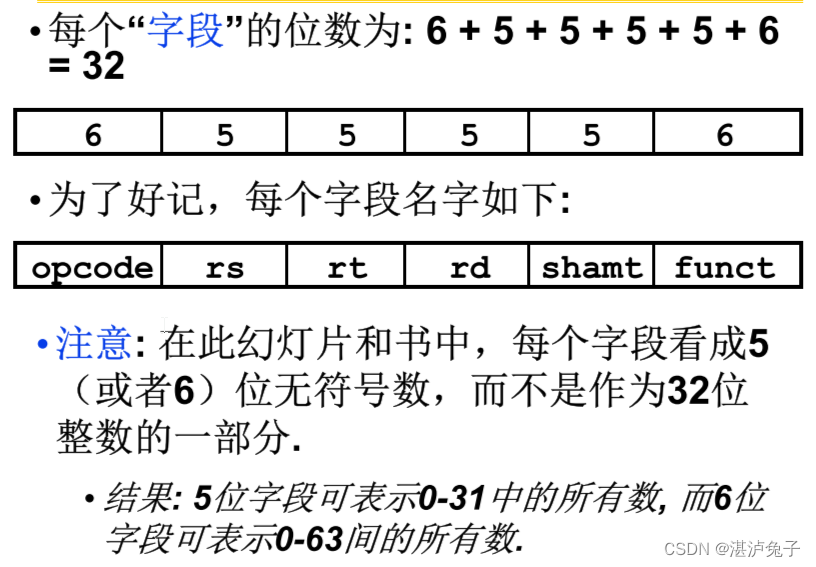

指令格式

R格式

- opcode: 所有R格式指令,此字段为0;和funct字段一起,共同确定具体的指令

- rs

Source Register确定首操作数的寄存器 - rt

Target Register确定次操作数的寄存器 - rd

Destination Register指定存放计算结果的寄存器 - shamt 包含移位指令需要移的位数;除了移位指令外,此位设为0

- add $reg1(rd),$reg2(rs),$reg3(rt)

I格式

- opcode 独立指定指令

- rs 指定寄存器操作数(如果有)

- rt 指定保存计算结果的寄存器

- addi $reg1(rt) $reg2(rs) imme

addi,slti 立即数符号扩展为32位

❓这里无符号数也进行符号位扩展,为了硬件的简单牺牲一定的数据,仅对$2^{15}\le n n n\lt 2^{16}$有问题,只能由汇编器想办法解决了

I格式问题

如何解决I格式问题?软件中处理+新指令

lui

新指令lui register,immediate

Load Upper Immediate 装入立即数高位

取立即数并将立即数放到寄存器高位部分,剩下部分填充0

PC-相对寻址

我们只有16位立即数,怎么解决32位分支指令?

PC-相对寻址作为32位分支指令解决方案

以PC为基点,分支$\pm 2^{15} $字节,保证大多数循环的寻址要求

指令是字,满足字对齐,后两位总是00

- 指定立即数immmediate以字作为单位

这样以PC为基点,可以分支$\pm 2^{15} 个 字 ( 或 个字 (或 个字(或\pm 2^{17} $个字节),因此,可以处理的循环范围为原来的4倍

J格式

现在可以表示26位的地址

- 由于字对齐,默认最后两位为00 +2

- 由于PC相对寻址,从PC处取最高4位 +4

- 这样26+2+4=32;我们成功表达了32位的地址

反汇编

对于32位机器指令的解码遵循下面步骤

- 把16进制转为2进制表示

- 确定opcode和指令格式

- opcode R:0 J:2/3 I:其他

- 基于格式分割字段

- R:6 5 5 5 5 6

- I:6 5 5 16

- J:6 26

- 反汇编为MIPS汇编指令

伪指令

不能直接转成MIPS语言,先要转成几条MIPS指令的组合

MAL(MIPS Assembly Language) 包含伪指令

TAL(True Assembly Language) 不包含伪指令

C--->MAL--->TAL翻译顺序

一些常见的伪指令

move

寄存器赋值

move $reg2,$reg1

将reg1的值赋给reg2

li

装入立即数(Load Immediate)

li $reg,immediate

la

装入地址(Load Address)

la $reg,label

把label对应的地址装入reg

ror

循环右移(Rotate Right Instruction)

ror $reg,value

把寄存器中的值循环右移value位

错误操作的操作数

比如addu指令写成了addu $reg1,$reg2,immediate

会自动改写为addiu $reg1,$reg2,immediate

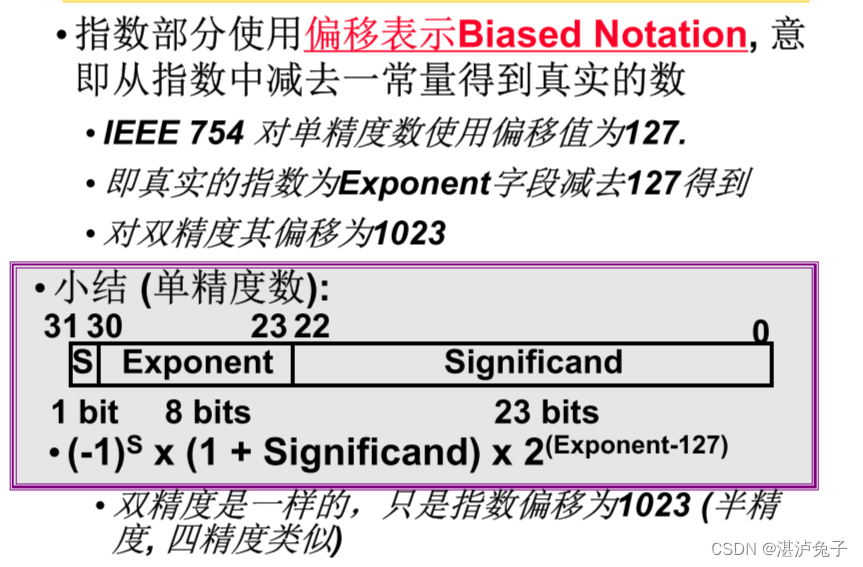

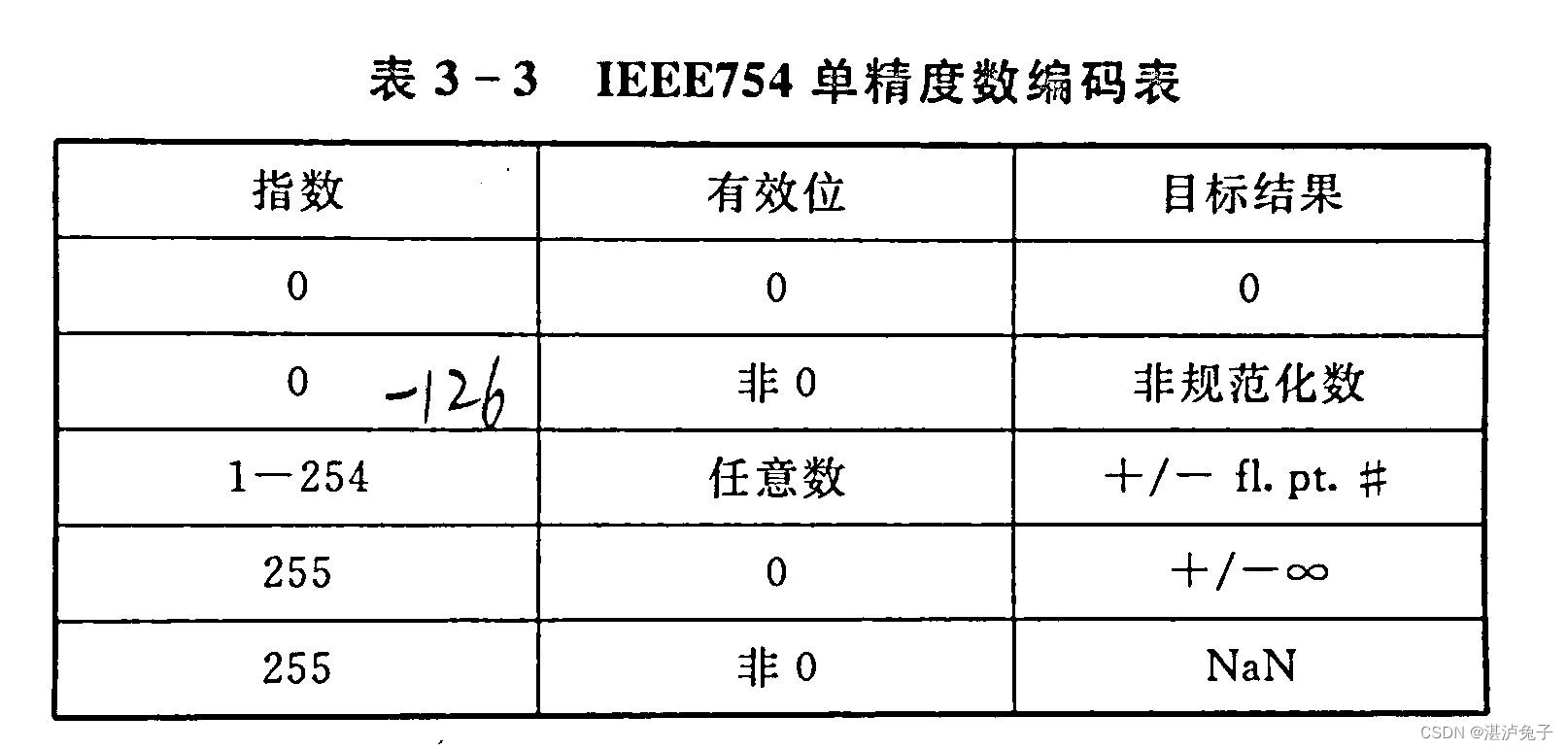

浮点数

IEEE754标准

标准形式

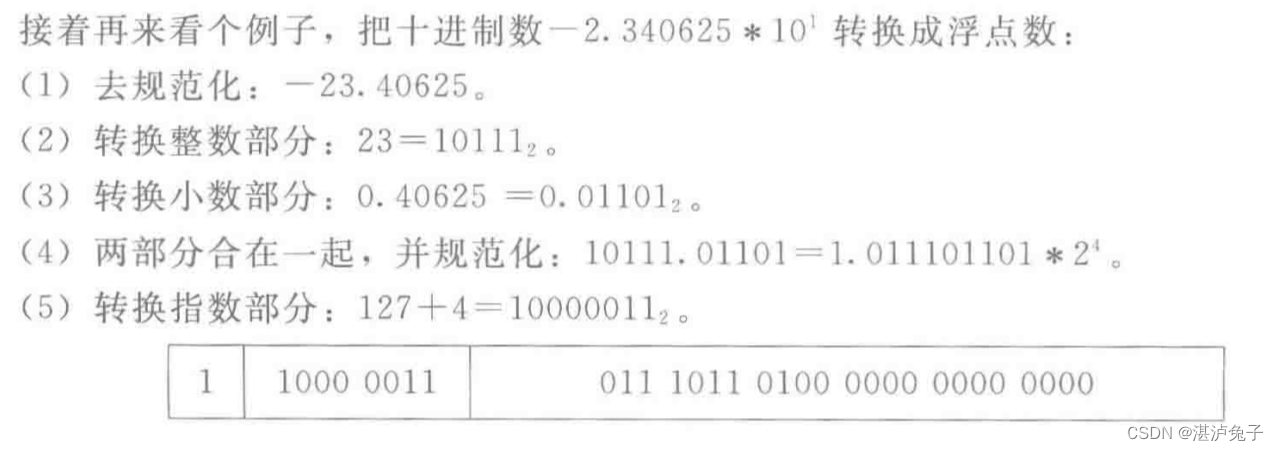

通过一个例子感受如何在二进制位串和十进制数字间进行转换

0 |0110 1000|101 0101 0100 0011 0100 0010

将上面的位串转换为十进制

- s=0 正数

- expont = 104 偏移调整104-127=-23

- significand = 1+1* 2 − 1 2^{-1} 2−1+0* 2 − 2 2^{-2} 2−2+1* 2 − 3 2^{-3} 2−3+…+0* 2 − 23 2^{-23} 2−23 = 1+0.666115

- 1.666115* 2 − 23 2^{-23} 2−23 = 1.9860* 1 0 − 7 10^{-7} 10−7

十进制转二进制

特殊数的表示

精度

- Precision 计算机一个字用于表示数的位数

精确性

- Accuracy 用于衡量精确值与计算机表示之间的差异

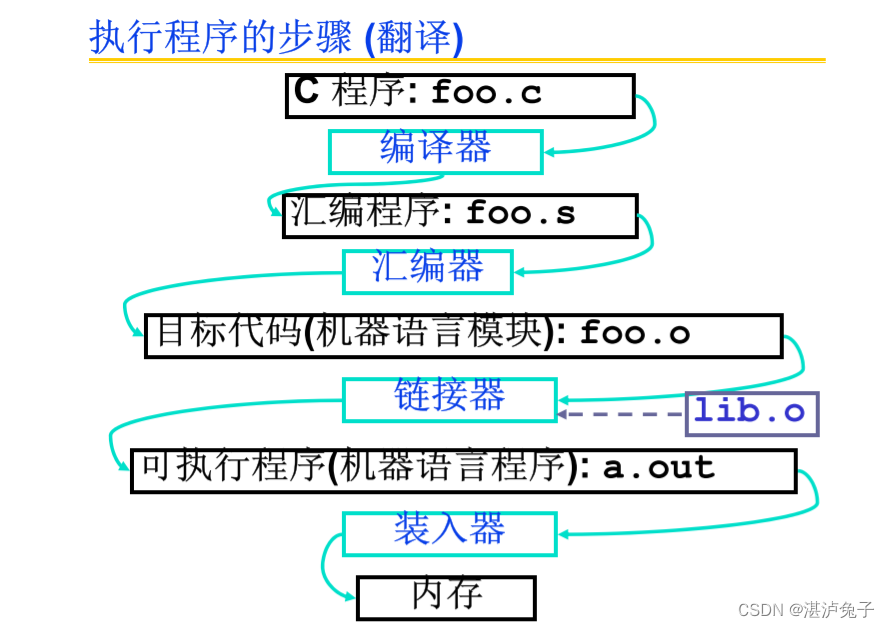

程序的运行

编译和翻译

高级语言的执行有两种方式

- 解释Interpreter

- 例如Python、Java;解释器读入语言并执行

- 翻译Translator

- 将程序翻译成机器语言再执行;执行效率高、隐藏源码

汇编器

1.读入并使用指示器Directive

指示器产生一系列的提示信息,不产生机器指令

2.替代伪指令

将伪指令替换为一组汇编指令

3.生成机器语言

分支怎么办?PC相对寻址

前向引用问题?分支指令引用还未遇到的标记

使用两次扫描的方式解决问题,一次扫描记住标记位置,第二次扫描使用标记位置产生代码。

跳转指令的问题?需要绝对地址

产生两张表

- 符号表

- 我有什么

- 重定位表

- 我要什么

4.生成目标文件

连接器

输入代码和信息表;输出可执行程序

使得多个文件的分离编译称为可能

- 从每个.o文件取代码段放一起

- 从每个.o文件取数据段放一起,然后整体连到代码段尾部

- 检查重定向表填充绝对地址

- PC相对寻址 不重定位

- 绝对地址、外部引用、数据引用 重定位

动态链接库DLL

便于及时更新,且体积小

静态链接库lib

装入器

操作系统的一部分,输入执行代码(.out).exe,输出正在运行的程序

电路基础和基本计算模块

同步数字系统

ISA(Instruction Structure Architecture,指令集结构)是软件与硬件之间的协议

- 同步

- 所有的操作都由一个中央时钟同步

- 数字

- 所有的值都用离散值来表示

晶体管的两种类型

- n-type

- 有电通,无电不通

- p-type

- 有电不通,无电通

信号与波形

同步数字系统由两种基本电路构成

信号正边沿触发!

- 组合逻辑电路

- 输出是输入经过一定规则后的运算结果

- 状态电路

- 存储信息

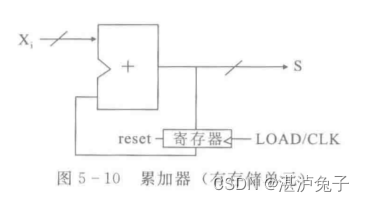

状态单元

状态单元用来储存数值,控制组合逻辑块间的信息流动;如寄存器

寄存器由多个翻转器(在0,1之间变换)组成,正边沿触发;reset是强制清零的信号

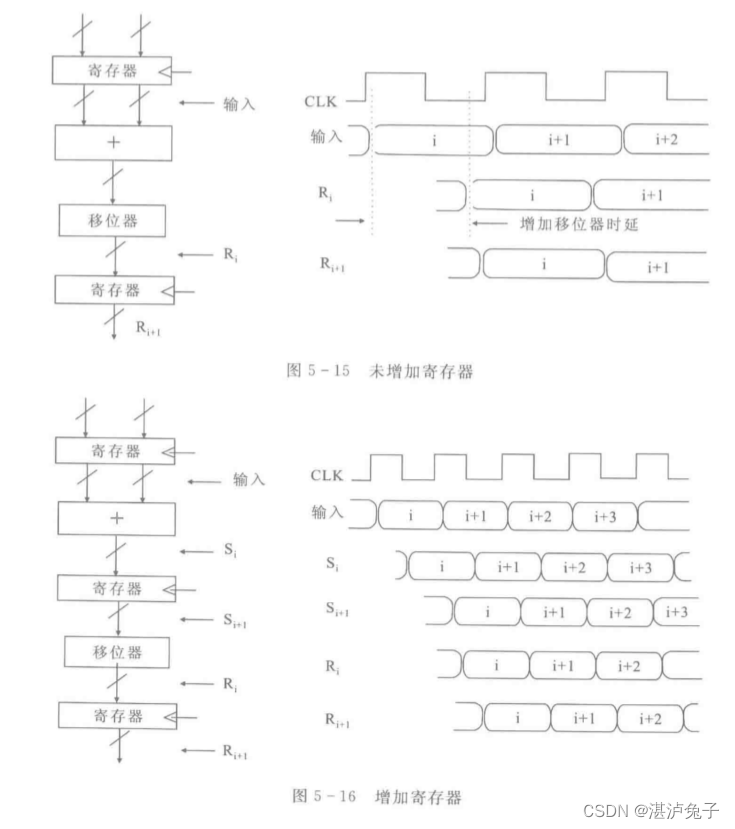

可以通过增加寄存器加快时钟频率

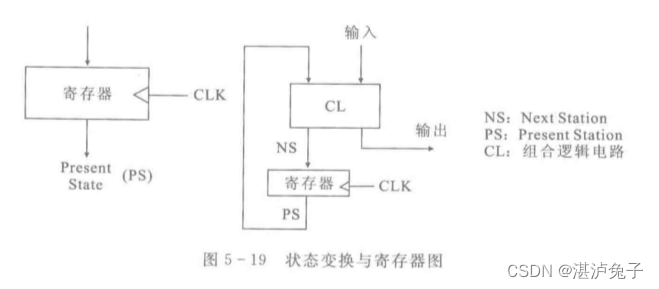

状态变换FSM图也可以借助寄存器来实现

电路组合

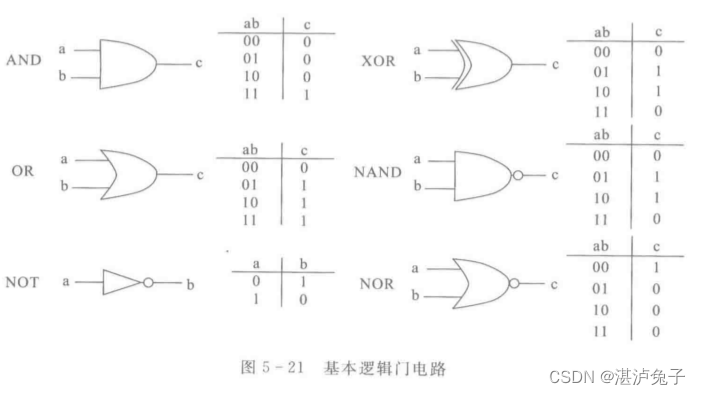

常见逻辑门的表示与真值表

异或XOR:当有奇数个1时输出1

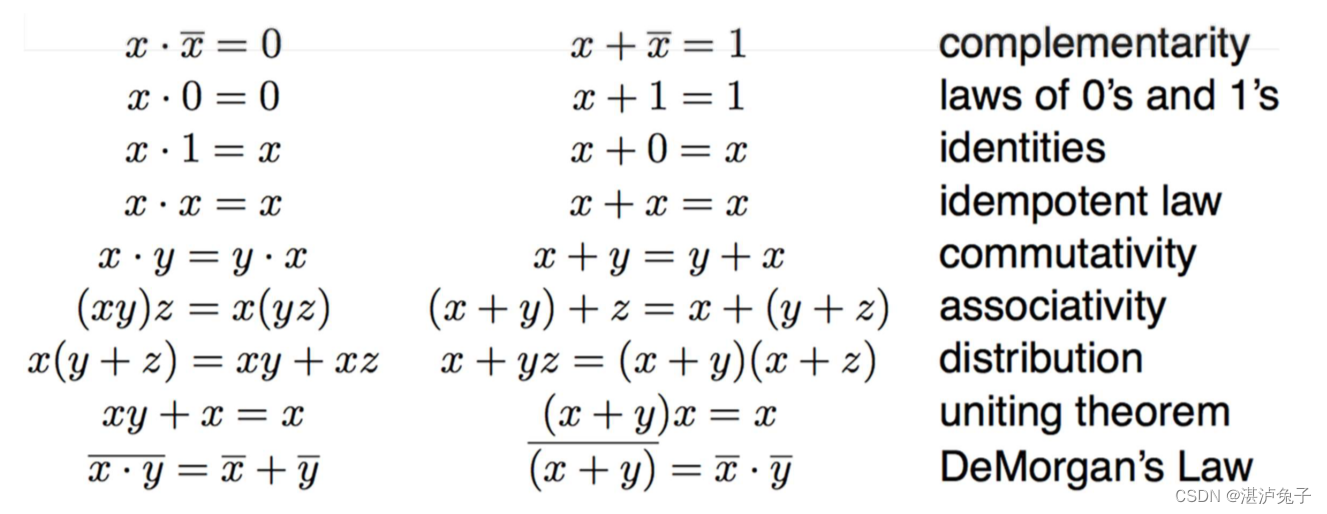

布尔代数

运用布尔代数可以化简电路

结合真值表可以设计电路

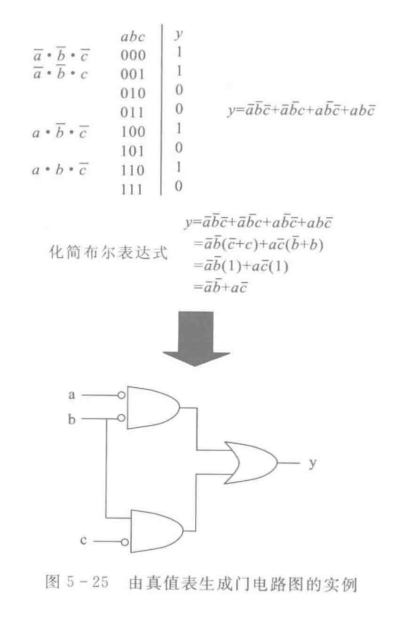

如何从真值表生成门电路呢?看下图

·是And

+是Or

图5-25中显示的是二选一MUX;利用层次结构可用二选一的MUX组合成四选一的MUX

设计ALU

32位加法器

首先画出真值表,发现有 2 64 2^{64} 264个表项;太多了,我们得换个思路---->分解!

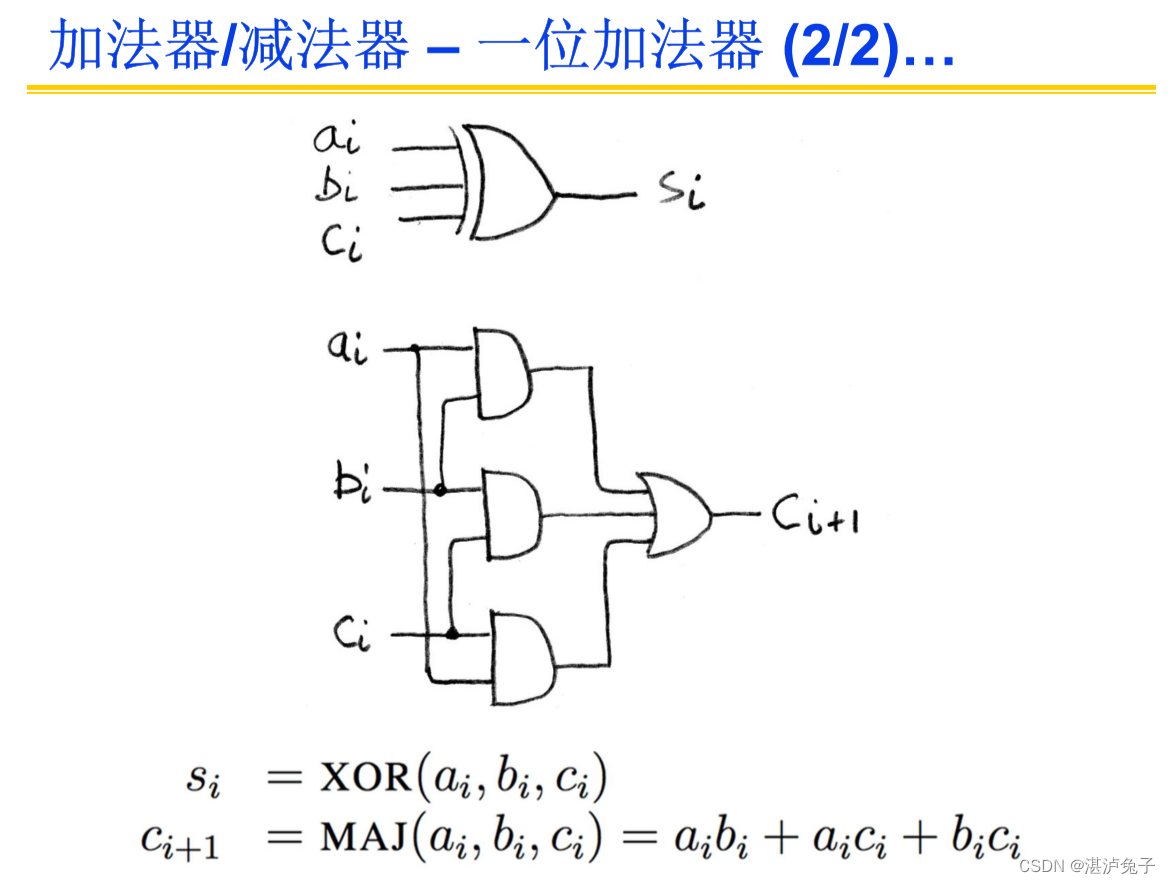

设计一位加法器

画出真值表—>写出布尔表达式并化简—>设计电路

把许多一位加法器连起来就可以构成多位加法器

溢出?不懂

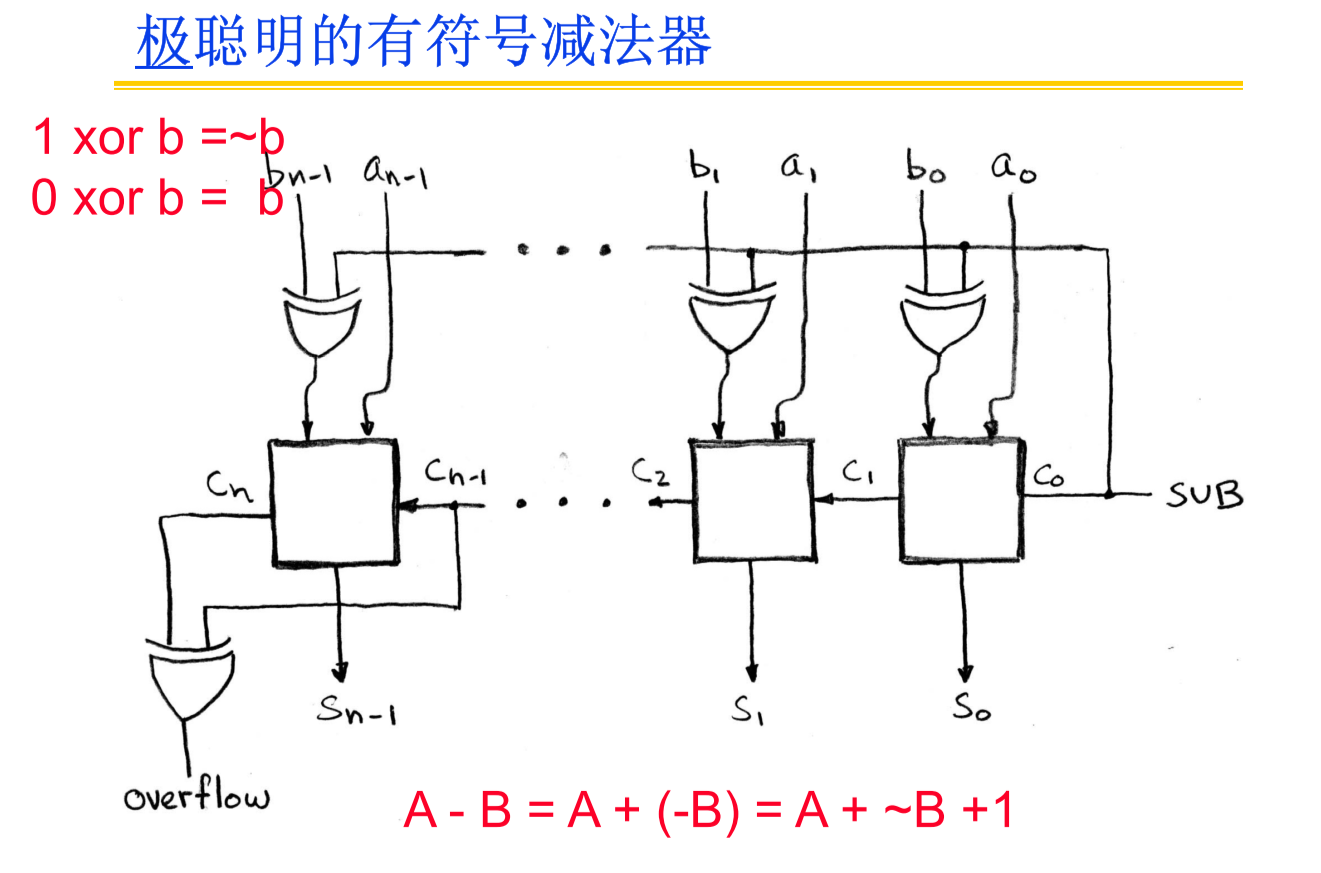

减法器实际上只需要在加法器上做一点点改进就好

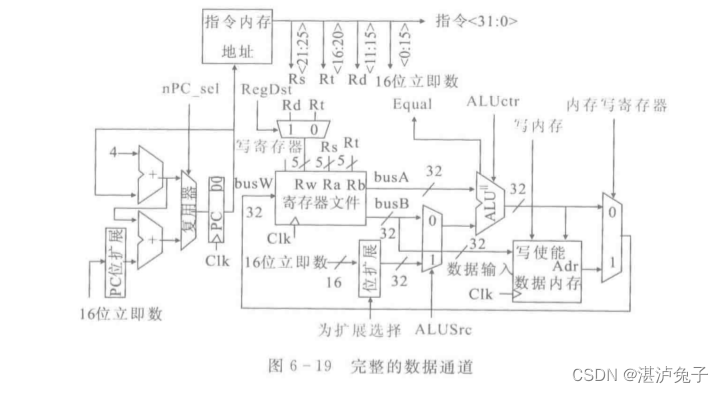

数据通道+控制通道

数据通道分为五步

- 取指

- 从内存中取出32位指令;PC=PC+4

- 指令译码

- 读opcode确定类型;分段;取出相关数据

- ALU

- 实际计算

- 内存访问

- 只有lw、sw此阶段工作;利用cache加快访问

- 写寄存器

需要在脑海里能够画出下面这个完整版的数据通道

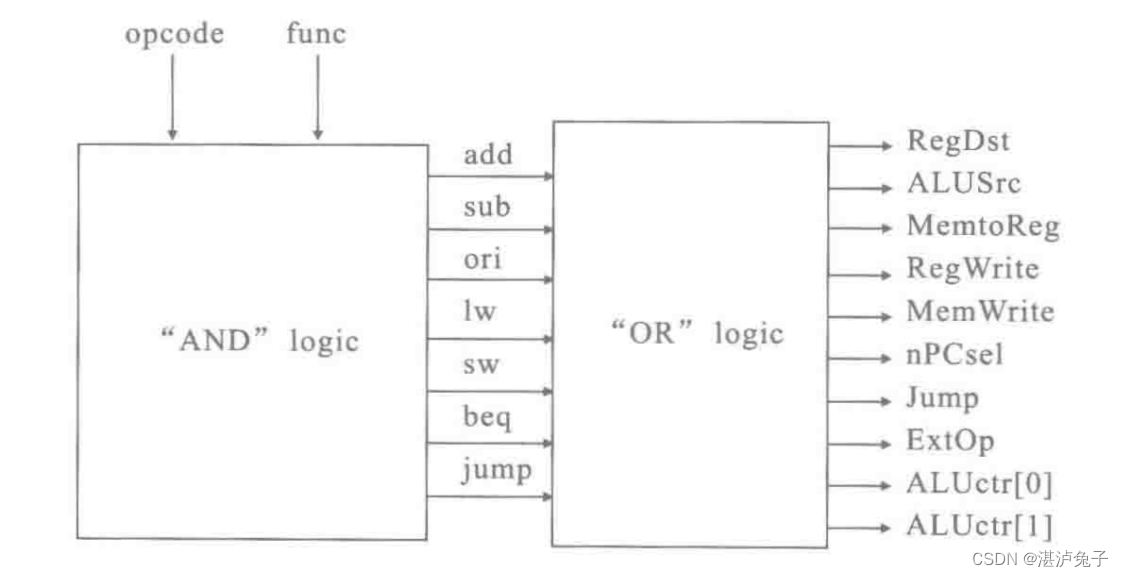

控制信号的设计,其实就是opcode与funct做and运算,得到一串二进制数,这串二进制数做or运算得到所需的信号

流水线改进性能

延迟不变;增加吞吐量

结构困境

硬件不支持某些组合

- 内存同时被访问

- 设计两个内存:一个指令内存一个数据内存

- 建立两个一级缓存

- 寄存器同时被读写

- 前半段只写;后半段只读

- 构建新的reg寄存器支持同时读写

控制困境

要等分支语句的判断出来后才能进行下一步

- 阻塞no-op消耗三个时钟周期

- 优化1:插入特殊分支比较器,在第二阶段解码得出分支立即决策更新PC

- 优化2:重新定义分支;(无论是否分支,分支判断语句下一条总被执行,叫做分支延时槽Branch-Delay slot

- 也就是将不被分支影响的指令放到分支语句后执行;重新排列汇编语句执行顺序

数据困境

后方指令依赖前面指令的结果

- 前馈解决

- 添加额外硬件从ALU的计算结果中直接取出后项要用的数据

- 无法解决就阻塞+前馈

- 硬件阻塞

- 可以单独插入一个bubble在两阶段之间

- nop阻塞

- 直接插入一个nop指令什么也不做

- load之后的指令叫load delay slot

- 硬件阻塞

Cache高速缓存

利用时间局部性和空间局部性

Cache是主存的子集的一个拷贝

Cache与内存间传输数据的单位——块block

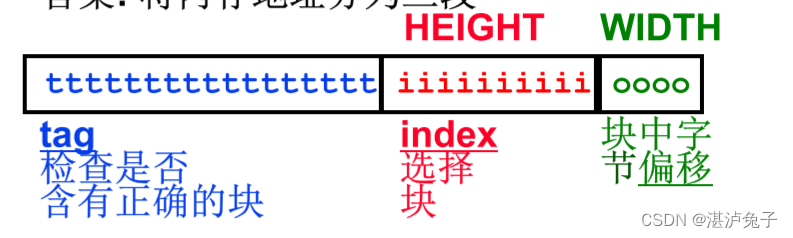

如上图,内存地址被划分为三块tag index offset

offset长度根据(能表示一个块包含的字节数来决定的位数)

index长度等于(能表示(缓存大小÷一行缓存的大小)这个的位数)

tag = 地址位数-offset和index的位数

访问cache有三种情况

- 命中

- 未命中

- 未命中且替换

访问cache有这样三步

- 看index确认cache行数

- 看tag确认是否是正确的行

- 看offset访问内容

- 如果2不满足就替换

内存读写

更新内存的方法

-

写内存Write Through

- 同时写内存和cache

-

写回WriteBack

- 只写cache,替换内存中的字为dirty;当该块缓存被替换时写入内存

最小化平均访问时间AMAT(Average Memory Access Time)

AMAT= H i t T i m e + M i s s P e n a l t y × M i s s R a t e HitTime+MissPenalty×MissRate HitTime+MissPenalty×MissRate

块替换策略,常用LRU

2582

2582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?