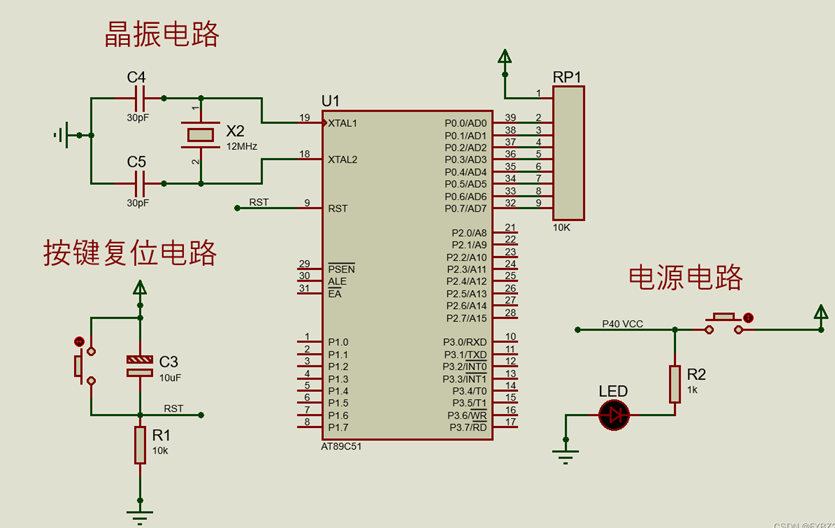

AT89C51是经典的51系列单片机,采用40引脚DIP封装,各引脚功能分类说明如下:

一、电源与时钟引脚

- VCC(40脚):+5V电源输入。

- GND(20脚):接地。

- XTAL1(19脚):接外部晶体和微调电容的一端。振荡电路的频率就是晶体的固有频率。若采用外部时钟电路,该引脚悬空。

- XTAL2(18脚):接外部晶体和微调电容的另一端。当采用外部时钟脉冲 由该引脚输入。

二、I/O端口引脚

1. P0口(32~39脚)

- P0.0 ~ P0.7(32~39脚):

- 通用I/O端口(需外接上拉电阻)。

- 外部存储器扩展模式:复用为低8位地址(A0-A7)和数据总线(D0-D7)。

2. P1口(1~8脚)

- P1.0 ~ P1.7(1~8脚):

纯通用I/O端口,无复用功能,内部带上拉电阻。

3. P2口(21~28脚)

- P2.0 ~ P2.7(21~28脚):

- 通用I/O端口。

- 外部存储器扩展模式:提供高8位地址(A8-A15)。

4. P3口(10~17脚)

- P3.0 ~ P3.7(10~17脚):

除通用I/O外,每个引脚有第二功能:- P3.0(10脚):RXD(串行数据接收)。

- P3.1(11脚):TXD(串行数据发送)。

- P3.2(12脚):INT0(外部中断0输入)。

- P3.3(13脚):INT1(外部中断1输入)。

- P3.4(14脚):T0(定时器0外部输入)。

- P3.5(15脚):T1(定时器1外部输入)。

- P3.6(16脚):WR(外部存储器写控制)。

- P3.7(17脚):RD(外部存储器读控制)。

三、控制信号引脚

1. RST(9脚):复位输入(高电平有效,持续至少2个机器周期)。

2. ALE/PROG(30脚):

- 正常模式:输出地址锁存允许信号(ALE),用于分离地址/数据总线。

- 编程模式:PROG(编程脉冲输入)。

3. PSEN(29脚):外部程序存储器使能信号(低电平有效)。

4. EA/VPP(31脚):

- EA=1:使用内部程序存储器。

- EA=0:强制从外部程序存储器启动。

- 编程模式:VPP(编程电压输入,通常12V)。

AT89C51最小系统原理图

8858

8858

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?