目录

预备知识

| 输入部件 | 鼠标、键盘、麦克风等 | |

| 输出部件 | 显示器,喇叭,打印机等 | |

| 存储器(用于存储数据的设备) | 易失性存储器(掉电丢失,速度快,成本高) | 寄存器 |

| 高速缓存(cache) | ||

| 内存(RAM) | ||

| 非易失性存储器(掉电不丢失,速度慢,容量大)(外部存储器) | 硬盘,机械硬盘,固态硬盘,光盘,U盘等 | |

| 运算器 | 算数、逻辑、位运算 | |

| 控制器 | 控制中心,控制整个 运行流程 | |

| 总线 | 数据的传输通道, 负责各个部件之间的数据传输 | 单总线模型( 结构简单 成本低 传输效率不高) |

| 多总线模型(各个部件 使用一条或多条独立的 总线 进行数据传递, 效率更高) | ||

ARM生态链:

ARM公司:设计了一种CPU架构——ARM架构,该架构的CPU功耗低 ,体积小,硬件结构简单,成本低,带动嵌入式发展;

ARM芯片公司:例如三星、飞思索尔、意法半导体STM32…

使用ARM架构:设计、生产芯片,使用芯片;

芯片应用公司:使用芯片 制作开发板,使用开发板完成特定应用;

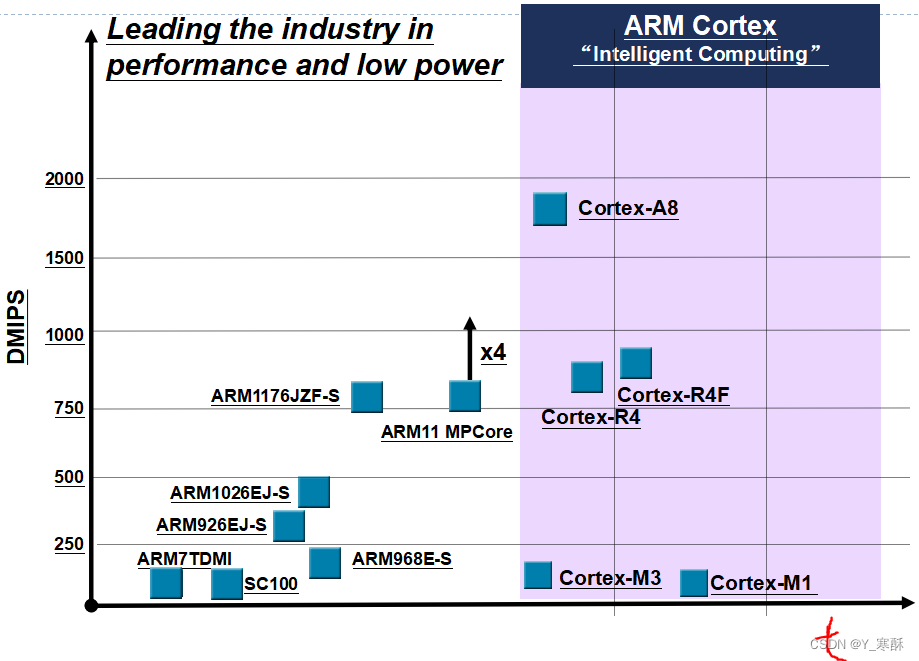

cortex系列:

cortex-A A8 A9 A53 高端高性能产品 ,图形图像 多用于多媒体应用

cortex-R R4 R4F 中端产品, 追求实时性 多用于工业控制

cortex-M M3 M1 M0 低端产品 ,单片机 多用于stm32

低速设备 ARM7 ARM9 ARM11 ...

ARM架构的发展:

ARMcpu:

其中 R0-R12 是 13个通用寄存器;

特殊功能寄存器:

R13 SP :栈指针寄存器 专门用于存储栈指针的 寄存器

R14 LR :链接寄存器 专门用于存储返回地址的

R15 PC :程序计数器

用于 记录 以及 控制 程序运行的位置 , 表示 下一条即将执行的(取址的)指令的位置, 程序的跳转由该寄存器完成。

spsr : 程序状态寄存器 备份寄存器 仅异常模式有 用于备份异常发生前的 cpsr寄存器 以便于在异常恢复时 恢复cpsr

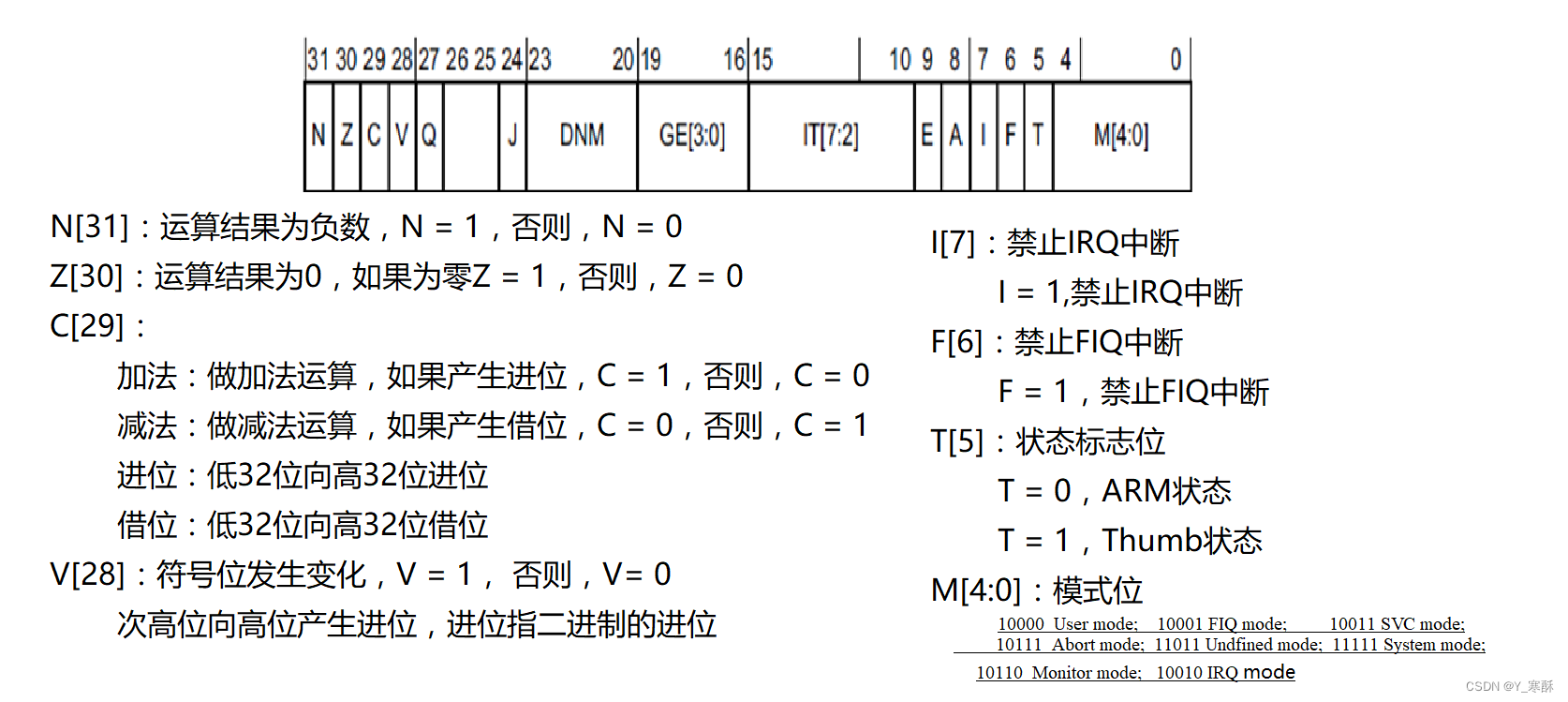

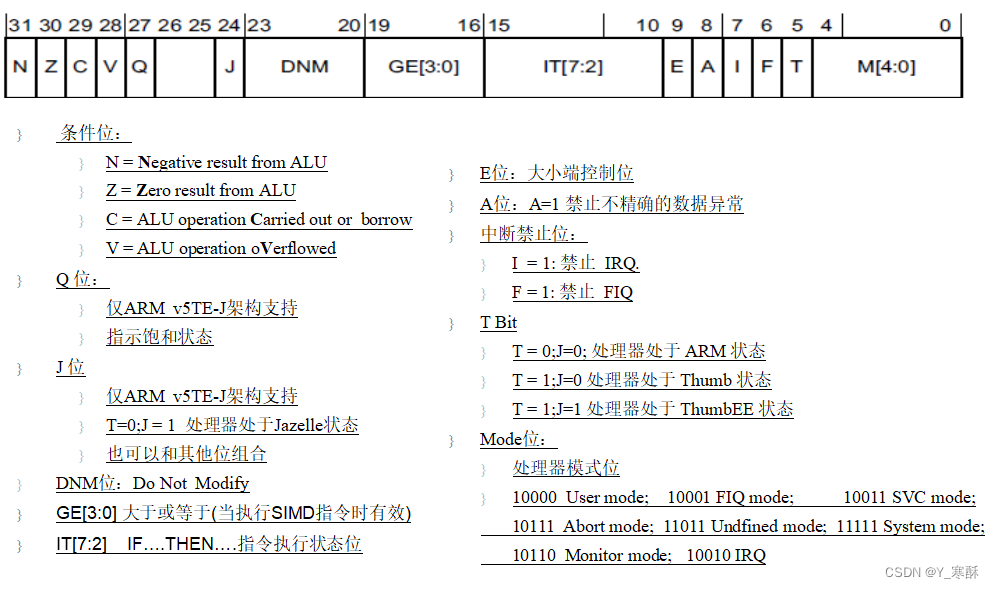

cpsr : 程序状态寄存器 ,用于存储 以及 控制 程序在运行过程中产生的 一些状态

寄存器详解:

nzcv: 条件位:

n: 运算结果为负数 则N = 1

z: 运算结果为 0 z = 1

c: 进位或借位标志

v: 符号位发生变化

i位和f位:

中断禁止位,中断表示能够暂时的暂停当前程序的执行,转而去处理突发的随机事件,而禁止中断是组织这样的动作或行为

T位: 状态标志位

0: ARM状态 该状态下 执行ARM指令集 4字节宽度

1: thumb状态 该状态下 执行thumb指令集 2字节宽度

[0-4] 模式位

10000 user模式 用户模式 用户的应用程序 10001 fiq模式 快速中断模式 紧急的硬件中断 10011 svc模式 管理员模式 操作系统 运行在该模式 10111 abort模式 终止模式 出现内存或数据 异常 11011 undefined模式 未定义指令模式 出现一个不识别的指令 11111 system模式 系统模式 操作系统 使用 10010 irq模式 中断模式 当硬件出现中断事件需要打断CPU 10110 monitor模式 安全模式 cortex-A架构有使用

ARMcpu 的模式: 7 +1 种模式(最后一个在cortex-A架构有使用),每一种模式 都有一套 寄存器 R0-R15 CPSR SPSR

模式分:

特权模式 除usr模式外的其它模式

异常模式: 除sys模式外

非异常模式: sys模式

非特权模式 usr

其中,异常模式指发生了 某种特定情况(异常) 才会进入的模式

注意:

1.usr模式与 SYS模式 共用一套寄存器 R0-R15 CPSR 没有spsr

2.异常模式的 R13(SP) R14(LR) SPSR 都是独立的

隔离异常模式 :其各个模式的栈区独立 ;目的:为了安全。

SPSR:备份异常发生前的cpsr寄存器

总结:

ARMCPU 一共有 多少个寄存器?

答:37+3个

一共有多少个模式?

答:7+1 8种模式

一共有多少状态?

答:2种状态 ARM状态/thumb状态

关于异常的总结

| 异常名 | 对应的模式 | 对应入口地址 |

| 复位异常 | svc | 0x0000 0000 |

| 未定义指令异常 | undefined模式 | 0x0000 0004 |

| 软中断异常(swi) | svc | 0x0000 0008 |

| 指令预取异常 | abort模式 (虚拟内存) | 0x0000 000c |

| 数据异常 | abort模式 (a / 0 ) | 0x0000 0010 |

| (该位置保留) | 0x0000 0014 | |

| 中断异常 | irq模式 | 0x0000 0018 |

| 快速中断异常 | fiq模式 | 0x0000 001c |

异常处理流程:

硬件处理: 当触发异常时,CPU自动执行的动作,不需要软件参与

1 备份 cpsr 到 对应模式 的spsr

2 设置适当的 CPSR 位

(1) 设置CPU为ARM状态

(2) 设置模式位 为对应的模式

(3) 禁止中断, 若有必要 高于中断优先级的异常

3 保存 pc-4 到 对应模式的 lr中

4 设置PC 为 对应异常的 入口地址 称:异常向量表

软件处理: 处理异常本身

1) 保存现场 将公有寄存器 入栈保存

2) 处理异常

3) 恢复现场 将公有寄存器 弹栈恢复 恢复cpsr 恢复LR到pc

异常优先级:

1、Reset

2、Data Abort

3、FIQ

4、IRQ

5、Prefetch Abort

6、SWI

7、Undefined instruction

fiq 快速中断 与irq中断

问 fiq 为什么比irq快?

1) fiq 独立寄存器多 入栈保存的公有寄存器少

2) fiq 优先级高于irq

3) fiq 异常入口 位于异常向量表的最后, 不用跳转直接处理异常

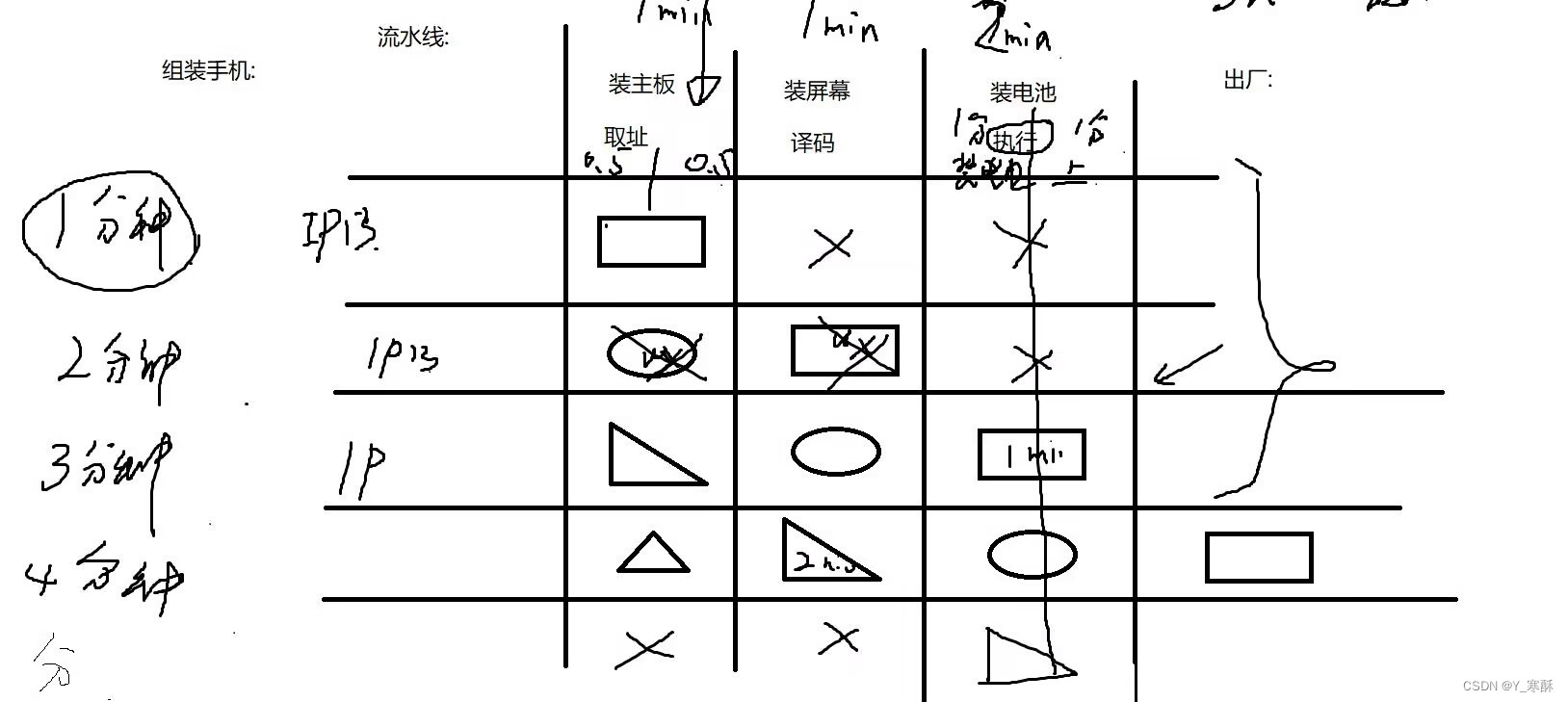

流水线

为了提高程序执行效率, 通过流水线的方式 实现一条指令 至少有3个动作:

取址: 从内存中 读取指令

译码: 解锁指令中需要的寄存器

执行: 指令执行

多级流水线:

ARM7 三级流水线

ARM9 五级流水线

ARM10/ARM11 七级流水线

cortex-A9 13级流水线

流水线的建立 需要时间,所以不是流水线越多越好

2323

2323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?