(1) 在Windows资源管理器中,新建一个子目录。

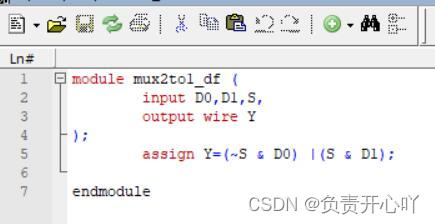

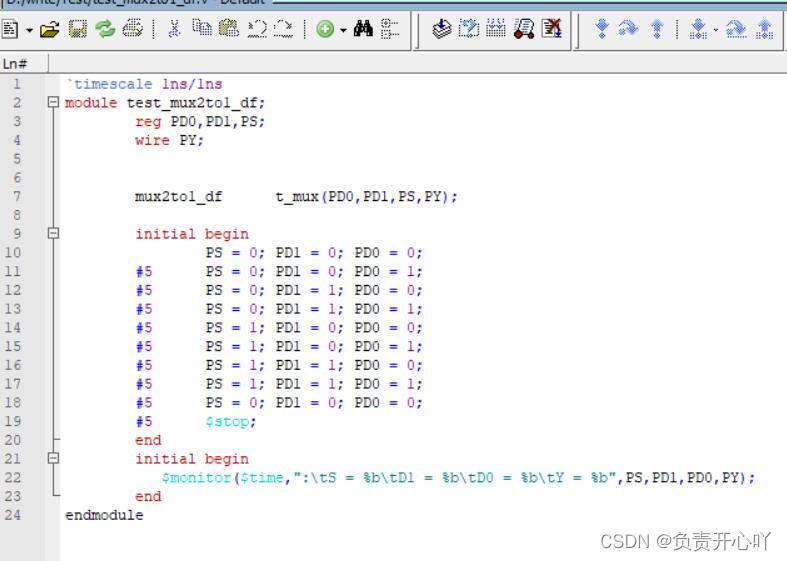

(2) 打开一个文本编辑器【本文使用记事本,需注意文本打开方式,否则Modelsim中无法编译,如图一所示】,输入设计块和激励块源代码,并将它们保存在新建的子目录中,文件名分别为mux2to1_df.v和test_mux2to1_df.v如图二和图三所示:

-

图一:文本打开方式 *  * 图二:设计块代码  图三:激励块代码 ❤注意注意注意(重要的事情说三遍,第一行代码中的“`”是英文状态下电脑左上角Esc下面的一瞥)

(3) 打开Modelsim软件,创建一个新的工程项目(Test_mux2to1.mpf),添加已经保在的源文件(mux2to1_df.v和test_mux2to1_df.v)。

(4) 在Project子窗口中,编译所有的源文件。如果编译成功,则代码文件Status栏显示为绿色的“✓”。如果编译出错,则会给出相关错误信息,修改代码,然后再重新编译,直到没有错误编译。

(5) 将设计载人仿真器,开始仿真。编译成功之后,仿真器通过调用 Verilog HDL 的顶层模块将设计载人到仿真器中,弹出与仿真相关的子窗口,且设置仿真时间从0时刻开始。

(6) 将需要观察的信号添加到 Wave 子窗口中。

(7) 执行仿真命令,得到如图四所示的输人、输出波形;同时,还得到图五以文本方式显示的仿真结果。可见,在0~20 ns 期间,由于 PS =0,所以输出 PY 与输人PD0相同;在20~40 ns 期间, PS =1,故输出 PY 与输人PD1相同。表明该设计块描述的逻辑功能是正确的。

(8) 结束仿真,退出 ModelSim 仿真器。

图四:仿真输出波形

图五:以文本方式显示的仿真结果

【仅供参考,不会的地方建议去B站学习学习,因为本人也在学习呢,怕误人子弟哈哈哈】

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?