以下内容为我电路与数字逻辑实验的实验报告内容。

实验部分采用的是logisim实现

本实验因时间问题做的比较仓促,有许多不足之处,还请谅解。

想要完整代码的可以在我的博客资源进行下载

电路与数字逻辑课程设计-电子钟-单片机文档类资源-CSDN文库

一、课程设计目的

设计一个电子钟功能要求如下:

(1)二十四/十二制小时、分、秒计时。采用七段数码管显示,由七段字形译码器驱动;

(2)小时、分钟可以校正(顺时针校正);

(3)使用小时及分钟完成定时闹钟功能,到达指定时间几时几分后,led灯闪烁1分。

(4)完成电路板焊接

二、课程设计环境

Logisim软件、PCB电路板、焊接工具、万用电表

三、课程设计步骤/过程

1.先使用Logisim软件画出电路图。

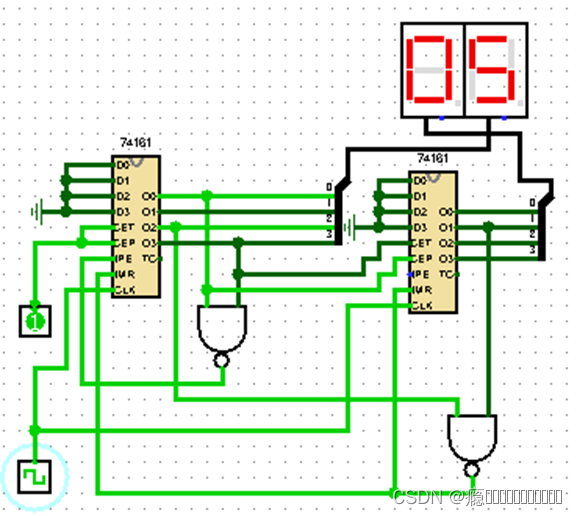

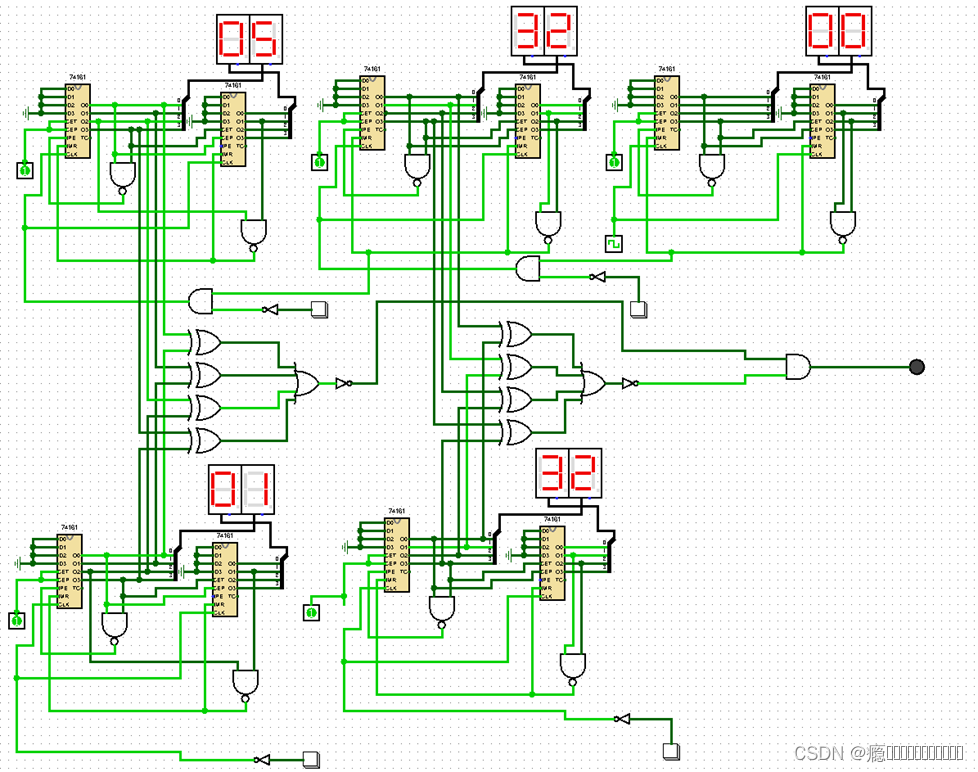

(1)设计出60进制的计数器。用一个74161对个位进行计数,当输入9个计数脉冲计数到9(8421码为1001)时,将Q0和Q3进行与非得出结果送给,此时=0,当第十个计数脉冲到达时,将D3D2D1D0=0000置入计数器,从而使个位数复位。控制十位数的74161计数器P和T端口分别连接个位计数器的Q0和Q3,CP端接个位数的74161计数器Q0和Q3与非后的结果,当输入9个计数脉冲计数到9(8421码为1001)时,P=Q0=1(P由0变成1),T=Q3=1(P由0变成1),在第十个计数脉冲到达时,Q0和Q3与非的结果发生变化进而给十位数的74161的CP端一个脉冲,此时P=T=1,计数器开始工作,十位数加1。然后将十位数上的74161计数的结果Q2和Q1进行与非,同时连接十位数和个位数74161的端,当计数到60的时候,=0对计数器清零,使Q3Q2Q1Q0=0000,实现60进制计数。

- 设计出24进制的计数器。在60进制计数器的基础上将各位数上的74161计数的结果Q2和十位数上的74161计数的结果Q1进行与非,同时连接十位数和个位数74161的端,当计数到24的时候,=0对计数器清零,使Q3Q2Q1Q0=0000,实现24进制计数。

- 设置开关校正分钟和时钟。准备一个开关,将开关给的脉冲信号与秒钟给的进位脉冲信号进行与输出,输出结果接分钟计数器的CP脉冲端,按一下给计数器一个脉冲信号或者秒钟进位给的脉冲信号,使得计数器加一。校正时钟的方式与秒钟一致。

- 设置闹钟。将分钟和时钟的输出信号逐个进行与非操作,得出的结果逐个进行或操作,直至得出最终结果,当结果为0时,闹钟响铃一分钟,当结果为1时,闹钟不响。

- 最后进行组合电路,得到电子时钟。

- 再使用焊接工具在PCB电路板进行电路焊接。

- 最后对焊接完的电路板进行调整。

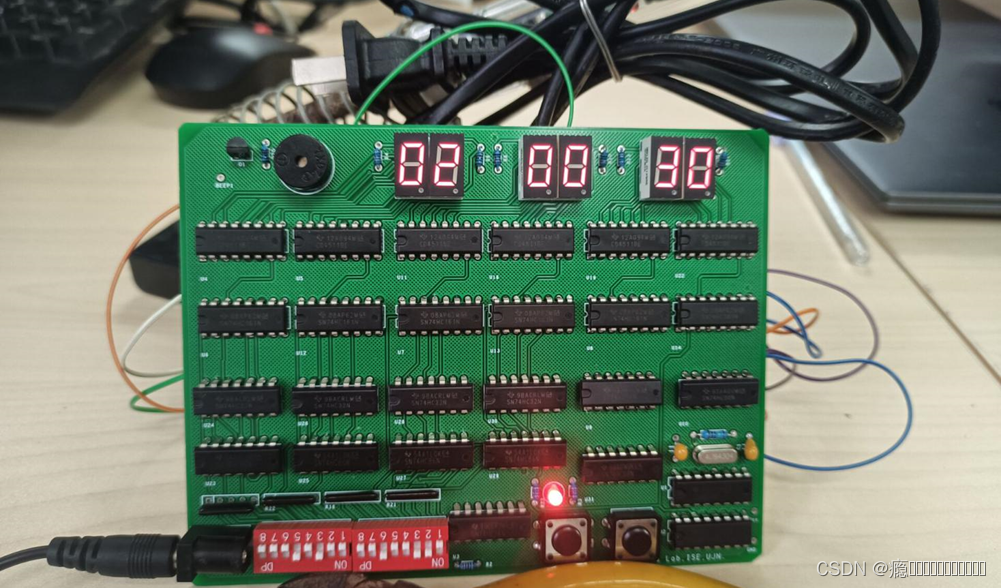

四 课程设计结果

在刚刚开机接通电源的时候,时钟,分钟和秒钟为任意值,对其进行调整,对分钟和时钟进行校正。先进行正常计时,当把时间校正为23:59:00,当秒针计数到60的时候,计数变成00:00:00,进位没有问题。再把时间设置为当前时间,闹钟响铃一分钟,运行结果无问题。

五、课程设计分析及反馈

电路与数字逻辑是本学期课程中唯一一门有课程设计的,要求设计一个电子时钟,经过我的认真摸索,设计电路到焊接电路再到最后的调整,我对计数器、译码器和与非门等有了更充分的了解,对课本上的知识有了进一步的掌握。

在完成课程设计之前,从刚开始一头雾水到有一点点头绪,再到最后的设计成功,从中获得了很多,没有耕耘,哪来的收获的喜悦,有付出才会有回报。

7155

7155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?